# **JAIST Repository**

https://dspace.jaist.ac.jp/

| Title        | Verification of automotive operating systems for multi-core processors |  |

|--------------|------------------------------------------------------------------------|--|

| Author(s)    | マリーヌアン、パッターウット                                                         |  |

| Citation     |                                                                        |  |

| Issue Date   | 2015-09                                                                |  |

| Туре         | Thesis or Dissertation                                                 |  |

| Text version | author                                                                 |  |

| URL          | http://hdl.handle.net/10119/12933                                      |  |

| Rights       |                                                                        |  |

| Description  | Supervisor:Toshiaki Aoki, School of Information<br>Science, Master     |  |

# Verification of automotive operating systems for multi-core processors

Pattaravut Maleehuan

School of Information Science Japan Advanced Institute of Science and Technology September, 2015

# Master's Thesis

# Verification of automotive operating systems for multi-core processors

1310205 Pattaravut Maleehuan

Supervisor: Toshiaki Aoki

Main Examiner: Toshiaki Aoki

Examiners: Masato Suzuki

Kazuhiro Ogata

School of Information Science Japan Advanced Institute of Science and Technology

August, 2015 (submitted)

#### Abstract

Currently, the automotive systems provide many functionalities for automobile. Although those functionalities are able to support our lives, the violation of those functionalities may be serious issue that we have to concern. Obviously, the automotive systems require high-reliability of the system to ensure safeness of our lives. In this research, we specifically focus on *operating systems* of automotive systems. The operating system is the basis component which provide services to serve application software. Thus, the correctness of the operating systems is the serious condition to correctly implement the operating system kernel.

In addition, since the demand of usage is increasing, the *multi-core processors* are adopt in the automotive systems for performance improving. The multi-core system is the system that have multi-processors with shared-memory. In the shared-memory systems, according to [Gha95], the results of programs might be not same as the *sequential execution*, which is the execution which follow the program order specified by programs. As programmer's point-of-view, these results maybe unexpected results. These results are affected by *memory consistency models* which are define the behaviors of memory in shared-memory systems.

In the shared-memory systems, the systems allow each processor to access the memory locations simultaneously. Moreover, each processor are able to issue the memory accesses out-of-order because of optimization mechanisms. Since each processor is independent to each other, the access order of memory access might be different. Hence, the memory maybe not consistence among processors. The specifications of memory consistency models ensure the execution order of memory accessing to shared-memory locations. Unfortunately, these behaviors are not appeared explicitly. It might be difficult to consider the behaviors of program execution.

Our research aims to verify the automotive operating systems for multi-core systems. Since the behaviors of program execution are not appeared explicitly, the verification might be difficult. In addition, the behaviors of program executions are affected by the hardware architecture. That means we cannot verify the programs on multi-core systems by themselves. Hence, this research will provide the verification which take the hardware behaviors into account for ensure the correctness. Moreover, the verification of the whole operating systems will be difficult because operating system is a complex system. Therefore, the scope of this research considers only multiprocessor programs to provide the verification for multi-core systems.

In software development, there are many approaches to ensure the correctness of the software. Due to the automotive operating systems require high-reliability, the *formal verification* is adopt in this research. Since the behaviors of program execution in multi-core systems might be complicated, we apply the *theorem proving* approach instead of model checking. Therefore, due to the behaviors of hardware is significant issue, this research provides the formal model which represent such behaviors. Then, the verification method is proposed to provide the proofs based on our formal model.

# Acknowledgment

First of all, I would like to express my sincere gratitude to my supervisor, Associate Professor Toshiaki Aoki, for his guidance, support, and encouragement. Since I was a student at Chulalongkorn University in Thailand, he gave opportunity to interview for studying abroad at JAIST. In addition, he also assisted me in advanced to get to Japanese Government (Monbukagakusho) Scholarship. As for my academic life in JAIST, every time I have problems about the research or stuck on some issues, he always give a time to discuss and give guidance to solve those problems. In addition, as my presentation skills are not good, he always fix my mistakes by exploring the issues that need to be explained, then give examples and guidance. His guidance and comments usually are helpful for me to improve my skills.

Beside my supervisor, Associate Professor Toshiaki Aoki, I would like to show gratitude to Assistance Professor Yuki Chiba. He usually help me in advance to do the research and my life in Laboratory. Due to my research uses many mathematics definitions, he usually suggest the correct mathematics definition in advanced. Every times I discuss with him, he usually check it in detail, and give the comments to improve and correct my works.

Finally, I also would like to give my special thank to my friends and seniors in JAIST for their helps, suggestions and encouragements during live in JAIST. I also need to give my thanks to Thais friends, whose usually help and make me have a great time in Japan.

# Contents

| 1        | Intr | Introduction                          |                                                         |          |  |  |  |  |  |  |

|----------|------|---------------------------------------|---------------------------------------------------------|----------|--|--|--|--|--|--|

|          | 1.1  | Proble                                | ems                                                     | 2        |  |  |  |  |  |  |

|          | 1.2  | Object                                | tive                                                    | 3        |  |  |  |  |  |  |

|          | 1.3  | Appro                                 | ach                                                     | 3        |  |  |  |  |  |  |

|          | 1.4  | Organ                                 | ization                                                 | 4        |  |  |  |  |  |  |

| <b>2</b> | Mu   | Multi-core systems and Verification 5 |                                                         |          |  |  |  |  |  |  |

|          | 2.1  | Multi-                                | core systems                                            | 5        |  |  |  |  |  |  |

|          |      | 2.1.1                                 | Terminology                                             | 6        |  |  |  |  |  |  |

|          |      | 2.1.2                                 | Behaviors for performing programs on multi-core systems | 7        |  |  |  |  |  |  |

|          |      | 2.1.3                                 | Hardware optimization                                   | 9        |  |  |  |  |  |  |

|          |      | 2.1.4                                 | Memory consistency models                               | 11       |  |  |  |  |  |  |

|          | 2.2  | Forma                                 | l Verification                                          | 15       |  |  |  |  |  |  |

| 3        | For  | malizat                               | tion for multi-core systems 1                           | .6       |  |  |  |  |  |  |

| J        | 3.1  |                                       | v                                                       | 16       |  |  |  |  |  |  |

|          | 0.1  | 3.1.1                                 | v                                                       | 17       |  |  |  |  |  |  |

|          |      | 3.1.2                                 |                                                         | 17       |  |  |  |  |  |  |

|          |      | 3.1.3                                 |                                                         | 18       |  |  |  |  |  |  |

|          |      | 3.1.4                                 | 1                                                       | 21       |  |  |  |  |  |  |

|          |      | 3.1.5                                 |                                                         | 21       |  |  |  |  |  |  |

|          | 3.2  |                                       |                                                         | 25<br>25 |  |  |  |  |  |  |

|          | 5.2  | 3.2.1                                 |                                                         | 25<br>25 |  |  |  |  |  |  |

|          |      | 3.2.1                                 |                                                         | 26<br>26 |  |  |  |  |  |  |

|          |      | 3.2.2                                 | v                                                       | 20<br>32 |  |  |  |  |  |  |

|          |      | 3.2.4                                 |                                                         | 39       |  |  |  |  |  |  |

|          |      | 3.2.4 $3.2.5$                         | y y                                                     | 14       |  |  |  |  |  |  |

|          | 3.3  |                                       |                                                         | 19       |  |  |  |  |  |  |

|          | 0.0  | Dampi                                 | c executions based on our semantics                     | ΕJ       |  |  |  |  |  |  |

| 4        |      |                                       | v                                                       | 53       |  |  |  |  |  |  |

|          | 4.1  |                                       | 1 0                                                     | 53       |  |  |  |  |  |  |

|          | 4.2  |                                       |                                                         | 55       |  |  |  |  |  |  |

|          |      | 4.2.1                                 | <u> </u>                                                | 55       |  |  |  |  |  |  |

|          |      | 422                                   | Define the sets of states                               | 56       |  |  |  |  |  |  |

|    |                                  | 4.2.3 Provide the induction proofs                              | 56                   |

|----|----------------------------------|-----------------------------------------------------------------|----------------------|

| 5  | <b>A c</b> 5.1 5.2               | ase study: a mutex lock verification  Apply verification method |                      |

| 6  | Eva 6.1 6.2                      | Iuation         Evaluation of our formal model                  |                      |

| 7  | Rela<br>7.1<br>7.2<br>7.3<br>7.4 | ated works  OS Verification                                     | 69<br>69             |

| 8  | Com<br>8.1<br>8.2                | Discussion                                                      | 71<br>71<br>72<br>72 |

| Bi | blioº                            | rraphy                                                          | 73                   |

# List of Figures

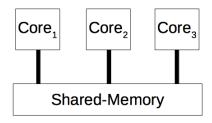

| Sample programs on different cores                       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General shared-memory systems                            | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Sample for shared-memory systems                         | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Example for bypassing read access                        | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Representation for the sequential consistency (SC) model | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Sample programs                                          | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Representation for the total store ordering (TSO) model  | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Example programs for the TSO model                       | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| The partial store ordering (PSO) model                   | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Abstract model for multi-core system                     | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                          | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                          | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A sample program for considering execution               | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A sample program                                         | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                          | General shared-memory systems Simple instructions Sample for shared-memory systems Example for bypassing read access Representation for the sequential consistency (SC) model. Sample programs Representation for the total store ordering (TSO) model Example programs for the TSO model The partial store ordering (PSO) model  Abstract model for multi-core system Example of out-of-order updates Example of read-modified-write requirement General model for shared-memory |

# Chapter 1

# Introduction

Currently, computer systems are attached to electronic systems around us. This research is interested in *automotive systems* which relate with our lives, such as automobile. In the *automobile systems*, computer systems are adopt to control many parts inside the automobiles, such as ABS braking systems. In addition, the most systems of automotive systems relate to our lives. Due to the fact that some violations of the systems may risk our lives, , we should ensure that the automotive systems is working correctly. In the automotive systems, *automotive operating systems* are the basis components which provide services for application software to control the hardware architecture. Hence, *automotive operating systems* are significant components which we focus in this research.

To improve the performance of the systems, the multi-cores systems are used in the modern automotive systems. In the multi-core systems, there are numerous optimization techniques to reduce the *memory latency*, such as bypass the read accesses. However, such techniques will change the order of executions in the systems. Even if the order of executions is changed, uniprocessor systems<sup>1</sup> are able to keep the correct results follow the program orders<sup>2</sup> Due to the fact that multi-core system is multiprocessors system with shared-memory, each core are able to read/write the shared-memory simultaneously. In addition, the order of updates, the results of write accesses to shared-memory, maybe appeared to each core independently in shared-memory systems. To keep *consistency* of the orders among cores, such optimization techniques have to restrict some behaviors in the hardware. So, we may loose the performance of optimization techniques. However, modern processor architectures assume that some executions of programs are acceptable. Hence, there are memory consistency models, or memory models, which allow some outof-order executions to be happened for improving the performance of the models. Nevertheless, due to some executions may produce unexpected results from the programs, ensuring the correctness of the programs for multi-core systems becomes complex.

In software development, there are many techniques to confirm the correctness of the programs, such as providing test cases. Nevertheless, the automotive systems need high-reliability of the systems. Hence, in this research, formal verification approach is proper

$<sup>^{1}\</sup>mathrm{A}$  computer system that has a single CPU

<sup>&</sup>lt;sup>2</sup>The order of instructions that appear in the program

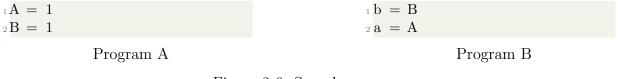

Figure 1-1: Sample programs on different cores

to ensure the correctness of the systems. Because the formal verification approaches offer rigorous approaches for the verification.

Since the operating systems are close to hardware architecture. Most of implementations are usually implemented by mixing assembly and c languages. As we said before, multi-core systems are able to allow out-of-order executions of memory accesses. Nevertheless, programmers usually assume that the executions will be sequential executions. Many program verification methods, such as Hoare logic, consider the instructions will be executed as atomic instructions in a sequential way. Therefore, unexpected results might be happened in the multi-core systems.

# 1.1 Problems

As we mention before, the hardware behaviors might change the order of executions of programs in multi-core systems. Even if we have ensured the programs, it's not enough to confirm programs are able to be performed correctly in multi-core systems. Firstly, let's consider the programs in figures 1-1. As for the programs, we define capital letters, A and B, as global memory locations and small letters, a and b, as private memory locations. Each program will be performed on different core on same multi-core systems. As verification of programs, we usually verify the programs in the interleaving ways as sequential executions. However, as we mention before, the order of executions will be changed due to hardware behaviors in multi-core systems. As the programmer's point of view, the results of (a, b) will never be (0, 0). Nevertheless, some multi-core systems allow operations 'b = B' and 'a = A' to be executed before 'B = 1' and 'A = 1'. Therefore, the results of (a, b) = (0, 0) might be possible in the multi-core systems. Obviously the verification of programs performed on multi-cores systems cannot be verified by themselves. Because behaviors of multi-core systems have not shown explicitly in the programs.

Due to the behaviors of multi-core systems can change the order of executions, the degree of non-determinism of multi-core systems will be greater than programs considered as *interleaved executions*. The verification becomes difficult because of degree of non-determinism. Since the behaviors of multi-core systems are significant issues to be concern, the verification should be able to ensure the correctness of programs with the behaviors of multi-core systems.

# 1.2 Objective

The objective of this research is to propose a verification method for ensure the correctness of automotive operating systems for multi-core systems. Since the operating systems are close to hardware and the behaviors of multi-core systems affect the execution of the programs, behaviors of multi-core systems are the most importance in the verification. Therefore, the hardware behaviors of multi-core systems will be taken into account. The proposed verification method also should able to ensure the correctness of the programs in multi-core systems.

In addition, since operating systems are the complex systems which contain a lot of functionalities to service the software application. The verification of the operating systems become difficult. As this research we focus on verification of programs on multicore systems, thus verification of programs which service the multi-core functionalities is enough to ensure the correctness of programs in multi-core systems. Because the out-of-order execution is the significant issue to be concerned when the programs are executed on different cores.

# 1.3 Approach

Since the operating systems usually implemented by mixing assembly with C languages. These languages offer different programming paradigms to write programs. In addition, assembly language is more close to the hardware which affect the execution order of programs. Moreover, considering the complied programs as assembly languages also avoid the compiler optimization which also change the program implementation. Therefore, this research will focus on assembly programs in the verification.

In order to propose a verification method for programs executed on multi-core systems, as we mention before, the behaviors of multi-core systems should be taken into account. Thus, the verification also need a *formal model* which represent the multi-core systems. The formal models should be an abstraction of multi-core systems and capable for verification of programs. In addition, the execution order of memory accesses in multi-core systems is influenced by *memory consistency models*. In the multi-core processors, there is a variation of memory consistency models which allow different behaviors of executions to be happened in the systems. Therefore, the memory consistency models are necessary issues to be formalized in the formal model.

Then, the verification method will be proposed to deal with programs executing on multi-core systems based on our formal model. The verification should be able to cover the executions of programs in the multi-core systems. As the executions of instructions will not be an atomic step and more hardware behaviors will be appeared in the formal model, the verification becomes more complex due to the degree of non-determinism. Thus the verification method should be capable for programs in our formal model which aren't executed as *sequential executions*.

# 1.4 Organization

In this thesis, the next chapter will explain the preliminaries for this research. Firstly, we will consider the behaviors of multi-core system. We specifically consider the behaviors of program executions which is necessary in verification. Then, we will explain about formal verification. The formal verification will be adopted to our research. In the verification, we specifically use the theorem proving for ensuring the correctness.

In chapter 3, we provide the formal model of our work for verification. The model that we have proposed captures the behaviors of program execution on multi-core processors. Since the optimization mechanisms inside multi-core systems change the order of execution, the formal model is provided to capture those behaviors in the verification. In the last section of this chapter, we show the sample of execution based on our formal model as an evidence to convince that our model can be used.

In chapter 4, we will adopt the proposed formal model in the verification. In that chapter, the method will cover the possible execution paths produced from our formal model. In addition, we also show the proofs as a case study in chapter 5 to show that our method can verify the programs executing on multi-core systems.

Since we have already proposed the formal model and verification method, those model a method will be evaluated in the chapter 6. Then, the chapter 8 will discuss about them and conclude the research.

# Chapter 2

# Multi-core systems and Verification

This section will explain about the underlying system behaviors that perform programs on multi-core systems. Normally, we know that the assembly instructions will be fetched to a processor and be executed in that processor. Behind an instruction execution, the processor uses *micro-operations* and *memory accesses* to execute the fetched instruction. That means a single instruction isn't appeared as atomic. In addition, there are many mechanisms to improve the performance of the systems. Such improving techniques will be used for reducing the *memory latency*. Some techniques allow the latter memory accesses to be executed before the earlier memory accesses. Hence improving techniques will affect the execution order of *memory access*. In the section 2.1 will explain the behaviors of multi-core systems which affect the executions of the programs in details.

In multi-core systems, memory accesses are used in programs which communicate via shared-memory. There are optimization mechanisms provided to reduce the *memory latency* of memory accesses. The optimization mechanisms will be in either *compiler optimization* or *hardware optimization*. In the compiler optimization, the compiler uses profile-guide optimization to reordering the assembly instructions. Anyway, in this research, we focus on hardware optimization mechanisms which affect the hardware behaviors. The section 2.1.3 will explain the behaviors of optimization mechanisms in detail. Moreover, the multi-core systems will have it's own memory consistency model which affects the order of executions of programs. That means the possible executions of the programs may not be as sequential executions. The section 2.1.4 will explain the behaviors of memory consistency models in details.

To ensure the correctness of the programs for multi-core systems, we choose *formal* verification approach. The section 2.2 explain the idea of *formal* verification, describes the existing approaches, and consider the related works which apply the formal verification to verify operating systems.

# 2.1 Multi-core systems

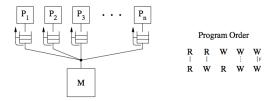

Normally, the multi-core systems are the *multiprocessor systems* with *shared-memory systems*. The program will be performed in a processor that belongs to one core and

Figure 2-1: General shared-memory systems

communicate each other by memory accesses via shared-memory as the figure 2-1. The programs usually are written in assembly code which belongs to Instruction Set Architecture (ISA) of processors, such as ARM processors. For each instruction appeared in the program will be fetched to the execution unit, or pipeline, inside a processor to be executed as micro-operations and memory accesses. Each of micro-operations and memory access will be issued from the processor to compute in the core or issue to outside the core for accessing the shared-memory. This section will consider the behaviors of executing programs on multi-core systems.

# 2.1.1 Terminology

Firstly, to describe the behaviors inside the multi-core systems, we would like to introduce overview of terminologies that will be appeared in this research.

A multi-core systems is the multiprocessor with shared-memory systems. It consists of a collection of cores, shared-memory locations, and a network, which connect cores and shared-memory locations. A **core** is a group of components that contains a processor, execution units, buffers, and private memory locations such as registers. The main role of the **processor** is to fetch the instructions from a program to be performed in the execution unit. A program is the sequence of instructions that will be performed in a processor. Each of programs will be placed on a core separately in multi-core systems. The fetched instructions are usually called **instances** to identify the execution in that time, because same instruction is able to fetched many times. The execution unit will issue a sequence of *micro-operations* and *memory accesses* for performing the fetch instructions. The micro-operations are the low-level instructions which transfer data among registers and buses inside a core. The **memory access** is the low-level instruction that access the memory location either update or read the value. There are situations that the processor try to perform a micro-operation and a memory access while earlier operations or accesses is not finished yet. The **buffers** will be used to handle such micro-operations or memory accesses which cannot be performed yet. The memory accesses which need to access the shared-memory locations will be issued to the *network* outside the core.

The **network** is an external bus that connect the cores and *shared-memory locations*. The memory accesses which access shared-memory locations might have a delay of memory latency to access the external memory locations. The modern processors usually have *caches* inside a core to reduce memory latency.

In the systems, we have information of **program order of instances** and **program**

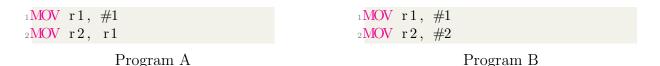

Figure 2-2: Simple instructions

order of micro-operations and memory accesses. These order is specified by the time that instances, micro-operations, or memory accesses are instantiated. These program orders are total orders in the it's own core. However they will be appeared as partial orders in the multi-core systems. Such program order will be used to consider about execution behaviors in the future, because memory consistency models will be generalized in formal model. Nevertheless, these information is not appeared in the hardware explicitly.

# 2.1.2 Behaviors for performing programs on multi-core systems

As the programs will be placed on each core separately, first we will consider the program executed in a one core. Then, the *memory accesses* which issued to the network will be considered later to interact with shared-memory locations.

# Performing instructions

In order to execute a program assigned to the core, a processor inside a core will fetch an instruction to the *execution unit*. The fetched instructions are considered as *instruction instances*. Even though such instances are instantiated from same instruction, the instances should be different to each other. The *program order* of instances is depend on the order of fetching instances from a programs. Obviously the program order of instances is a *partial order* among cores.

After an instruction is fetched, execution unit will issue *micro-operations* and *memory* accesses to perform an instance of such instruction. These micro-operations and memory accesses also have their *program order* to keep order of executions of instance's operations.

Moreover, fetching instruction is able to fetch the next instruction immediately if the registers which will be used by such instructions are available to use. Let's consider the programs in figure 2-2, In the  $Program\ A$ , we have to wait instruction at line 1 before fetching the next instruction because of dependency of register r1. Nevertheless, in the  $Program\ B$ , we are able to fetch the instruction at line 2 even if the instruction at line 1 is not finish yet. The fetched instructions will be placed on available  $execution\ units$ , as known as pipeline in modern processors.

### Read and write accesses and their buffers

Let's consider the memory accesses which issued from execution units. The accesses are either read accesses or write accesses to memory locations. Generally, accessing the memory always have a memory latency of memory operations. Due to memory latency, a processor have to be *stall* until the outstanding memory access is finished. Hence, the

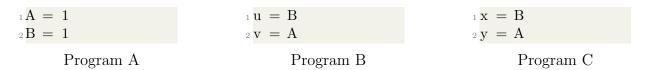

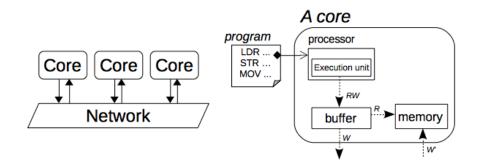

Figure 2-3: Sample for shared-memory systems

read and write buffers have been introduced to reduce memory latency. If there are any read or write accesses as the next memory accesses which independent from outstanding access, such read or write accesses are able to be issued from the buffers and performed immediately. Because such accesses will be perform in different locations which do not need to stall the processor. The access locations of memory accesses can be either private or shared memory locations.

# Atomic operations

In the hardware architecture, the instructions are not be appeared as atomic instructions. Each instruction described in assembly language is performed as *micro-operations* and *memory accesses*. However, such atomic instructions are necessary in the multi-core systems. The hardware also have mechanisms to service the instructions which require atomicity. Normally, atomicity behaviors will consist of read and write access which access the same location. The atomicity behaviors ensure that once the read access is executed, there is no any write access from another processors which access the same location can update the value before the atomic's write access. The such mechanism can be implemented in either processors or memory. In a processors, atomicity can be supported by controlling the cache coherency protocol. Once the atomicity is needed, the processor will request the exclusive owner of the locations. Then, the cache coherency protocol will lock that location until the write access is finished. In the related work [Gha95], they refer to such kind of operations as *read-modified-write operations*.

### Accessing shared-memory locations

Let's consider the memory accesses which access the memory locations. Once the read and write accesses are finished by accessing the caches, the caches also have mechanisms to maintain the coherency of locations among cores. Although the cache protocol is able to handle the coherency among cores, there are the execution order issues to be concerned. Due to each core is independently and the optimization mechanisms are able to change the order of execution, the order of updates might be different. In multi-core systems, there are memory consistency models which describe the behaviors of memory accesses for shared-memory systems. Such consistency models will affect the order of updates among cores. Let's consider the programs in figure 2-3, once the 'A = 1' and 'B = 1' are issued, some memory consistency models can allow programs B to read the value of 'A = 0' and 'B = 1', and program C can read the value of 'A = 1' and 'B = 0'. We can see that the order of updates is appeared to each core independently.

In the related work [AAS03], they propose the formal model for share-memory systems. That model also take the memory consistency models into account for capturing the behaviors of shared-memory. As for shared-memory systems, they have proposed *view-orders* to each core to describe the order appeared to the core in each step of executions. That approach also applicable to simulate the order which is appeared to each core independently.

# Fencing operations

Due to some systems allow out-of-order executions to be happened, such systems also provide fencing operations, or memory barrier, to enforce some parts of programs to be executed follow the program order. However, in each processor architecture also have different mechanisms of fencing operations. Fencing operations will separate the group of operation to be two groups. They usually define groups as past operations and future operations. For the future operations, each system is able to define it's group, such as consider only write operations to the same location as operations in past operation group. To control the order of executions, some systems put the fence operations into a write buffer to enforce the executions.

# 2.1.3 Hardware optimization

This section will explain the hardware optimization mechanisms that usually be used in the multi-core systems. However, some optimization mechanisms, such as lock-up free cached, are ignored in this research. Due to we need to abstract the behaviors of hardware for programs verification, the cache behaviors might not necessary to consider. If the cache components are taken into account, the cache coherency protocols also might be considered in details. Moreover, the effect of some mechanisms also lead to reordering of executions. Such reordering also is able to be simulated by buffers behaviors. In addition, to maintain the coherency, memory consistency models are also used to control the order of updates among cores. Therefore, as optimization mechanisms proposed in this section might be sufficient to verify the programs for multi-core systems.

#### Out-of-order issuing

In the fetching instruction, normally the instructions are fetched in order decided by a program counter. Sometimes the next instruction should be wait until the necessary registers are available, as described in section 2.1.2. Instead of waiting, this technique stores the instruction into reservation station, or instruction buffer. The reservation station will issue an instruction that it's required registers are available. That means this behaviors will allow out-of-order issuing of instructions. In some cases that the programs are executed in multi-core systems, this behavior is known by only it's own processor. Therefore, the unexpected results maybe produced.

Figure 2-4: Example for bypassing read access

# Non-blocking read access

In the execution units, the instruction will be performed as *micro-operations* and *memory accesses*. As for the read accesses, there are some situations that the read access cannot be performed immediately. The causes maybe *read miss* in caches or the memory locations is not available yet. Hence, this mechanisms have been introduced to skip such read accesses to perform next *micro-operation* or *memory access*. However this read access will be performed again once the value of the read is needed. This behavior is able to be realized by *read buffers*.

#### Bypassing read access

The write accesses normally are putted into write buffers. To issue the read access as the program order, the read operation usually have to wait until the previous write accesses already be issued from buffers. In this case, the processor should be stall itself before perform the next operations. To reduce the stalls, bypassing read access have been introduced. The read access can be performed immediately if and only if there are no write accesses that access to the same address as the read access. Hence, this behavior will cause that a read access may be executed before write accesses specified as earlier operations. In the same processor, this behavior will not produce unexpected results. Nevertheless, in the multi-core systems, the order of some write accesses and read accesses maybe significant order to be considered.

For example, let's consider the figure 2-4, we define 'A =1' and 'B=1' as write access, and the remaining are read accesses. Assume that the write access 'A=1' already executed in the shared-memory and 'B=1' is stored in the write buffers. In this case, the read access 'a = A' is able to read the value 'A = 1' from shared-memory immediately, even if the write access 'B = 1' is not executed yet. In this case, the result of (x, y) is (0, 1) can be happened in the multi-core systems.

### Read forwarding

This mechanism also reduces the stalls of that processor by immediately issue the read access if and only if there is a write access stored in write buffers which access the same memory locations as the read access. However, such return value should be the value from the last write access that appeared in the buffer. Although this mechanism can reduce the stalls in processors, some *hardware* are not allow this mechanism to be implemented due to it may provide some unexpected results.

# Non-FIFO read/write buffers

Generally, buffers usually act like queues which issue an entity in order as First-In-First-Out(FIFO). In some cases the earlier read or write accesses cannot be executed yet, because accessing memory location is not available. Moreover, In the case of *out-of-order issuing*, some accesses should be issued in the program order, but buffers might have earlier accesses which should be issued later. Hence, such accesses will be selected to be issued before the earlier accesses in the buffers.

# 2.1.4 Memory consistency models

Due to the fact that the execution order on multi-core systems is significant issue to verify the correctness of the programs, this section will explain about memory consistency models. Currently, there are many models have been proposed in the computer systems. In each systems also provide different hardware behaviors to keep the memory consistency among cores. Fortunately, there is a related work [Gha95] that generalize the memory consistency models to their framework. They provide constrains to consider valid executions on each model. So, such framework will be applied to formalize the multi-core systems in our work.

A memory consistency model, or memory model, is the model to describe how read and write access will be executed in the multiprocessor with shared-memory systems. Due to the order of read and write accesses are able to be changed, the memory consistency models are used to specify how it can be changed. As the programmer's point of views, the program should be executed follow the program order. Such behaviors that every executions are executed in order are called sequential consistency model. Relaxed models have been introduced to allow more optimization techniques can exploit the hardware architecture.

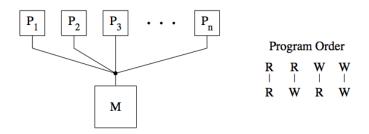

#### Framework for representing memory consistency models

First of all, to describe the memory consistency models, we need a framework to describe such model in a formal way. The framework that we use to describe the various of memory consistency models is adopt from [Gha95]. The framework provides conceptual abstract structure of shared-memory systems. The figure 2-5 show basic representation for sequential consistency model. In their conceptual system for sequential consistency consists of n processors sharing a single logical memory. In the conceptual systems, they show the concept in the programmers point-of-view. That means caches components is not appeared in this systems, even if it's used to implement in the practical systems.

The read and write accesses are treated as **R** and **W** for representing as read and write operations. A read operation is assumed to complete once the return value is bound. A write operation is assumed to complete once the shared-memory is updated to be new value. This framework also assume that read and write operations are issued from processor as *program order* though the completed order might be out-of-order. A atomic operation is represented as read-modified-write operation in this framework. The read-

Figure 2-5: Representation for the sequential consistency (SC) model.

modified-write operation is treated as both a read operation and a write operation. The most of memory consistency models require that there is no write operations appeared in execution order between the execution of atomic operation.

To represent memory consistency models, this framework proposes a set of constraints for the model. There are types of constraints for this framework. The first type of constraint on the execution of memory operations relates to program order. This is referred to as the program order requirement. Such requirements are figured in the rightside of the figure 2-5, they represent all pairs of read and write operations issued by same processor that follow one another in program order: read followed by a read, read followed by a write, write followed by a read, and write followed by a write. The lines provide constraints that the operations between the line should be maintained the program order in the execution order. The second type of constraint relates to the values returned by reads and is referred to as the value requirement. As for the sequential consistency, the value requirement is as follows: a read is required to return the value of the last write to the same location that completed in memory before the read completes. This requirement is referred as memory value requirement. Some of the memory consistency model have different value requirement that allows a processor to read the value of its own write before the write completes in memory. This latter requirement is affected by optimization mechanisms such as read forwarding that allows a read to return the value of a write from a write buffer. This requirement is referred as the buffer-and-memory value requirement. Other models may impose additional types of constraints to describe the models.

#### Sequential consistency model

According to framework in [Gha95], the conceptual systems as shown in figure 2-5 must obey the program order and memory value requirement described above to satisfy sequential consistency. An implementation obeys a given model if the result of any execution is the same as if the program was executed on the conceptual system. Therefore, a practical system need not satisfy the constraints imposed by conceptual systems (e.g. program order) as long as the results of its executions appear as if these constrains are maintained.

Let's consider the programs in figure 2-6, this example is taken from the related work [Gha95]. Assume that these programs are working together in a multi-core system, the capital letters, A and B, refer to the shared memory locations. the small letters, a and b, refer to private memory locations inside a core. Obviously these programs are working

Figure 2-6: Sample programs

Figure 2-7: Representation for the total store ordering (TSO) model

on different cores. As for sequential consistency models, the results of executions should follow the program order. That means some out-of-order executions also are allowed to be happen in the sequential consistency models if and only if the correct results is maintained. Hence the possible results of (a,b) from this programs are  $\{(0,0),(1,0),(1,1)\}$ . In the sequential consistency models, they allow operation 'A=1' and 'B=1' to be changed the order of executions. Nevertheless, if 'B=1' already executed, the model will enforce the operation 'A=1' to be executed before 'a=A'. Therefore, the result of (a,b) is (0,1) will not be happened in this model.

Since multi-core system has many hardware components working together. Moreover each core is working independently. To maintain the sequential consistency among cores, there is a work [Lam79] that describe how to correctly execute multiprocessor program on multiprocessor computer. However, there are another models which allow some results to be happened called *relaxed models*. These models assume that some results of the programs are acceptable and the significant order in the program should be maintained by programmers. Moreover, to control the significant order in some parts of programs, they provide fencing instructions to enforce the order of operations. This kind of models will be explained in the next section.

#### Relaxed models

The relaxed models are memory consistency models which allow the execution order of memory access to be changed. Each model will provide different constraints for its own conceptual system. Although the order of execution is allowed to be changed implicitly, they provide some mechanisms to restrict the significant program order to avoid the out-of-order execution of the order. We will give some sets of constraints for memory consistency models. Each of models will provides different requirements to maintain the behaviors of system.

The figure 2-7 represent the conceptual system for total store ordering. The systems

| <u>P1</u>     | <u>P2</u>                      |

|---------------|--------------------------------|

| a1: $A = 1$ ; | a2: B = 1;                     |

| b1: u = A;    | $b2: \mathbf{v} = \mathbf{B};$ |

| ct: $w = B$ : | c2: $X = A$ :                  |

Figure 2-8: Example programs for the TSO model

Figure 2-9: The partial store ordering (PSO) model

that use this model will be allow to finish the write operations out-of-program order. This conceptual systems is similar to figure 2-5 with a single logical memory shared by the processors. In contrast, this system provide a buffer buffer between each processor and the memory. Since we assume that operations will be issued in program order, they use the buffer to capture the behaviors of the operations are not necessary issued in the same order to memory. Hence, program order requirement places the constraints on the reordering that can tale place within the buffer. They also use the buffer to capture the behavior of models that allow a read to return the value of conflicting write in the buffer before the write is actually issued to the memory. The program order requirement for the TSO model is shown on the right side of figure 2-7. It similar to sequential consistency model, the only difference is in the program order from a write followed by a read is allowed to complete out-of-order.

Let's consider the example programs from [Gha95] in figure 2-8, under the sequential consistency model, the outcome (u,v,w,x) = (1,1,0,0) is disallowed. However, this outcome is possible under TSO model because read operations are allowed to bypass previous write operations, even if they are to the same location. Therefore the sequence (b1,b2,c1,c2,a1,a2) is a valid order for TSO model. Obviously the value requirement still requires b1 and b2 to return the values of a1 and a2, respectively, even though the reads occur earlier in the sequence than the writes.

The partial store ordering model(PSO) is an extension of the TSO models. Figure 2-9 shows the representation for this model. The conceptual system is same as the TSO model. The program order requirement is also similar, the difference is the order of a write followed by a write. The dotted line represent that the order of a write followed by a write should be maintained if and only if both writes access the same location. Moreover, the line with the description F represent that the order of a write follow by a write, which do not access to the same location, will be maintained if there is a fence instruction between them. Thus, the PSO model provides a fence instruction for maintaining the order. Programmers have to use such instructions for maintaining the order by themselves.

# 2.2 Formal Verification

In software development, there is a number of techniques to ensure the correctness of the software, such as *unit testing*. Since the software which is focus in this research is *automotive operating system*. The services of this operating systems will be used to control the behaviors of automotive systems which might relate to our lives. The errors of the systems also be significant issues which we should concern. Hence, to ensure the correctness of *automotive operating systems*, we need *rigorous approaches* to ensure the correctness of the systems. Therefore, *formal verification* is the appropriate approach for this research.

Formal verification is the approach to ensure the systems whether satisfy the given properties or not. Generally, it's used to prove or disprove the given properties by using formal methods. According to [But], "Formal Methods" refers to mathematically rigorous techniques and tools for the specification, design and verification of software and hardware systems. The phrase "mathematically rigorous" means that the specifications used in formal methods are well-formed statements in a mathematical logic and that the formal verifications are rigorous deductions in that logic (i.e. each step follows from a rule of inference and hence can be checked by a mechanical process).

There are approaches for formal verification. One approach is *model checking*, which we formalize the systems as the *mathematical model* and exploring all states and transitions in the model. The properties to be verified usually given in *temporal logic*. The great advantage of this techniques is fully automatically exploring all states of the models. However, It's doesn't scale for large models, the state explosion will be happened in the exploring process. Hence, there are many approaches to avoid such behaviors, such as providing boundaries for exploring.

Another one is *deductive verification*, which construct the collection of mathematical *proof obligations*, the truth of which imply conformance of the system to its specification. Then, provide proofs for these *proof obligations* to verify the correctness. Generally, we usually use either interactive theorem provers, automatic theorem provers, or satisfiability modulo theories (SMT) solvers. The disadvantage of this technique is that it requires user to understand the systems in detail, and how to convey the information for verification systems.

There are related works that also use formal verification to ensure the correctness of automotive operating systems. In the related work [Cho13], they use model checking techniques in this work. The formal model is translated from the kernel code of the operating systems. Thus, the model checking approach is adopted for this model. Then, the verification of this model is using the SPIN model checker. In this work, the safety properties are considered in the SPIN model checker to check the correctness of the operating system which already formalized as formal model.

There is another related work [KAE<sup>+</sup>14] that use *theorem provers*, which is used for *deductive verification*, to verify the correctness of it's operating systems. Since it has the advantage that it is not constrained to specific properties or finite, possible state spaces, unlike more automated methods of verification such as *static analysis* or *model checking*.

# Chapter 3

# Formalization for multi-core systems

This section will propose a formal model to represent multi-core systems. Since the behaviors of multi-core systems is necessary issue in verification, the systems should be formalized to verify the correctness of the programs for multi-core systems. In order to formalize the multi-core systems, the formal model should keep the essences of the multi-core system and sufficient to capture the behaviors of multi-core system. The first section will provide the details of target multi-core system which is focused in this research. The target system consists of components and behaviors which are sufficient for verifying programs on multi-core systems. The next section will propose our formal model based on operational semantics. Then, we give a sample execution of programs based on our formal model.

# 3.1 Target multi-core systems

First of all, to capture the essences of multi-core systems, let's consider the procedures to execute programs on multi-core systems. In the section 3.1.1 will proposed the abstract model of the target systems which represent multi-core systems. The model will capture only the components that sufficient for program verification. To execute programs on multi-core system, normally, each program will be assigned to each core. Then, a processor in the core will *fetch an instruction* from the assigned program. The fetched instruction will be performed by an execution unit. The details to performed each instruction will be explained in section 3.1.2.

Then, the execution unit will issue micro-operations and memory accesses to complete assigned instruction. We refer micro-operations and memory accesses as hardware operations in the target systems for the formal model. There is a variation of hardware operations to complete the instruction that provide semantics by Instruction set architecture. However, the target system captures only the operations which influence the execution order issue. The behaviors of hardware operation will be explained in section 3.1.3.

Next, we will consider memory operations which accesses the memory locations either shared-memory or private memory. In the practical systems, there are many components

Figure 3-1: Abstract model for multi-core system

to store data, such as cache. In addition, the address locations and arithmetic calculation are used in the low-level architecture. Since the formal model will keep only the essences of the systems, the unnecessary components and behaviors will be eliminated in the target systems.

Since memory consistency models are used for describing the behaviors of shared-memory. As memory operations which access the shared-memory, the order of executions should be controlled by memory consistency models. Thus, the section 3.1.5 will explain idea to adapt the constraints which are proposed by [Gha95].

# 3.1.1 Abstract model

The figure 3-1 represent the abstract model that represent the multi-core system in the target system. This model consists of a group of cores, and a network for communicating. As for shared-memory locations, these locations are separated and be attached to each core to capture the memory consistency of target system. Inside a core, It consists of a processor, buffers, reservation stations, an execution unit, and memory location. In target system, buffers is used for keeping the read/write operations. Memory locations in the core is used to represent both shared-memory location and private memory locations. The memory locations are also refer to a cache which can be appeared in the core. However, we did not model the cache separately to take the cache coherency protocol into account because cache coherency can be controlled by memory consistency which we focus in this research. As for reservation station, we use this component as instruction buffer for the core. The behaviors of this component will be explained in the followed section.

# 3.1.2 Fetching instruction

In order to execute assigned program in the core, the processor will fetch the instruction indicated by *program counter*, which is a register in the core. Once the instruction was fetched, such instruction will be placed into an available execution unit. Note that, in the modern processors, there is a pipeline which consists a collection of execution units. When the execution unit access the registers inside a core, sometimes the registers are not updated immediately. Thus, the execution unit will lock the registers which is not

updated yet.

In target systems, the processor is allowed to fetch the next instruction immediately. However, such instruction cannot be performed immediately because there is dependence of locked registers. In some cases, processor has reservation stations, or instruction buffer, for keeping the instruction to be issue later. In addition, the reservation station allows the out-of-order issuing to be happened. The followed topics will explain more about reservation stations.

Moreover, there are some instructions that can update the value of *program counter*. So, such instructions will lock the register that represent *program counter* in the core. In the target system, we will eliminate the some behaviors which predict the next instruction such as *pre-fetch* and *branch-prediction*. Therefore, to fetch next instruction, we will make sure that the program counter is available.

#### Reservation stations for instructions

Reservation station, or instruction buffer, is a buffer to store the instructions which cannot be performed immediately. As the programmer point-of-view, the program should issue the instructions as program order. Nevertheless, to improve the performance of the system, there is mechanism, called out-of-order issue, to issue an instruction from reservation station out-of-order if that instruction is ready to be performed. To consider the ready instructions to be performed, processor have to check whether the required registers of such instructions is available to be accessed.

# 3.1.3 Hardware operations

Hardware operations refer to the operations issued by execution unit for performing the assigned instruction. In the target system, these operations are either memory access, arithmetic calculation, or fence operation for relaxed memory consistency models. In addition, in the modern processors, the predicated instruction set have been introduced. For example, Instruction set architecture of ARM processor provides instruction with condition can be attached to it such as 'MOVNE r1, #1'. The condition of 'MOVNE r1, #1' is 'NE' used to consider whether this condition will be performed or not. Thus, the behaviors of predicated instruction also be captured in the target system. In the follow topics will describe some hardware operations in details.

#### Read/Write operation

The read and write operations refer to memory operations which provide memory access to either private memory, such as register and program status registers, or shared-memory. These operations usually used in the programs to communicate each other among cores. As for read operations, the read will access the memory location to read the value. Then, the read will return the value to the issued processor. To keep the intermediate value of read, target system will store that value into the *internal bus* that will be used in the next operations. The target system allows *non-blocking read access* behaviors, which was

Figure 3-2: Example of out-of-order updates

described in section 2.1.3, to be happened in the system. Hence, the read operations will be putted into the buffer if the hardware uses this optimization mechanism.

As for write operations, the write will get the value to update the memory location in the write operation. The value should be came from the *internal bus*. Once the write operation is issued from the execution unit, the write operation will be putted into the buffer. In the target system, read and write operations are stored in the same buffer. The practical systems can contains many buffers inside a core. However, to capture the behaviors of reordering of memory operations, we have decided to use only single buffer to represent.

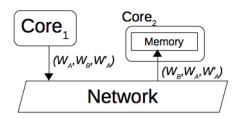

The effect of write operation will update the value of memory location. In the case of shared-memory location. The memory location will be appeared in each core separately as copies of shared-memory. In order to keep coherency among cores, the write operations will be distributed into the network. The network will update the shared-memory location for each core. However, the order of write operations is allow to be changed the order, except the writes to the same location for keeping *coherency of memory* among cores.

Let's consider the figure 3-2, the figure shows that write operations  $W_A$ ,  $W_B$  and  $W'_A$  are issued from  $Core_1$  in that order. Note that the subscriptions A and B locate the shared-memory locations. These write operations will be putted into the Network and update the memory in  $Core_2$ . In some systems, it's possible to update by the order  $(W_B, W_A, W'_A)$ . In this order,  $W_B$  is possible to be executed before  $W_A$ . Nevertheless,  $W'_A$  is not allowed to be executed before  $W_A$  because coherency properties should be kept.

### Lock/Unlock operation

These operations are used to own the permission for accessing the memory location. In the private memory locations, the *execution unit* will lock the *used registers* for the assigned instruction. This will keep the dependency among instructions even if the instructions are allowed to be issue out-of-order. As for shared-memory locations, the lock/unlock operations will be used to facilitate the read-modify-write operation which will be described in the next topic.

#### Read-modified-write operation

The read-modified-write operation is proposed to capture the atomicity behaviors. This operation will consists of a lock, an unlock, a read, and a write operation. The read

Figure 3-3: Example of read-modified-write requirement

and write operations will access the same shared-memory location. Moreover, the lock and unlock operations will used to ensure that during the execution of read and write operations, there are no another read-modified-write operations can access this location.

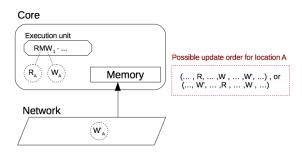

In addition, in the target systems, we have to control the behaviors of write operations that access the same location of read-modified-write operation will not interrupt execution of the read-modified-write operation. Let's consider the figure 3-3, RMW<sub>1</sub> refers to read-modified-write operation which consists of a read and a write,  $R_A$  and  $W_A$ , respectively. Moreover, network also has a write operation  $W'_A$ . These read and write operations need to access the memory location A in the core, which represent the copy of shared-memory location. However, the read-modified-write operation requires that during the executions, there is no write operations from another cores can interrupt the executions. Hence, the possible executions of these operations will be either  $(..., R_A, ..., W_A, ..., W'_A, ...)$  or  $(..., W'_A, ..., R_A, ..., W_A, ...)$ . Obviously it's possible to allow another read/write operations to interrupt executions unless they are not write operations which access to the same location.

#### Fence operation

Since the memory consistency models are provided to allow out-of-order execution, the critical section of the programs should be kept the order to avoid the violation. The fence operation is introduced for that purpose. Normally the fence operation will indicate two groups of operations as past operations and future operations. In some architecture will treat this operation as read or write operation. To separate the groups of operations, fence operations will be putted in the write buffers or read buffers. To issue the next operations, the fence operation will check that the previous operations already issued from the buffers or cores.

However, the essence of the fence operation is to keep the order of execution to be executed as the program order. Hence, in the formal model, we will just keep the information of program order of fence operation to enforce the execution in the future.

# 3.1.4 Target memory locations

The target multi-core system consists of a collection of cores and a network that connect each core together. The memory locations appeared to each core consist of *private memory locations* and *shared-memory locations*. These locations are accessed by *read/write operations* which are issued from the *buffer* or *network*.

In the practical systems, the locations of memory are described as the binary address and the index of registers. In order to abstract the system, the target system define address of memory location as a variable. This means that the address of location cannot be considered as consequent address. Hence, some optimization mechanisms are not able to be taken into account, such as merging write. As for the value to be kept inside the memory location, the target system will consider the value as a natural number instead of binary bits. Due to we need to deal with the execution order as a major topic, we will keep the calculation inside the model to be simply.

# 3.1.5 Memory consistency models

For now the behaviors of read and write operations are able to be executed out-of-order by hardware optimization mechanisms. Although the processor is able to keep the correct result of programs by itself, another processors should be able to keep the correct result too. Since the *memory consistency models* are introduced to describe the behaviors of memory, we will adopt the constraints from [Gha95] for enforcing the possible execution to produce the valid executions based on its memory consistency model.

First of all, we would like to introduce some of framework that propose by [Gha95] in order to specify the system requirements. The system requirement is used to identify the valid systems for the memory consistency model. The specification of system requirements directly defines the *ordering constraints* for a given model. This framework is appropriate to deal with the memory consistency models which are defined differently in each system. Hence, we adopt the idea of [Gha95] to realize the behaviors based on a given model. Nevertheless, we cannot use those specification directly, because the framework captures the order constraints to be happened based on the given model. In contrast, our formal model captures the execution behaviors that should be appeared in the verification. However, we will briefly describe this framework for identifying the specification of system requirement.

### Read and write operations

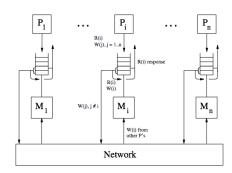

The figure 3-4 show the conceptual model for memory of their abstraction. In this model, the system consists of n processors,  $P_1, P_2, ..., P_n$ . The processor will issue the operations and put it into the buffer. Each node of processors has its own memory,  $M_i$  which belong to  $P_i$ . The memory,  $M_i$ , is a complete copy of shared-memory in the system. the each node will be connected by network. As processors use memory operations to access the memory and the presence of the copies memory, they introduce the notion of sub-operations for each memory operation. A read operation R by  $P_i$  is comprised of two atomic sub-

Figure 3-4: General model for shared-memory

operations: an initial sub-operation  $R_{init}(i)$  and a single read sub-operation R(i). A write operation W by  $P_i$  is comprised of at most n+1 atomic sub-operations: an initial write sub-operation  $W_{init}(i)$  and at most n sub-operations W(1), W(2), ..., W(n). A read operation on  $P_i$  results in the read sub-operation R(i) being placed into  $P_i$ 's memory buffer. Similarly, a write operation on  $P_i$  results in write sub-operations W(1), ..., W(n) being placed in its processor's memory buffer. The initial sub-operations  $R_{init}(i)$  and  $W_{init}(i)$  are mainly used to capture the program order among conflicting operations. Conceptually,  $R_{init}(i)$  for a read corresponds to the initial event of placing R(i) into a memory buffer and  $W_{init}(i)$  for a write corresponds to the initial event of placing W(1), ..., W(n) into the memory buffer.

Once the sub-operations are placed in the processor's buffer, these operations will be issued by system. However, it's not necessary to issue the operations as first-in-first-out order. As for W(j) issued by  $P_i$  will be placed into the network for updating the memory which belong to processor  $P_j$ . Similarly, the operation R(i) issued by  $P_i$  will be used to read the memory of processor  $P_i$ . Since the R(i) and W(i) are allowed to change the execution order,  $R_{init}(i)$  and  $W_{init}(i)$  are provided to capture the program order of these memory operations. Obviously,  $R_{init}(i)$  and  $W_{init}(i)$  are not appeared explicitly.