## **JAIST Repository**

https://dspace.jaist.ac.jp/

| Title        | A Study of Reducing Jitter and Energy Consumption<br>in Hard Real-Time Systems using Intra-task DVFS<br>Techniques |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| Author(s)    | Tseng, Bo-Yu                                                                                                       |  |  |  |

| Citation     |                                                                                                                    |  |  |  |

| Issue Date   | 2018-09                                                                                                            |  |  |  |

| Туре         | Thesis or Dissertation                                                                                             |  |  |  |

| Text version | author                                                                                                             |  |  |  |

| URL          | http://hdl.handle.net/10119/15464                                                                                  |  |  |  |

| Rights       |                                                                                                                    |  |  |  |

| Description  | Supervisor:田中 清史,先端科学技術研究科,修士<br>(情報科学)                                                                            |  |  |  |

Japan Advanced Institute of Science and Technology

A study of reducing jitter and energy consumption in hard real-time systems using Intra-task DVFS techniques

# **BO-YU TSENG**

Graduate School of Advanced Science and Technology Japan Advanced Institute of Science and Technology September, 2018

## Master's Thesis

## A study of reducing jitter and energy consumption in hard real-time systems using Intra-task DVFS techniques

# 1610105 BO-YU TSENG

Supervisor : Associate Professor Kiyofumi Tanaka Main Examiner : Associate Professor Kiyofumi Tanaka Examiners : Professor Mineo Kaneko Professor Yasushi Inoguchi Associate Professor Yuto Lim

Graduate School of Advanced Science and Technology Japan Advanced Institute of Science and Technology [Information Science]

August, 2018

#### Abstract

In some real-time control applications, the predictability of task's timing behaviour is as important as energy consumption. That predictability includes the response time and short finish time jitter. This thesis presents a jitter-aware Intra-task DVFS scheme for mitigating finish time jitter in hard real-time systems; meanwhile, the system still can consume energy efficiently. This work exploits Dynamic Voltage and Frequency Scaling (DVFS) technique to proactively manipulate actual execution/response times of tasks. The strategy proposed in this paper mainly applies control and data flow analysis of task program to insert additional frequency scaling codes (instructions to change processors voltage and frequency). Moreover, it determines the appropriate frequency scaling factor. Through evaluation by multitasking simulation, it is shown that jitter can be reduced by up to 16.2%-19.4%, and energy saving by up to 13.6%-18.39% as side effect.

### Acknowledgments

First of all, I would like to extend my sincere gratitude to my supervisor, Associate Professor Kiyofumi Tanaka, who has been helping me a lot of things during my master programme in addition to previous research student duration. He is really a responsible and professional advisor. During this two years and a half, he was always willing to be patient with me, especially whenever I got stuck in designing the algorithm, literature review, or even had problem on my presentation and writing skill (e.g., making a presentation within laboratory seminars, writing the papers and thesis). Furthermore, I really need to appreciate him that he helped me to write the recommendation for scholarship application. Thanks to his support, I could get scholarship. Although I did not study well and accomplish any successful research at all, I will still keep going in the following three-year's doctoral programme until I become a good researcher and let him be proud of me.

Next, I must thank for the NTT DOCOMO, INC., which granted me two-year scholarship. Thanks to their financial aid, I did not need to worry about the tuition fee and daily expenses. In addition, because of this scholarship, I feel I have much more responsibility in the future for doing well in my research and making contribution to our industrial field.

Besides, I would like to thank to my laboratory senior, Amr Mostafa M. Ashmawy and Doan Duy. They also kindly assisted me whenever I had difficulties or got stress in my research, e.g., research plan, programming (when I was confused about how to design the simulator efficiently), and even correcting my English all the time. Moreover, a special thank to Dr.Diego Pinheiro from Institute of Computing IComp, Federal University of Amazonas, who provided me the analysis toolset for analysing the benchmark programs, and spent few time to teach me how to use the tool, although we have never met each other.

Last but not least, I really have to express my gratitude to my lovely family (including my family's future member) who are always with me since I decided to go for master degree. It is definitely not easy to study aboard, there are a lot of pressure from financial and psychological aspects. Thanks to their unconditional support, encouragement and love, and without which I would not have come this far.

**BO-YU TSENG**

# Contents

| 3.1       Characteristic of Real-Time Task       12         3.2       Rate Monotonic Scheduling Algorithm       13         3.3       The sources and definition of Jitter       13         3.4       Modelling Timing Attributes of Jitter       15         4       Jitter-Aware Intra-Task DVFS Scheme       18         4.1       System Framework       18         4.2       Runtime Profiling       19         4.2.1       Recorded Maximum/Minimum Response Time       19         4.2.2       Updating the Recorded Slack Time       20         4.3       Control and Data Flow Analysis       21         4.3.1       Extracting Control Flow graph       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.3.4       Extracting Control Flow graph       23         4.4.1       Estimation       23         4.4.2       Checkpoint and Mining Table Placement       24         4.5       Frequency-Updated Ratio Calculation       31         4.6.1       Static-Based DVFS       32         4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35                                                                                        | $\mathbf{A}$  | bstra | $\operatorname{ct}$                              | 1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|--------------------------------------------------|----|

| 1       Introduction       7         2       Related Work       8         2.1       Dynamic Voltage and Frequency Scaling       8         2.2       Energy/Power-Aware Scheduling       8         2.3       Intra-task DVFS       10         2.4       Jitter Reduction       10         3       Static Timing Analysis toward Jitter       12         3.1       Characteristic of Real-Time Task       12         3.2       Rate Monotonic Scheduling Algorithm       13         3.3       The sources and definition of Jitter       13         3.4       Modelling Timing Attributes of Jitter       15         4       Jitter-Aware Intra-Task DVFS Scheme       18         4.1       System Framework       18         4.2       Runtime Profiling       19         4.2.1       Recorded Maximum/Minimum Response Time       19         4.2.2       Updating Actual Interference Time       20         4.3       Control and Data Flow Analysis       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.3.2       Checkpoint and Mining Table Placement       29                                                                                                                 | $\mathbf{Li}$ | st of | Figures                                          | 4  |

| 2 Related Work       8         2.1 Dynamic Voltage and Frequency Scaling       8         2.2 Energy/Power-Aware Scheduling       8         2.3 Intra-task DVFS       10         2.4 Jitter Reduction       10         3 Static Timing Analysis toward Jitter       10         3.1 Characteristic of Real-Time Task       12         3.2 Rate Monotonic Scheduling Algorithm       13         3.3 The sources and definition of Jitter       13         3.4 Modelling Timing Attributes of Jitter       15         4 Jitter-Aware Intra-Task DVFS Scheme       18         4.1 System Framework       18         4.2 Runtime Profiling       19         4.2.1 Recorded Maximum/Minimum Response Time       19         4.2.2 Updating the Recorded Slack Time       20         4.3 Control and Data Flow Analysis       21         4.3.1 Extracting Control Flow graph       21         4.3.2 Data Flow Tracing against Loop Variability       21         4.4       Execution Cycle Estimation       23         4.4.2 Checkpoint and Mining Table Placement       24         4.5 Frequency-Updated Ratio Calculation       31         4.6.1 Static-Based DVFS       32         4.6.2 Profile-Based DVFS       32         4.6.3 Discrete Bound Handli                                                | $\mathbf{Li}$ | st of | Tables                                           | 6  |

| 2.1       Dynamic Voltage and Frequency Scaling       8         2.2       Energy/Power-Aware Scheduling       8         2.3       Intra-task DVFS       10         2.4       Jitter Reduction       10         3       Static Timing Analysis toward Jitter       12         3.1       Characteristic of Real-Time Task       12         3.2       Rate Monotonic Scheduling Algorithm       13         3.3       The sources and definition of Jitter       13         3.4       Modelling Timing Attributes of Jitter       15         4       Jitter-Aware Intra-Task DVFS Scheme       18         4.1       System Framework       18         4.2       Runtime Profiling       19         4.2.1       Recorded Maximum/Minimum Response Time       19         4.2.2       Updating Actual Interference Time       20         4.3       Control and Data Flow Analysis       21         4.3.1       Extracting Control Flow graph       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.3.3       How Tracing against Loop Variability       21         4.4.4       Execution Cycle Estimation       23         4.4.1       Estrimation of Processing Cost <td< th=""><th>1</th><th>Intr</th><th>oduction</th><th>7</th></td<>                          | 1             | Intr  | oduction                                         | 7  |

| 2.2       Energy/Power-Aware Scheduling       8         2.3       Intra-task DVFS       10         2.4       Jitter Reduction       10         3       Static Timing Analysis toward Jitter       12         3.1       Characteristic of Real-Time Task       12         3.2       Rate Monotonic Scheduling Algorithm       13         3.3       The sources and definition of Jitter       13         3.4       Modelling Timing Attributes of Jitter       15         4       Jitter-Aware Intra-Task DVFS Scheme       18         4.1       System Framework       18         4.2       Runtime Profiling       19         4.2.1       Recorded Maximum/Minimum Response Time       19         4.2.2       Updating the Recorded Slack Time       20         4.3       Control and Data Flow Analysis       21         4.3.1       Extracting Control Flow graph       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.4.1       Estimation of Processing Cost       23         4.4.2       Checkpoint and Mining Table Placement       24         4.5       Frequency-Updated Ratio Calculation       31         4.6.1       Static-Based DVFS       32                                                                                                | <b>2</b>      | Rela  | ated Work                                        | 8  |

| 2.2       Energy/Power-Aware Scheduling       8         2.3       Intra-task DVFS       10         2.4       Jitter Reduction       10         3       Static Timing Analysis toward Jitter       12         3.1       Characteristic of Real-Time Task       12         3.2       Rate Monotonic Scheduling Algorithm       13         3.3       The sources and definition of Jitter       13         3.4       Modelling Timing Attributes of Jitter       15         4       Jitter-Aware Intra-Task DVFS Scheme       18         4.1       System Framework       18         4.2       Runtime Profiling       19         4.2.1       Recorded Maximum/Minimum Response Time       19         4.2.2       Updating Actual Interference Time       20         4.3       Control and Data Flow Analysis       21         4.3.1       Extracting Control Flow graph       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.4.1       Estimation of Processing Cost       23         4.4.2       Checkpoint and Mining Table Placement       24         4.5       Frequency-Scaling Point Placement       29         4.6       Frequency-Updated Ratio Calculation                                                                                          |               | 2.1   | Dynamic Voltage and Frequency Scaling            | 8  |

| 2.4Jitter Reduction103Static Timing Analysis toward Jitter123.1Characteristic of Real-Time Task123.2Rate Monotonic Scheduling Algorithm133.3The sources and definition of Jitter133.4Modelling Timing Attributes of Jitter154Jitter-Aware Intra-Task DVFS Scheme184.1System Framework184.2Runtime Profiling194.2.1Recorded Maximum/Minimum Response Time194.2.2Updating the Recorded Slack Time204.2.3Updating Actual Interference Time204.3.1Extracting Control Flow graph214.3.2Data Flow Tracing against Loop Variability214.4Execution Cycle Estimation234.4.1Estimation of Processing Cost234.4.2Checkpoint and Mining Table Placement244.5Frequency-Scaling Point Placement294.6Frequency-Updated Ratio Calculation314.6.1Static-Based DVFS324.6.2Profile-Based DVFS344.6.3Discrete Bound Handling355Evaluation375.1Experimental Setup37                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | 2.2   | Energy/Power-Aware Scheduling                    | 8  |

| 3 Static Timing Analysis toward Jitter       12         3.1 Characteristic of Real-Time Task       12         3.2 Rate Monotonic Scheduling Algorithm       13         3.3 The sources and definition of Jitter       13         3.4 Modelling Timing Attributes of Jitter       15         4 Jitter-Aware Intra-Task DVFS Scheme       18         4.1 System Framework       18         4.2 Runtime Profiling       19         4.2.1 Recorded Maximum/Minimum Response Time       19         4.2.2 Updating the Recorded Slack Time       20         4.2.3 Updating Actual Interference Time       20         4.3.4 Execution Optic Estimation       21         4.3.2 Data Flow Tracing against Loop Variability       21         4.4 Execution Cycle Estimation       23         4.4.1 Estimation of Processing Cost       23         4.4.2 Checkpoint and Mining Table Placement       24         4.5 Frequency-Scaling Point Placement       29         4.6 Frequency-Updated Ratio Calculation       31         4.6.2 Profile-Based DVFS       32         4.6.3 Discrete Bound Handling       35         5 Evaluation       37         5.1 Experimental Setup       37                                                                                                                      |               | 2.3   | Intra-task DVFS                                  | 10 |

| 3.1Characteristic of Real-Time Task123.2Rate Monotonic Scheduling Algorithm133.3The sources and definition of Jitter133.4Modelling Timing Attributes of Jitter154Jitter-Aware Intra-Task DVFS Scheme184.1System Framework184.2Runtime Profiling194.2.1Recorded Maximum/Minimum Response Time194.2.2Updating the Recorded Slack Time204.3Control and Data Flow Analysis214.3.1Extracting Control Flow graph214.3.2Data Flow Tracing against Loop Variability214.4Execution Cycle Estimation234.4.1Estimation of Processing Cost234.4.2Checkpoint and Mining Table Placement244.5Frequency-Scaling Point Placement294.6Frequency-Updated Ratio Calculation314.6.3Discrete Bound Handling355Evaluation375.1Experimental Setup37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               | 2.4   | Jitter Reduction                                 | 10 |

| 3.2       Rate Monotonic Scheduling Algorithm       13         3.3       The sources and definition of Jitter       13         3.4       Modelling Timing Attributes of Jitter       15         4       Jitter-Aware Intra-Task DVFS Scheme       18         4.1       System Framework       18         4.2       Runtime Profiling       19         4.2.1       Recorded Maximum/Minimum Response Time       19         4.2.2       Updating the Recorded Slack Time       20         4.3       Control and Data Flow Analysis       21         4.3.1       Extracting Control Flow graph       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.3.1       Extracting Control Flow graph       23         4.4.2       Checkpoint and Mining Table Placement       29         4.4.3       Estimation of Processing Cost       23         4.4.2       Checkpoint and Mining Table Placement       24         4.5       Frequency-Scaling Point Placement       29         4.6       Frequency-Updated Ratio Calculation       31         4.6.2       Profile-Based DVFS       32         4.6.3       Discrete Bound Handling       35         5       Evaluation <t< td=""><td>3</td><td>Stat</td><td>cic Timing Analysis toward Jitter</td><td>12</td></t<> | 3             | Stat  | cic Timing Analysis toward Jitter                | 12 |

| 3.3The sources and definition of Jitter133.4Modelling Timing Attributes of Jitter154Jitter-Aware Intra-Task DVFS Scheme184.1System Framework184.2Runtime Profiling194.2.1Recorded Maximum/Minimum Response Time194.2.2Updating the Recorded Slack Time204.2.3Updating Actual Interference Time204.3Control and Data Flow Analysis214.3.1Extracting Control Flow graph214.3.2Data Flow Tracing against Loop Variability214.4Execution Cycle Estimation234.4.1Estimation of Processing Cost234.4.2Checkpoint and Mining Table Placement244.5Frequency-Updated Ratio Calculation314.6.1Static-Based DVFS324.6.2Profile-Based DVFS344.6.3Discrete Bound Handling355Evaluation375.1Experimental Setup37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               | 3.1   | Characteristic of Real-Time Task                 | 12 |

| 3.3The sources and definition of Jitter133.4Modelling Timing Attributes of Jitter154Jitter-Aware Intra-Task DVFS Scheme184.1System Framework184.2Runtime Profiling194.2.1Recorded Maximum/Minimum Response Time194.2.2Updating the Recorded Slack Time204.2.3Updating Actual Interference Time204.3Control and Data Flow Analysis214.3.1Extracting Control Flow graph214.3.2Data Flow Tracing against Loop Variability214.4Execution Cycle Estimation234.4.1Estimation of Processing Cost234.4.2Checkpoint and Mining Table Placement244.5Frequency-Updated Ratio Calculation314.6.1Static-Based DVFS324.6.2Profile-Based DVFS344.6.3Discrete Bound Handling355Evaluation375.1Experimental Setup37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               | 3.2   | Rate Monotonic Scheduling Algorithm              | 13 |

| 4Jitter-Aware Intra-Task DVFS Scheme184.1System Framework184.2Runtime Profiling194.2.1Recorded Maximum/Minimum Response Time194.2.2Updating the Recorded Slack Time204.2.3Updating Actual Interference Time204.3Control and Data Flow Analysis214.3.1Extracting Control Flow graph214.3.2Data Flow Tracing against Loop Variability214.4Execution Cycle Estimation234.4.1Estimation of Processing Cost234.4.2Checkpoint and Mining Table Placement244.5Frequency-Updated Ratio Calculation314.6.1Static-Based DVFS324.6.2Profile-Based DVFS344.6.3Discrete Bound Handling355Evaluation375.1Experimental Setup37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               | 3.3   |                                                  | 13 |

| 4.1       System Framework       18         4.2       Runtime Profiling       19         4.2.1       Recorded Maximum/Minimum Response Time       19         4.2.2       Updating the Recorded Slack Time       20         4.2.3       Updating Actual Interference Time       20         4.3.1       Extracting Control Flow graph       21         4.3.2       Data Flow Analysis       21         4.3.1       Extracting Control Flow graph       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.4       Execution Cycle Estimation       23         4.4.1       Estimation of Processing Cost       23         4.4.2       Checkpoint and Mining Table Placement       24         4.5       Frequency-Scaling Point Placement       29         4.6       Frequency-Updated Ratio Calculation       31         4.6.1       Static-Based DVFS       32         4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35         5       Evaluation       37         5.1       Experimental Setup       37                                                                                                                                    |               | 3.4   | Modelling Timing Attributes of Jitter            | 15 |

| 4.2       Runtime Profiling       19         4.2.1       Recorded Maximum/Minimum Response Time       19         4.2.2       Updating the Recorded Slack Time       20         4.2.3       Updating Actual Interference Time       20         4.3       Control and Data Flow Analysis       21         4.3.1       Extracting Control Flow graph       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.4       Execution Cycle Estimation       23         4.4.1       Estimation of Processing Cost       23         4.4.2       Checkpoint and Mining Table Placement       24         4.5       Frequency-Scaling Point Placement       29         4.6       Frequency-Updated Ratio Calculation       31         4.6.1       Static-Based DVFS       32         4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35         5       Evaluation       37         5.1       Experimental Setup       37                                                                                                                                                                                                                                 | 4             | Jitte | er-Aware Intra-Task DVFS Scheme                  | 18 |

| 4.2       Runtime Profiling       19         4.2.1       Recorded Maximum/Minimum Response Time       19         4.2.2       Updating the Recorded Slack Time       20         4.2.3       Updating Actual Interference Time       20         4.3       Control and Data Flow Analysis       21         4.3.1       Extracting Control Flow graph       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.4       Execution Cycle Estimation       23         4.4.1       Estimation of Processing Cost       23         4.4.2       Checkpoint and Mining Table Placement       24         4.5       Frequency-Scaling Point Placement       29         4.6       Frequency-Updated Ratio Calculation       31         4.6.1       Static-Based DVFS       32         4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35         5       Evaluation       37         5.1       Experimental Setup       37                                                                                                                                                                                                                                 |               | 4.1   | System Framework                                 | 18 |

| 4.2.2Updating the Recorded Slack Time204.2.3Updating Actual Interference Time204.3Control and Data Flow Analysis214.3.1Extracting Control Flow graph214.3.2Data Flow Tracing against Loop Variability214.4Execution Cycle Estimation234.4.1Estimation of Processing Cost234.4.2Checkpoint and Mining Table Placement244.5Frequency-Scaling Point Placement294.6Frequency-Updated Ratio Calculation314.6.1Static-Based DVFS344.6.3Discrete Bound Handling355Evaluation375.1Experimental Setup37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | 4.2   |                                                  | 19 |

| 4.2.2Updating the Recorded Slack Time204.2.3Updating Actual Interference Time204.3Control and Data Flow Analysis214.3.1Extracting Control Flow graph214.3.2Data Flow Tracing against Loop Variability214.4Execution Cycle Estimation234.4.1Estimation of Processing Cost234.4.2Checkpoint and Mining Table Placement244.5Frequency-Scaling Point Placement294.6Frequency-Updated Ratio Calculation314.6.1Static-Based DVFS344.6.3Discrete Bound Handling355Evaluation375.1Experimental Setup37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |       | 4.2.1 Recorded Maximum/Minimum Response Time     | 19 |

| 4.3       Control and Data Flow Analysis       21         4.3.1       Extracting Control Flow graph       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.4       Execution Cycle Estimation       23         4.4.1       Estimation of Processing Cost       23         4.4.2       Checkpoint and Mining Table Placement       24         4.5       Frequency-Scaling Point Placement       29         4.6       Frequency-Updated Ratio Calculation       31         4.6.1       Static-Based DVFS       32         4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35         5       Evaluation       37         5.1       Experimental Setup       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |       |                                                  | 20 |

| 4.3.1       Extracting Control Flow graph       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.4       Execution Cycle Estimation       23         4.4.1       Estimation of Processing Cost       23         4.4.2       Checkpoint and Mining Table Placement       24         4.5       Frequency-Scaling Point Placement       29         4.6       Frequency-Updated Ratio Calculation       31         4.6.1       Static-Based DVFS       32         4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35         5       Evaluation       37         5.1       Experimental Setup       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |       |                                                  | 20 |

| 4.3.1       Extracting Control Flow graph       21         4.3.2       Data Flow Tracing against Loop Variability       21         4.4       Execution Cycle Estimation       23         4.4.1       Estimation of Processing Cost       23         4.4.2       Checkpoint and Mining Table Placement       24         4.5       Frequency-Scaling Point Placement       29         4.6       Frequency-Updated Ratio Calculation       31         4.6.1       Static-Based DVFS       32         4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35         5       Evaluation       37         5.1       Experimental Setup       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               | 4.3   | Control and Data Flow Analysis                   | 21 |

| 4.4       Execution Cycle Estimation       23         4.4.1       Estimation of Processing Cost       23         4.4.2       Checkpoint and Mining Table Placement       24         4.5       Frequency-Scaling Point Placement       29         4.6       Frequency-Updated Ratio Calculation       31         4.6.1       Static-Based DVFS       32         4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35         5       Evaluation       37         5.1       Experimental Setup       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |       | *                                                | 21 |

| 4.4.1       Estimation of Processing Cost       23         4.4.2       Checkpoint and Mining Table Placement       24         4.5       Frequency-Scaling Point Placement       29         4.6       Frequency-Updated Ratio Calculation       31         4.6.1       Static-Based DVFS       32         4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35         5       Evaluation       37         5.1       Experimental Setup       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |       | 4.3.2 Data Flow Tracing against Loop Variability | 21 |

| 4.4.2       Checkpoint and Mining Table Placement       24         4.5       Frequency-Scaling Point Placement       29         4.6       Frequency-Updated Ratio Calculation       31         4.6.1       Static-Based DVFS       32         4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35         5       Evaluation       37         5.1       Experimental Setup       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               | 4.4   | Execution Cycle Estimation                       | 23 |

| 4.4.2       Checkpoint and Mining Table Placement       24         4.5       Frequency-Scaling Point Placement       29         4.6       Frequency-Updated Ratio Calculation       31         4.6.1       Static-Based DVFS       32         4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35         5       Evaluation       37         5.1       Experimental Setup       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |       | 4.4.1 Estimation of Processing Cost              | 23 |

| 4.5       Frequency-Scaling Point Placement       29         4.6       Frequency-Updated Ratio Calculation       31         4.6.1       Static-Based DVFS       32         4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35         5       Evaluation       37         5.1       Experimental Setup       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |       | °                                                | 24 |

| 4.6       Frequency-Updated Ratio Calculation       31         4.6.1       Static-Based DVFS       32         4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35         5       Evaluation       37         5.1       Experimental Setup       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               | 4.5   |                                                  |    |

| 4.6.1       Static-Based DVFS       32         4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35         5       Evaluation       37         5.1       Experimental Setup       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               | 4.6   |                                                  | 31 |

| 4.6.2       Profile-Based DVFS       34         4.6.3       Discrete Bound Handling       35         5       Evaluation       37         5.1       Experimental Setup       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |       |                                                  | 32 |

| 4.6.3 Discrete Bound Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |       |                                                  | 34 |

| 5.1 Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |       |                                                  |    |

| 5.1 Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>5</b>      | Eva   | luation                                          | 37 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               | 5.1   | Experimental Setup                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |       |                                                  |    |

|              |       | 5.1.2 Task-Set and Test Pattern Generation Algorithm | 38        |

|--------------|-------|------------------------------------------------------|-----------|

|              |       | 5.1.3 Jitter Constraint Settings                     | 42        |

|              |       | 5.1.4 Implementation of Simulator                    | 42        |

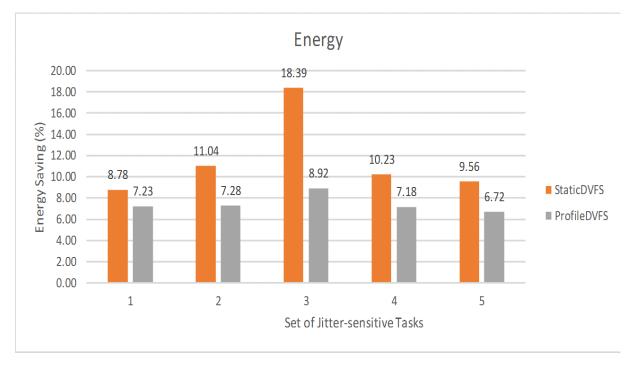

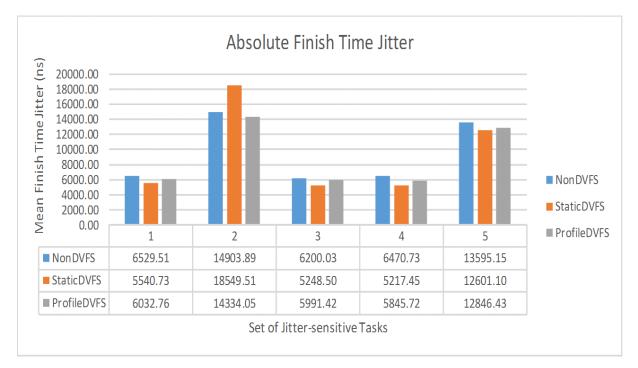

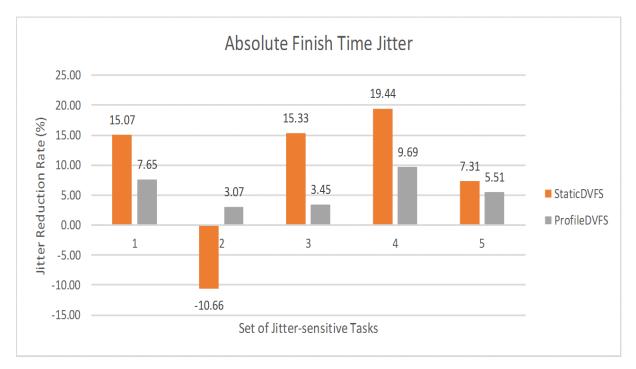

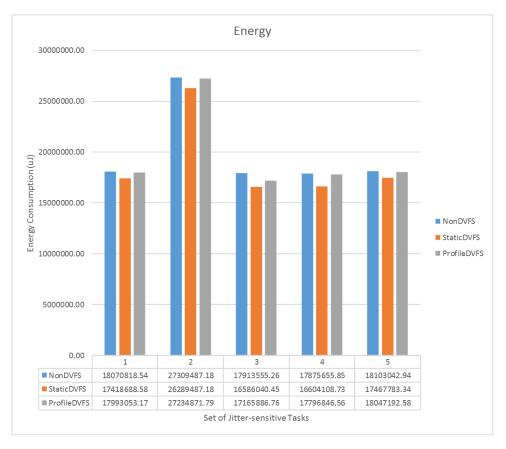

|              | 5.2   | Experimental Results                                 | 46        |

| 6            | Con   | nclusion                                             | 51        |

|              | 6.1   | Summary                                              | 51        |

|              | 6.2   | Future Work                                          | 51        |

| 7            | Pub   | olication                                            | <b>53</b> |

| A            | ppen  | dices                                                | <b>54</b> |

| $\mathbf{A}$ | The   | e Required Execution Cycles for each instruction     | <b>54</b> |

| В            | CFC   | Gs of Benchmarks                                     | 55        |

| С            | Ann   | notation of Scaling Point                            | 60        |

| Bi           | bliog | graphy                                               | 61        |

# List of Figures

| 2.1  | Original task scheduling                                                           | 9  |

|------|------------------------------------------------------------------------------------|----|

| 2.2  | Inter-task DVFS                                                                    | 9  |

| 2.3  | Intra-task DVFS                                                                    | 9  |

| 2.4  | The workflow of existing Intra-task DVFS scheme                                    | 10 |

| 3.1  | The timeline of one periodic task's feature                                        | 12 |

| 3.2  | Example of Rate-Monotonic scheduling                                               | 14 |

| 3.3  | Example of Rate-Monotonic task scheduling                                          | 15 |

| 3.4  | The input-output delay in a control task. The symbol $h$ is period of the          |    |

|      | control task. $[11]$                                                               | 16 |

| 3.5  | The target response time from the perspective of <i>Jitter Margin</i>              | 17 |

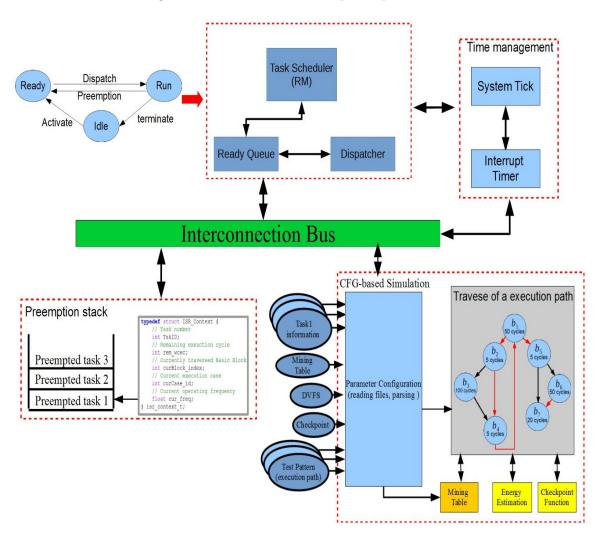

| 4.1  | The framework of Jitter-aware Intra-task DVFS scheme                               | 19 |

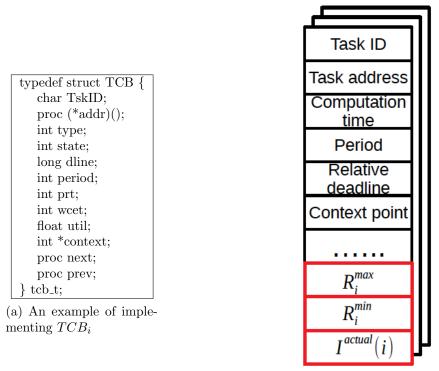

| 4.2  | The task control blocks featuring tasks for system kernel to manage                | 20 |

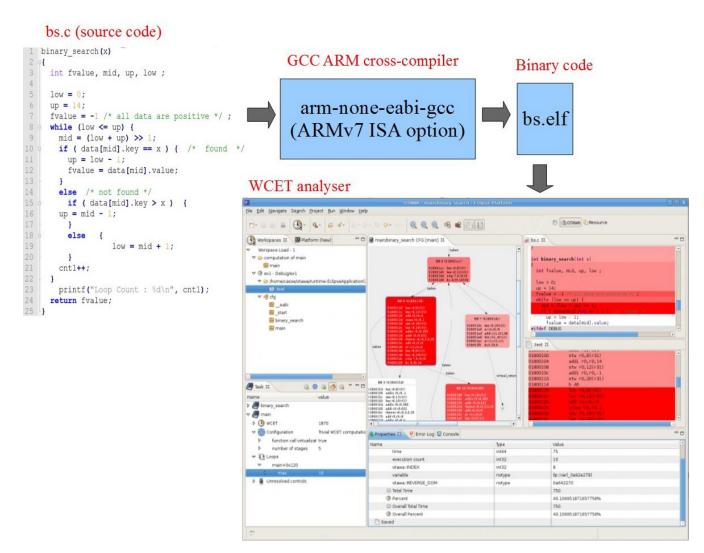

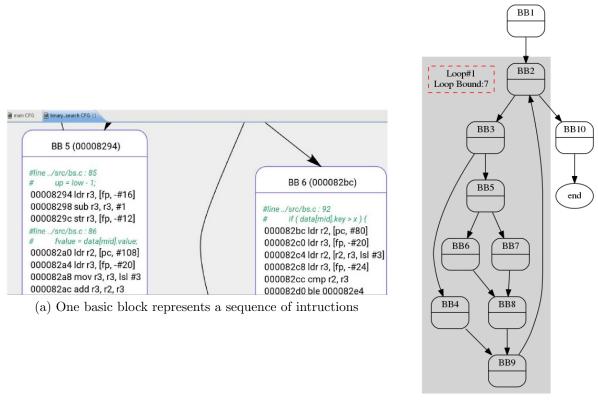

| 4.3  | Extracting CFG using OTAWA WCET analyser                                           | 22 |

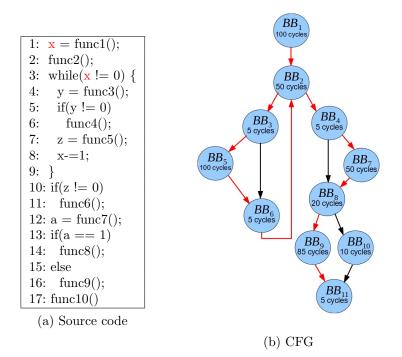

| 4.4  | Control flow of target task's source code                                          | 23 |

| 4.5  | Example program with <b>for-loop</b>                                               | 23 |

| 4.6  | An example of loop dependency                                                      | 24 |

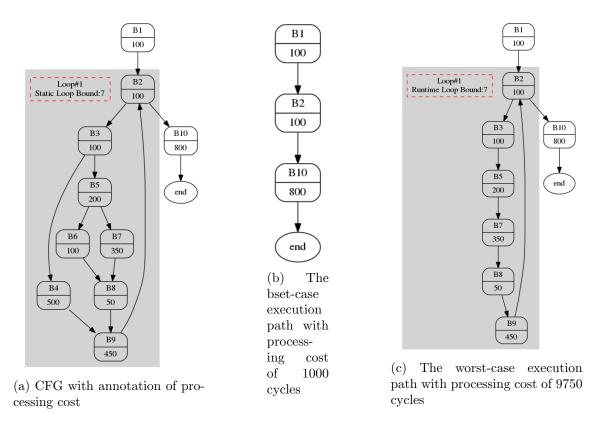

| 4.7  | The control flow graph after processing cost estimation                            | 25 |

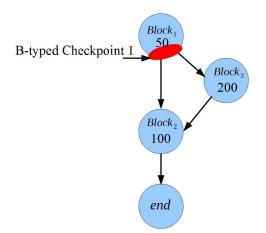

| 4.8  | The location of B-type checkpoint                                                  | 26 |

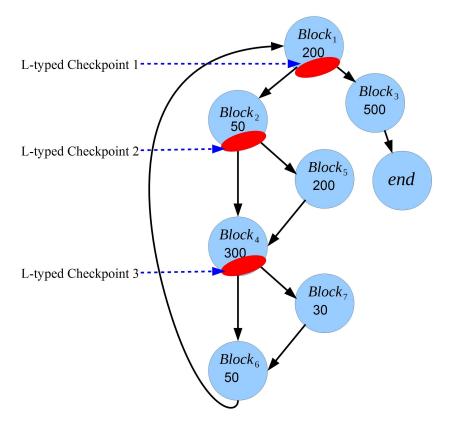

| 4.9  | The location of L-type checkpoint                                                  | 27 |

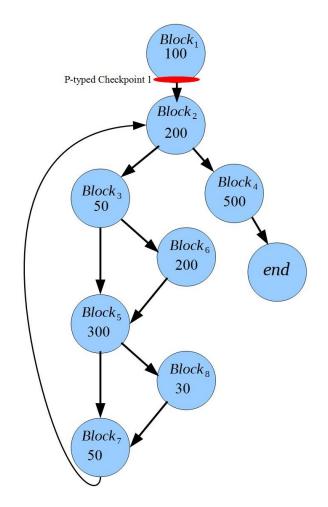

| 4.10 | The location of P-type checkpoint                                                  | 29 |

| 4.11 | The finish time jitter caused by the variance of interference time                 | 30 |

|      | An example of user-specified target response time                                  | 32 |

| 4.13 | The discrete bound of practical processor                                          | 36 |

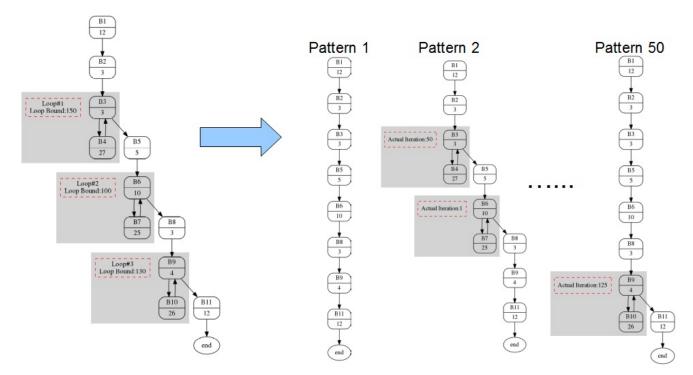

| 5.1  | Generating fifty execution path patterns for $\mathbf{compress}$ 's CFG $\ldots$ . | 40 |

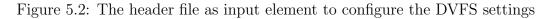

| 5.2  | The header file as input element to configure the DVFS settings                    | 43 |

| 5.3  | The configuration files of target task                                             | 44 |

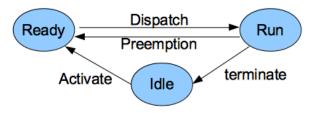

| 5.4  | The states of every task during runtime                                            | 45 |

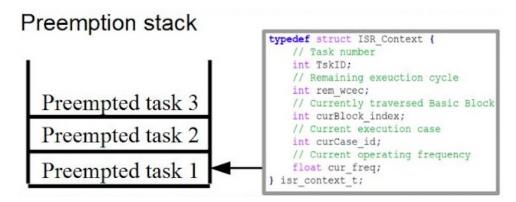

| 5.5  | The structure of preemption stack                                                  | 45 |

| 5.6  | The whole system framework                                                         | 45 |

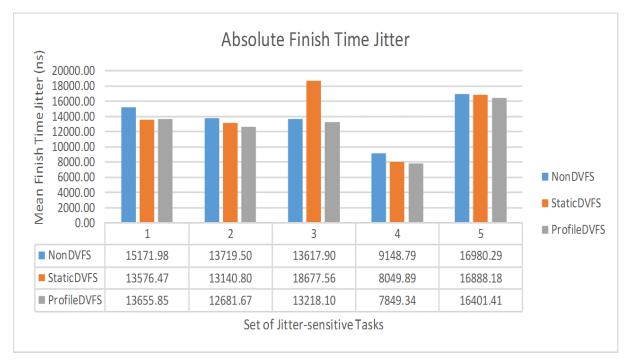

| 5.7  | Absolute finish time jitter of task-set 1                                          | 46 |

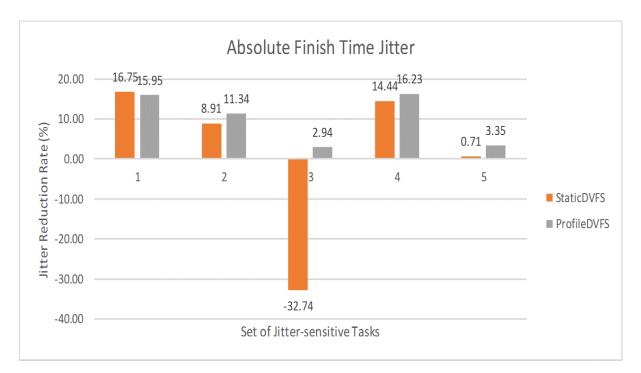

| 5.8  | Jitter reduction rate of task-set 1                                                | 47 |

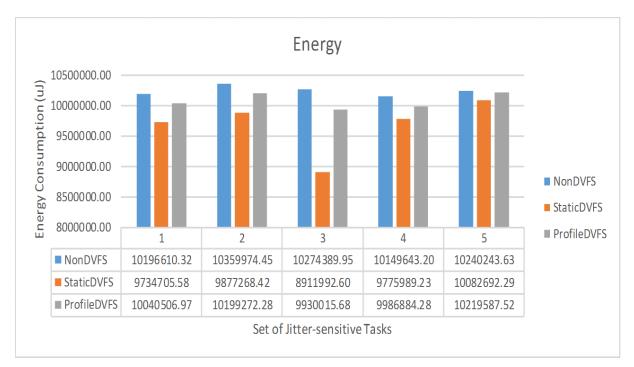

| 5.9  | Energy consumption of task-set 1                                                   | 47 |

| 5.10 | 0, 0                                                                               | 48 |

| 5.11 | Absolute finish time jitter of task-set 2                                          | 48 |

| 5.12 |                                                                                    | 49 |

|      | Energy consumption of task-set 2                                                   | 49 |

| 5.14 | Energy-saving rate of task-set 2                                                   | 50 |

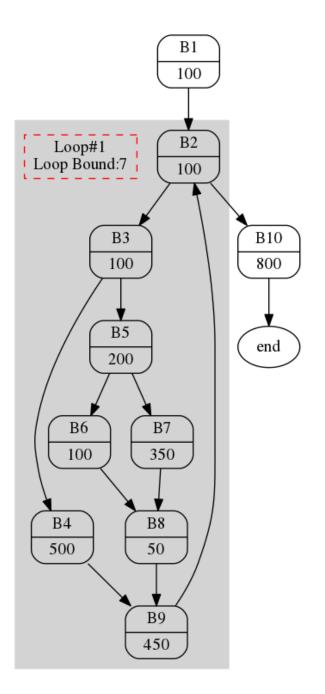

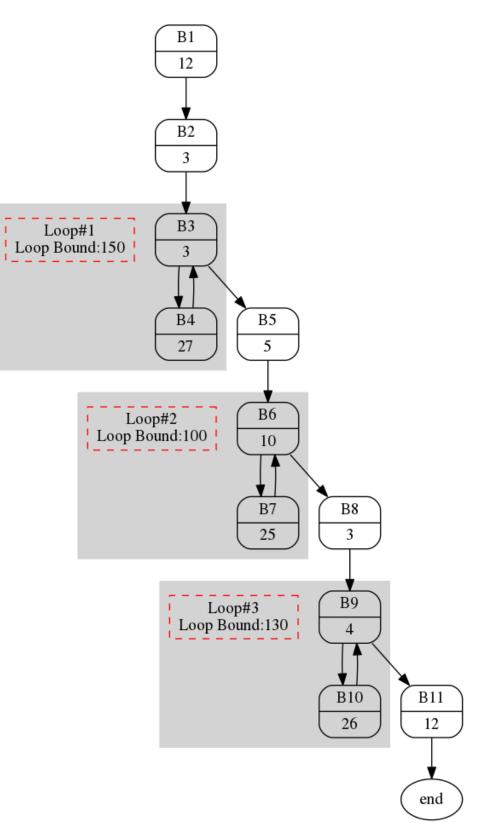

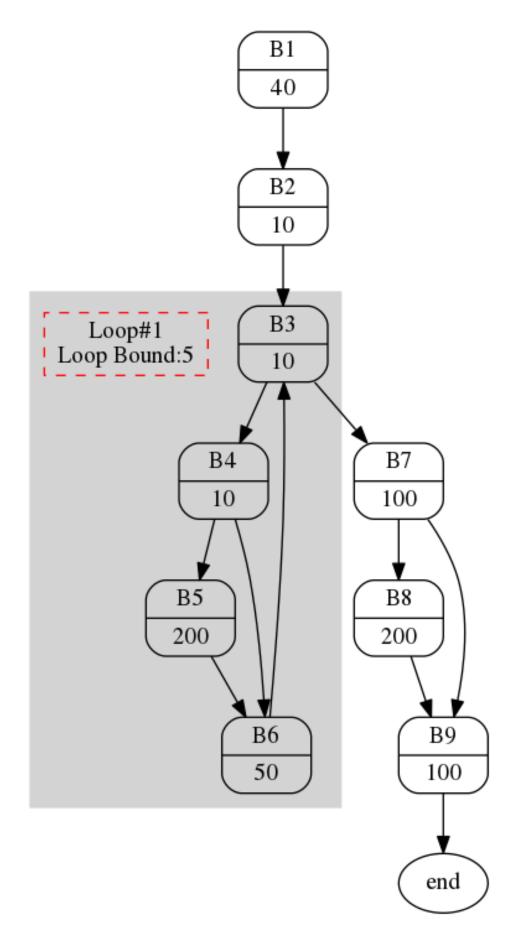

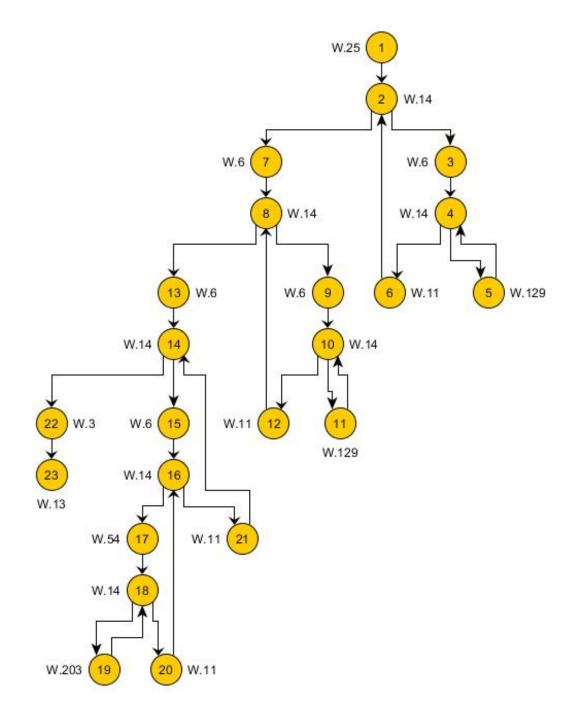

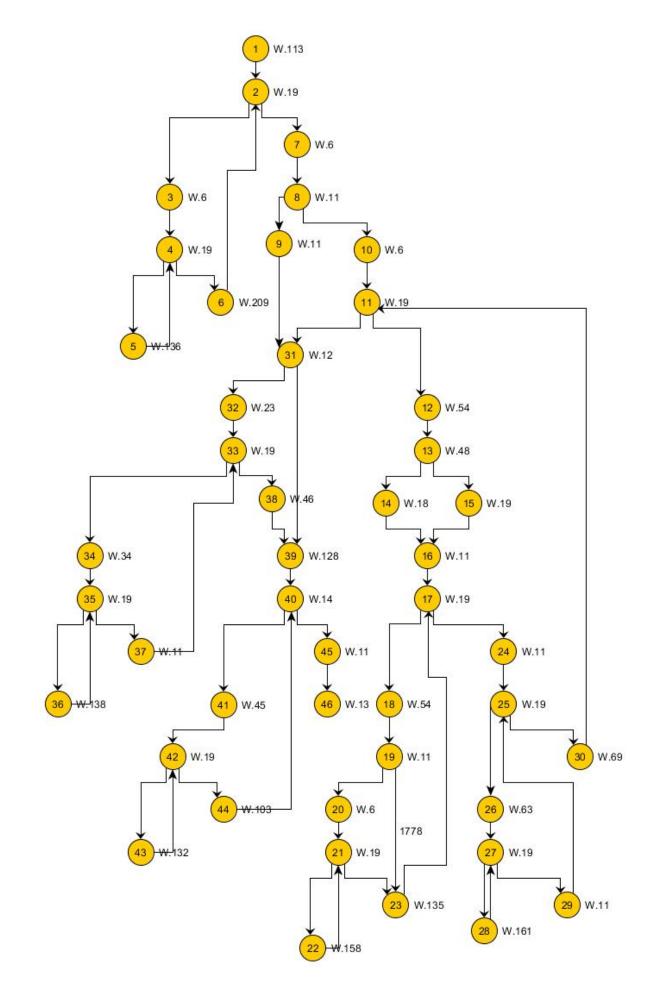

| B.1 | The CFG of bs.c                                                                 | 55       |

|-----|---------------------------------------------------------------------------------|----------|

| B.2 | The CFG of compress.c                                                           | 56       |

| B.3 | The CFG of case study                                                           | 57       |

| B.4 | The CFG of matmult.c                                                            | 58       |

| B.5 | The CFG of ludcmp.c                                                             | 59       |

| 0.1 |                                                                                 | <u> </u> |

| C.1 | The annotation file for configuring the frequency-scaling points at every CFG 6 | 00       |

# List of Tables

| 4.1 | B-type mining table                                                          | 26 |

|-----|------------------------------------------------------------------------------|----|

| 4.2 | L-type mining table                                                          | 27 |

| 4.3 | P-type mining table                                                          | 29 |

| 4.4 | The DVFS-aware code instrumentation in task's source code                    | 31 |

| 4.5 | The operating points of Sitara AM335x family processor $\ . \ . \ . \ . \ .$ | 36 |

| 5.1 | The information of chosen benchmarks                                         | 38 |

| 5.2 | The generated task sets                                                      | 39 |

| 5.3 | The result of response-time analysis                                         | 39 |

| 5.4 | The sets of jitter-sensitivity tasks                                         | 42 |

| A.1 | The list of required execution cycles of each instruction                    | 54 |

# Chapter 1 Introduction

In the hard real time systems, every periodic task is required to perform deterministic timing behaviour, i.e., explicit timing constraint (specific deadline, low jitter). Among them, schedulability of multitasking is the highest criticality in hard real-time system which is not allowed to be violated. To maintain the schedulability, feasible task scheduling algorithms have been studied for decades. However, predictability of response times of periodic tasks is also a critical concern in some real-time applications, e.g., control system or data acquisition. In the context of task scheduling, due to the task interaction (preemption, precedence constraint or synchronisation protocol), memory access latency, shared-resource contention or I/O device accesses, systems may face great runtime variation in response time, called finish time jitter. Especially, in the real-time control applications, finish time jitter can be tolerated whilst it does not lead a degradation of system performance. However, large jitter can impact predictability in terms of timing domain. This unpredictability can degrade stability (some fluctuation behaviour) or processing accuracy of system [11, 22]. Thereby jitter ought to be kept as low as possible.

The objective of this paper is to reduce finishing time jitter under Rate-Monotonic scheduling (RM) whilst keeping the system consuming energy efficiently. A **jitter-aware Intra-task DVFS scheme** is proposed to make task scheduling adapt to runtime variations due to both interference and execution time. The Intra-task DVFS approach [25,31,33,35] promises finer granularity of frequency scaling within one instance of task's execution. Thus, it relatively outperforms the Inter-task DVFS approach in terms of energy reduction. Apart from the effect of energy efficiency, it is expected that the Intra-task DVFS approach manipulates finishing time jitter. The proposed algorithms target at reducing variation in both execution time and interference time.

This work is the first to control the finishing time jitter using Intra-task DVFS, to the best of the authors knowledge.

# Chapter 2 Related Work

As stated in Chapter 1, this research is to mitigate the finish time jitter whilst keeping the energy efficiency using the Intra-task DVFS techniques. Therefore, it is necessary to introduce the concept of DVFS, how the task scheduling can cooperate with DVFS mechanism, and the existing solutions of jitter reduction.

### 2.1 Dynamic Voltage and Frequency Scaling

There are enormous techniques which have been proposed for reducing energy consumption or thermal issue in CMOS devices (e.g., processor). One of the widely used approaches is *Dynamic Voltage and Frequency Scaling (DVFS)*. Nowadays, most of processors (e.g., Intel XScale PXA270 [20], Texas Instruments Sitra AM335x [16], AMD Zacate [27]) support the DVFS mechanism for energy efficiency of embedded system platforms, laptop or cloud datacenters [37] when they are in active states. With the DVFS mechanism, processors can perform multiple levels of supply voltage and operating frequency in various system requirement. For instance, whilst the application's processes do not need to be executed at the high computational performance, processor may scale down the operating frequency and its corresponding supply voltage to avoid energy dissipation.

Specifically, DVFS technique is to deal with energy consumption caused by *dynamic* power  $(P_{dynamic})^1$ . When the processor is operating at clock frequency f with supply voltage  $V_{dd}$ . The  $P_{dynamic}$  can be written as follows:

$$P_{dynamic} = \alpha \times C_{eff} \times V_{dd}^2 \times f \tag{2.1}$$

where  $\alpha$  is the switching activity,  $C_{eff}$  is the load capacitance.

According to the equation 2.1, the dynamic power is proportional to the operating frequency and quadratically proportional to the supply voltage. Therefore, the processor reduces operating frequency and supply voltage together, to achieve the energy saving.

## 2.2 Energy/Power-Aware Scheduling

In the energy-aware task scheduling, the DVFS techniques are classified into Inter-task and Intra-task according to the scaling granularity. Inter-task DVFS [2, 7, 12, 19] determines the supply voltage and operating frequency for each execution duration on task-by-task perspective. That is, system assesses adequate operating frequency(and its corresponding supply voltage) for every instance of tasks. On the other hand, Intra-task

<sup>&</sup>lt;sup>1</sup>Energy consumption of a CMOS device includes two sources [36]: dynamic power and static power.

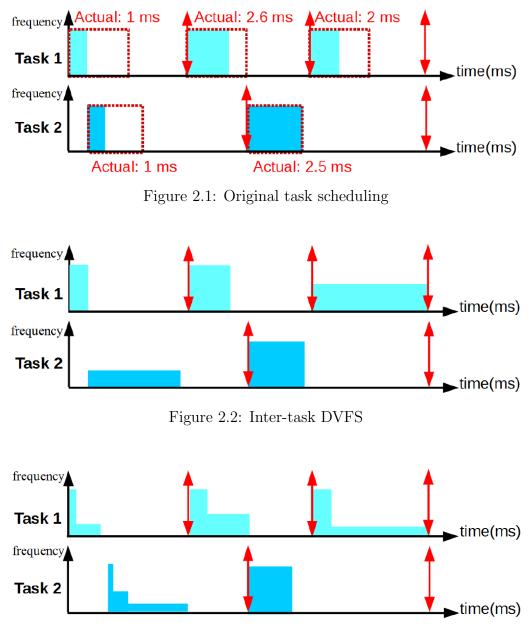

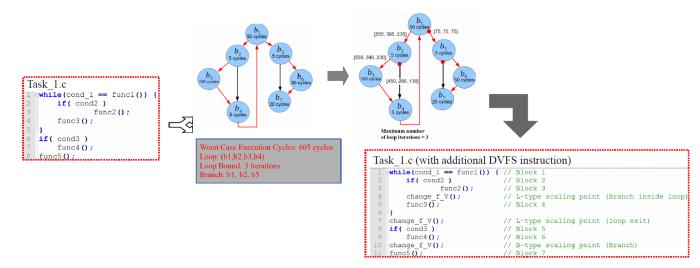

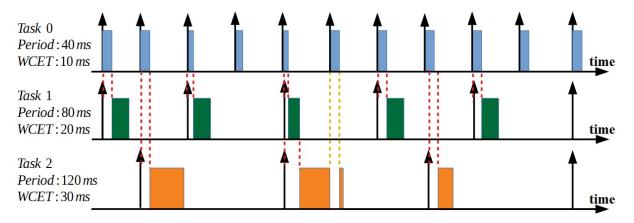

DVFS [3,25,28,29,31–33,35,39] adjusts the supply voltage and operating frequency within each individual-task boundary. Therefore, the major difference between them is that the former deals with the existing slack time during any two consecutive instances of tasks, whereas the latter manages to predict the upcoming slack time generated by the running task itself. The Figure 2.1 to 2.3 illustrate the difference between Inter-task and Intra-task DVFS scheduling. The Figure 2.1 is the original task scheduling without DVFS mechanism. Because both task 1 and task 2 finish their execution times earlier than *worst-case execution times*, system leaves some slack times in which the processor is in idle state. Consequently, in Figure 2.2, if Inter-task DVFS mechanism is enabled, every instance of any task will combine the slack time (left by previous running task) with its available execution and decide a lower operating frequency to run through. On the other hand, in Figure 2.3, if Intra-task DVFS mechanism is enabled, every instance of any task will be run under multiple operating frequency by predicting the upcoming slack time arising from the current instance's execution itself.

Figure 2.3: Intra-task DVFS

#### 2.3 Intra-task DVFS

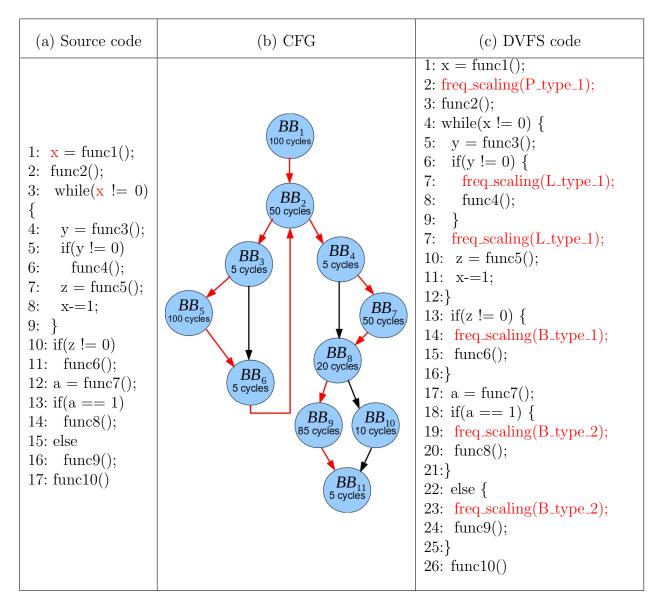

As for the main scheme of Intra-task DVFS, the objective is to decide in which execution points the processor should adjust its processing speed within the execution of one task's program; moreover the specific *speed-updated ratio* is assessed in order to reduce the energy consumption whilst preventing deadline miss. There are two different approaches to achieve Intra-task DVFS, i.e., stochastic-based Intra-task [38] and path-based Intratask [25, 29, 31–33]. The former divides every task's program into several code sections and furthermore analyses the stochastic information of each code section (e.g., average execution time, probabilistic distribution, etc.). On the other hand, the procedures of path-base Intra-task can be generally organised into timing analysis (control and data flow information), placement of program checkpoint and calculation of speed-updated ratio. First, timing analysis can give tight WCET bounds of every program by the *control flow* graph (CFG) and data flow information (e.g., loop dependencies). It provides the hints about the locations where the runtime variation (i.e., the causes of slack times in the future) may occur. The example is the appearance of branch instruction or loop (a multiple iteration of branch instruction). Second, the program checkpoints are inserted at some program regions in order to trace the actual control flow during runtime. Accordingly, the locations of checkpoints can be at the exits of branch instructions and loops (corresponding to the B-type voltage-scaling point and L-type voltage-scaling point respectively [25, 31,32). Thus, the actual execution flow of one task within any instance becomes clear. Last, every program checkpoint decided by previous step is regarded as a candidate for speed adjustment (voltage/frequency scaling). If the successive execution path (of the current control flow) where it is directing is not the longest path (the execution path taking the largest execution cycles among its all branches), processor slows down the processing speed but still makes task complete before the given WCET/deadline and overall energy consumption can be further reduced.

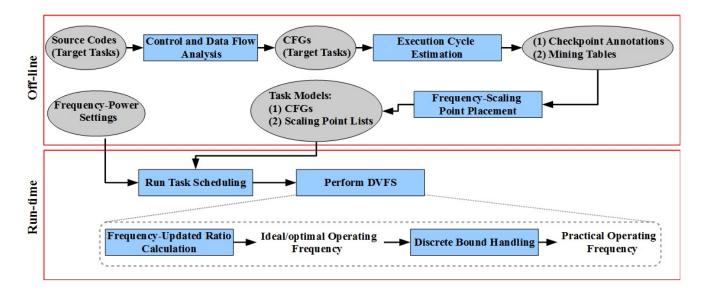

The existing approaches of Intra-task DVFS scheme are summarised in the illustration of Figure 2.4.

Figure 2.4: The workflow of existing Intra-task DVFS scheme

#### 2.4 Jitter Reduction

To reduce jitter, a *deadline assignment algorithm* by linear programming was proposed [17] under the EDF scheduling environments [21]. Deadline assignment attempts to shorten

relative deadlines of some periodic tasks whilst keeping the schedulability, by promoting priorities of certain tasks to reduce the number of preemptions. Variation in preemption duration makes contribution to jitter. Accordingly the less the preemption, the less the jitter. In addition, some similar researches propose the period adjustment algorithms [6, 22] for fixed-priority preemptive scheduling environment. Especially, they apply the notion of *jitter margin* [11] (it will be introduced in Chapter 3) with feedback loop control technique to reduce the impact of task scheduling on the presence of jitter. Although those ideas reduce the finish time jitter by shortening the start time jitter, the variance of actual execution time is not directly handled. In particular, if the periods of tasks are much greater than finish time jitters then the effectiveness obtained from such approach is relatively small; moreover, the nature of their approaches manages to change the priorities of some tasks from original task schedules, whilst the literature [15] shows that it may violate the schedulability of the system in some cases.

Other works exploit DVFS to handle jitter [1,23,24]. They proves that DVFS mechanism enables the system to control the actual execution/response times of periodic tasks, thus it is applicable to reducing finish time jitter. Mochocki, et al. exploit only the suitable portion of slack time to scale down the operating frequency for some lower-priority tasks instances instead of aggressively using all slack time for energy reduction [23]. However, their work is based on Inter-task perspective, hence frequency scaling can be performed only at the start time of every instance of tasks.

On the other hand, Phatrapornnant and Pont point out the issue of *DVFS-induced* variance in task scheduling. This issue is discussed that, the usage of DVFS-based task scheduling schemes mainly aim at minimising systems energy consumption under the constraints of schedulability. But it also incurs a great deal of uncertainty about actual response times (especially the duration of execution time).

Hence they proposed a similar jitter-aware DVFS algorithm called TTC-jDVS algorithm. This algorithm manages to suppress the impact of DVFS on response times's predictability. Firstly, It assumes that some tasks require low jitter (defined as reduced-jitter tasks) and others are unnecessary. Then system would intentionally add certain length of delays after the completions of particular tasks which are not reduced-jitter tasks. Thus, the following reduced-jitter tasks only can get fewer slack time to perform the DVFS operation. Consequently the aggressive frequency scaling can be avoided. However, despite of their effort on TTC-jDVS algorithm, the variation in actual execution time is still not dealt with directly (the finish time jitter is still overlooked).

# Chapter 3

# Static Timing Analysis toward Jitter

#### 3.1 Characteristic of Real-Time Task

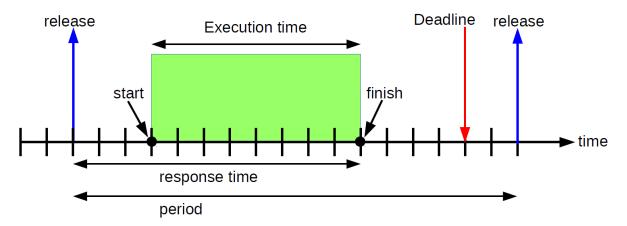

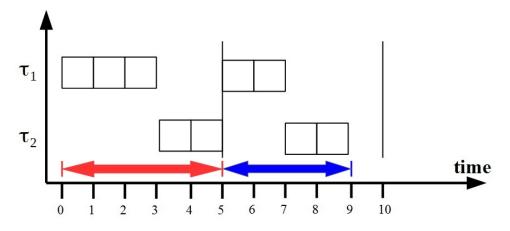

In the real-time systems, the features of every periodic task  $\tau_i$  in timing domain are depicted in Figure 3.1, where

Figure 3.1: The timeline of one periodic task's feature

- 1. **Release.** The time at which task requests for execution; it also means the time at which task becomes ready for execution.

- 2. Execution time. The total amount of processing time necessary for execution without interruption.

- 3. Deadline. The maximum time within which task must complete its execution.

- 4. Start. The time at which system starts to run the task.

- 5. Finish. The time at which system completes the execution of task.

- 6. **Response time.** The total amount of time for system to respond to request of task, i.e., the interval between release and finis time.

- 7. **Period.** The interval between task's consecutive release times, i.e., the request rate of execution.

For ease of timing analysis by mathematics, those features can be denoted by the notations below.

- $\mathbf{r}_{i,j}$  denotes the *release time* of  $j^{th}$  instance of task  $\tau_i$ .

- $\mathbf{s}_{i,j}$  denotes the start time of  $j^{th}$  instance of task  $\tau_i$ .

- $\mathbf{T}_{\mathbf{i}}$  denotes the *period* of task  $\tau_i$ .

- $\mathbf{d}_{\mathbf{i},\mathbf{j}}$  denotes the *absolute deadline* of  $j^{th}$  instance of task  $\tau_i$ .

- $\mathbf{D}_{\mathbf{i}}$  denotes the *relative deadline* of task  $\tau_i$ .

- $\mathbf{R}_{i,j}$  denotes the response time of  $j^{th}$  instance of task  $\tau_i$ .

- $\mathbf{f}_{i,j}$  denotes the *finish/completion time* of  $j^{th}$  instance of task  $\tau_i$ .

- $C_i$  denotes the execution/computation time of task  $\tau_i$ .

- $\mathbf{prt}_i$  denotes the *priority* which is assigned to task  $\tau_i$  in task scheduling.

## 3.2 Rate Monotonic Scheduling Algorithm

This research is based on the *Rate-Monotonic* algorithm as the task scheduling policy. Hence this section is to introduce the idea of it.

Rate-Monotonic (RM) is a fixed-priority preemptive algorithm for periodic tasks [9]. Its rule is to assign priority to every periodic task according to the length of its period. That means the periodic task with shorter period is assigned higher priority. Note that, since the period of every periodic task is constant, every task's priority is decided before execution and does not change during runtime.

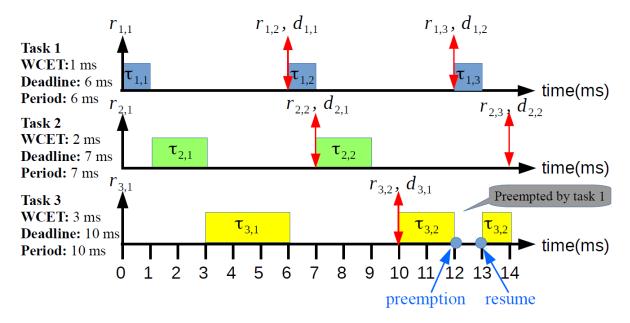

Figure 3.2 is an example of Rate-Monotonic algorithm for scheduling three periodic tasks. Task 1  $\tau_1$  has execution time 1 ms and period 6 ms (=relative deadline). Task 2  $\tau_2$  has execution time 2 ms and period 7 ms. Task 3  $\tau_3$  has execution time 3ms and period 10 ms. According to the RM algorithm,  $\tau_1$  has the highest priority,  $\tau_2$  has middle priority and  $\tau_3$  has the lowest priority. In the execution point 12 ms of Figure 3.2's timeline, the third instance of  $\tau_1$  is released; meanwhile, the second instance of  $\tau_3$  is still executing. In this case, because  $\tau_1$  has higher priority than priority of  $\tau_3$ , the  $\tau_{3,2}$  is suspended from its execution until  $\tau_{1,3}$  finishes, which is called *preemption*.

#### 3.3 The sources and definition of Jitter

In the real-time task scheduling, different instances of a task may vary their computational behaviour in timing domain. Such variation in timing domain is called *jitter*. According to the characterisation of a periodic task  $\tau_i$  defined by [9], there are four types of jitter described below.

• Relative Start Time Jitter. The maximum variation between relative start times of any two consecutive instances, expressed by equation (3.1):

$$RRJ_{i} = \max_{k} |(s_{i,k} - r_{i,k}) - (s_{i,k-1} - r_{i,k-1}))|$$

(3.1)

Figure 3.2: Example of Rate-Monotonic scheduling

• Absolute Start Time Jitter. The maximum variation of relative start times among all instances, expressed by equation (3.2):

$$ARJ_{i} = \max_{k} (s_{i,k} - r_{i,k}) - \min_{k} (s_{i,k} - r_{i,k})$$

(3.2)

• Relative Finish Time Jitter. The maximum variation between response times of any two consecutive instances, expressed by equation (3.3):

$$RFJ_i = \max_k |(f_{i,k} - r_{i,k}) - (f_{i,k-1} - r_{i,k-1}))|$$

(3.3)

• Absolute Finish Time Jitter. The maximum variation of response times among all instances, expressed by equation (3.4):

$$AFJ_{i} = \max_{k} (f_{i,k} - r_{i,k}) - \min_{k} (f_{i,k} - r_{i,k})$$

(3.4)

According to the equation above, it is clear that start time jitter is one part of finish time jitter, hence finish time time jitter is the aim of jitter reduction metrics in this research. Furthermore, finish time jitter of one task is regarded as composition of **execution time variance** and **interference time variance**.

As for execution time variance, its causes can be traced by structure of its source code (described in Chapter 4.3) and target processor's architecture (such as pipline and cache hierarchy) [14, 26]. The former will be the main focus in this study. On the other hand,

interference time variance denotes runtime variation of the total duration in which the task is suspended in *Ready Queue* at any instance, i.e., the preemption duration. As a result, the interference time variance of a task is dominated by the timing behaviour of higher-priority tasks.

The Figure 3.3 shows an example of presence of finish time jitter with three periodic tasks under Rate-Monotonic scheduling<sup>1</sup>. The first periodic task  $\tau_0$  has period  $T_0 = 40$  ms and worst-case execution time  $WCET_0 = 10$  ms, the second task  $\tau_1$  has  $T_1 = 80$  ms and  $WCET_1 = 20$  ms. Last, the task  $\tau_2$  has  $T_2 = 120$  ms and  $WCET_2 = 30$  ms. And thereby those tasks show their priorities in a descend order. Because task  $\tau_0$  gets the highest priority, the variability of its response times among all instances only arises from runtime variation of actual execution time between different instances. On the other hand, the sources of finish time jitters happening to both task  $\tau_1$  and  $\tau_2$  do not only depend on their execution time variance, but also interference time variances which are inherently affected by their higher-priority tasks' jitters.

Figure 3.3: Example of Rate-Monotonic task scheduling

Accordingly, if a task  $\tau_i$  is assigned a lower priority, then the more impacts from higherpriority tasks that the response time of task  $\tau_i$  will be greatly uncertain. Hence the downside of low-priority task in terms of jitter reduction's complexity will be taken into account in proposed methodology of this research.

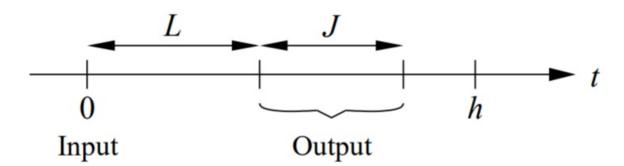

## **3.4** Modelling Timing Attributes of Jitter

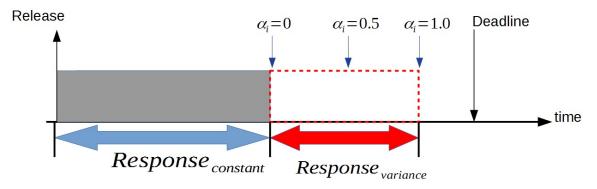

To further quantify the possible finish time jitter of every periodic task regarding its WCET, period and the chosen task scheduling algorithm, Cervin et al. [10,11] introduced the notion of *jitter margin*. It defined the upper and lower bound of input-output jitter<sup>2</sup> of a periodic task in real-time control system, which can help designers to guarantee the system stability of their task scheduling algorithm. In their definition, the input-output delay means the response time of a control task is divided into a **constant delay**,  $L \geq 0$  and **time-varying delay (the jitter)**,  $J_m \geq 0$  shown in Figure 3.4. The minimum possible delay is equal to L, and the maximum possible delay is given by  $L+J_m$ . Therefore, *jitter margin* is defined as the largest variance of input-output delay,  $J_m(L)$ .

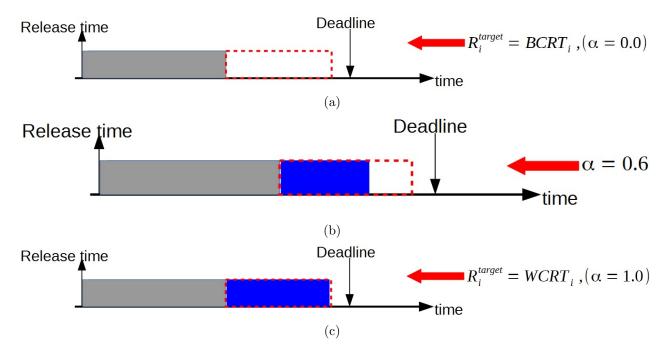

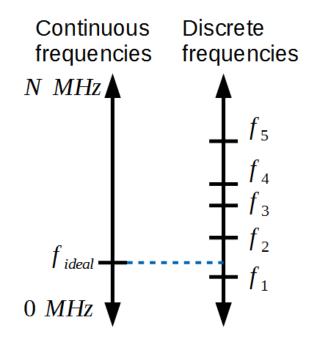

Accordingly, this thesis redefines the viewpoint of original *jitter margin*. That is, every periodic task's execution must take system a constant interval of response time denoted as *constant response*  $R_{constant}$ . Moreover, system would spend an uncertain interval of

<sup>&</sup>lt;sup>1</sup>In Rate-Monotonic scheduling, relative deadline  $D_i$  of one task  $\tau_i$  is equal to its period  $T_i$

<sup>&</sup>lt;sup>2</sup>In the general real-time system's point of view, **input** and **output time** of a control task are equivalent to release and finish time respectively.

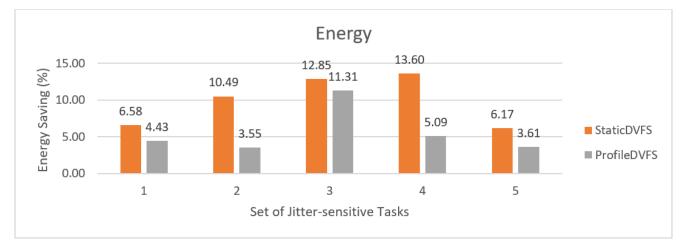

Figure 3.4: The input-output delay in a control task. The symbol h is period of the control task. [11]