| Title                                 | マルチプロセッサのためのリラックスメモリモデルに<br>基づいたSMTソルバによるプログラム検証 |  |  |

|---------------------------------------|--------------------------------------------------|--|--|

| Author(s)                             | Maleehuan, Pattaravut                            |  |  |

| Citation                              |                                                  |  |  |

| Issue Date                            | 2018-09                                          |  |  |

| Туре                                  | Thesis or Dissertation                           |  |  |

| Text version                          | ETD                                              |  |  |

| URL http://hdl.handle.net/10119/15532 |                                                  |  |  |

| Rights                                |                                                  |  |  |

| Description                           | Supervisor:青木 利晃,情報科学研究科,博士                      |  |  |

## Program Verification for Multiprocessors with Relaxed Memory Models using an SMT Solver

Pattaravut Maleehuan

Japan Advanced Institute of Science and Technology

### **Doctoral Dissertation**

## Program Verification for Multiprocessors with Relaxed Memory Models using an SMT Solver

Pattaravut Maleehuan

Supervisor: Toshiaki Aoki

School of Information Science Japan Advanced Institute of Science and Technology

September, 2018

## Abstract

In modern multiprocessors, the consistency of shared memory would be relaxed to increase the computing power; hence, the value of a memory location could be observed as different values at the same time on each execution unit. Note that, term memory model is usually used to determine the semantics of the memory system. In particular, the memory model that relaxes the consistency of the shared memory is usually called relaxed memory model. Consequently, an anomalous result of the concurrent programs could occur on relaxed memory models. Therefore, relaxed memory model is the primary concern to ensure the program correctness.

For ensuring program correctness, the program property is defined as the invariant of the concurrent programs. Due to the relaxed memory models, this research provides an abstraction, called operation structures, of the concurrent programs. The targets of this abstraction are (1) to be sufficient for program verification, and (2) can describe the essence of assembly programs to be verified. Consequently, the program verification approach should be introduced to prove the program property on target relaxed memory model. In particular, this research uses SMT-based program verification approach to ensure the program correctness automatically.

This thesis shows two program verification methods for relaxed memory models. Mainly, the methods rely on the SMT-based program verification approach. In both methods, the behavior of program execution and the program property are encoded into a verification condition represented by a first-order formula; the formula is then used to check every execution satisfies the program property. The primary difference between the proposed methods is the way to abstract the behavior of program executions into the verification condition.

In both methods, the program executions are abstracted symbolically. In particular, the computation of program execution is considered in SMT-based program verification. The first method uses the bounded loop unwinding technique to abstract the symbolic executions. In the bounded method, the loop iterations are unwound systematically within a bound. For the second method, the inductive invariant approach is used instead of loop unwinding. However, the proposed inductive invariant method has seemed to be sound for partial store ordering (PSO) and stronger memory models. For SMT-based program verification, the abstraction of program execution and the program property are encoded regarding the relaxed memory model into a first-order formula. Primarily, the encoded formula is a decidable formula to be solved by an SMT solver automatically. Consequently, the program correctness can be ensured automatically.

In the experiment, an experiment tool was developed, and the Z3 solver is adopted to solve the first-order formula. As a result, the tool can automatically verify the property of the abstraction of concurrent programs on a relaxed memory model. In particular, the abstraction of concurrent programs can represent some essential behaviors of assembly programs. Besides, the bounded method is an under-approximation approach, while the inductive invariant method is an over-approximation approach.

In summary, concurrent assembly programs can be abstracted for ensuring the correctness by our methods. For the bounded method, the program correctness on a relaxed memory model

can be ensured if there is no loop. Otherwise, the method can at least disprove the program property on a relaxed memory model. As for inductive invariant method, the correctness of concurrent program contains loop can be ensured on partial store ordering (PSO).

**Keywords**: Concurrent Program Verification, SMT-based Program Verification, Multiprocessors, Relaxed Memory Model, and Automated Program Verification.

## Acknowledgment

This dissertation could not be completed without supports, comments, and suggestions from many people. Especially, I would like to express my sincere gratitude to my supervisor, Prof Toshiaki Aoki, who always give the valuable comments and suggestions on my research topic. Without his help, its quite hard to imagine how this research can reach this state. In addition to the contents of my research, its almost 5 years that I studied at JAIST and there are several advisories to help me to enjoy living here.

Besides, I would like to express mine sincerely to Dr. Yuki Chiba, former Assistance Professor in our lab, who always help me since I came here until the last day he works at JAIST. Once I was a new student here, my mathematical skill is not good enough for this research. Fortunately, Chiba-sensei always correct my mistakes in my research and advise the right way to express the mathematic expression.

In addition, I thank all members and former members of Aoki-lab who help me to refine my work and discuss with me to improve the contents of the research and the paper that I wrote. Although my research topic is quite different from them, their help also helps me to improve the work in a general way, in which non-specialize researchers can understand.

I also would like to give my special thank to my friends and seniors for their help, suggestions, and encouragements during living in Japan. I also need to give my thanks to Thais friends, whose usually help and make me have a great time in Japan.

Finally, I would like to thank my family for supporting and encouraging me all the time. With out their supports, It's quite hard to go through obstracle of my life.

# Contents

| $\mathbf{A}$ | Abstract |         |                                                  |     |

|--------------|----------|---------|--------------------------------------------------|-----|

| A            | ckno     | wledgn  | nent                                             | iii |

| 1            | Intr     | oducti  | ion                                              | 1   |

|              | 1.1      | Backg   | round and Motivation                             | 1   |

|              | 1.2      | Memo    | ry Models of Multiprocessors                     | 3   |

|              | 1.3      | Progra  | am Verification                                  | 5   |

|              | 1.4      | Object  | tive                                             | 6   |

|              | 1.5      | Thesis  | S Outline                                        | 6   |

| <b>2</b>     | Pre      | limina  | ries                                             | 7   |

|              | 2.1      | Multip  | processors using Shared Memory                   | 7   |

|              |          | 2.1.1   | Hardware Optimization                            | 8   |

|              |          | 2.1.2   | Memory Models                                    | 10  |

|              | 2.2      | Assem   | ably Program                                     | 15  |

|              |          | 2.2.1   | Assembly Instructions                            | 15  |

|              |          | 2.2.2   | Granulity of Assembly Instruction                |     |

|              | 2.3      | Model   | ing Framework                                    | 20  |

|              |          | 2.3.1   | Gharachorloo Framework                           | 21  |

|              |          | 2.3.2   | Herding Cats Framework                           | 24  |

|              | 2.4      | Progra  | am Verification                                  |     |

|              |          | 2.4.1   | Program Property                                 |     |

|              |          | 2.4.2   | Satisfiability Modulo Theories (SMT)             | 28  |

|              | 2.5      | Symbo   | olic Analysis for SMT-based Program Verification | 30  |

|              |          | 2.5.1   | Static Single Assignment (SSA)                   |     |

|              |          | 2.5.2   | Control Flow Analysis                            | 32  |

|              |          | 2.5.3   | Invariant Analysis                               | 33  |

| 3            | Bou      | ınded l | Method for SMT-based Program Verification        | 36  |

|              | 3.1      | Motiva  | ation                                            | 36  |

|              | 3.2      | Abstra  | actions of Assembly Programs                     | 38  |

|              |          | 3.2.1   | Assumptions on Assembly Programs                 | 40  |

|              |          | 3.2.2   | Operation Structure                              | 44  |

|   |      | 3.2.3 Executions of Operation Structures                      |

|---|------|---------------------------------------------------------------|

|   |      | 3.2.4 Semantics of Operation Structures                       |

|   | 3.3  | SMT-based Program Verification                                |

|   |      | 3.3.1 Execution Path                                          |

|   |      | 3.3.2 Bounded Loop Unwinding                                  |

|   |      | 3.3.3 Encoding Scheme                                         |

|   | 3.4  | Conclusions                                                   |

|   |      | 3.4.1 Achievements                                            |

|   |      | 3.4.2 Limitations                                             |

| 4 | Ind  | uctive Invariant Method for SMT-based Program Verification 85 |

|   | 4.1  | Motivation                                                    |

|   | 4.2  | Overview of Inductive Invariant Method                        |

|   |      | 4.2.1 Issues for Program Verification                         |

|   |      | 4.2.2 Overview of Method for Relaxed Memory Models 88         |

|   | 4.3  | Abstractions for Program Execution                            |

|   |      | 4.3.1 Abstractions of Assembly Programs                       |

|   |      | 4.3.2 Execution of Operation Structures                       |

|   | 4.4  | Inductive Invariant Method                                    |

|   |      | 4.4.1 Derivation of Programs containing Loop                  |

|   |      | 4.4.2 Soundness of Inductive Invariant Method                 |

|   | 4.5  | Conclusions                                                   |

|   |      | 4.5.1 Contrary to Bounded Method                              |

|   |      | 4.5.2 Achievements                                            |

|   |      | 4.5.3 Limitations                                             |

| 5 | _    | periment and Discussion 120                                   |

|   | 5.1  | Case Study                                                    |

|   | 5.2  | Experiment                                                    |

|   | 5.3  | Discussion                                                    |

|   |      | 5.3.1 Encoded Formula                                         |

|   |      | 5.3.2 Preciseness                                             |

|   |      | 5.3.3 Expressiveness of Assertion Language                    |

|   |      | 5.3.4 Expressiveness of Operation Structure                   |

|   |      | 5.3.5 Scalability                                             |

| 6 | Rela | ated Work 143                                                 |

|   | 6.1  | Relaxed Memory Models                                         |

|   | 6.2  | Program Verification for Relaxed Memory Models                |

|   | 6.3  | Symbolic Execution Analysis 146                               |

|                           | Conclusion 1 |                             |           |  |  |

|---------------------------|--------------|-----------------------------|-----------|--|--|

|                           | 7.1          | $\operatorname{Advantages}$ | 49        |  |  |

|                           | 7.2          | Limitations                 | 49        |  |  |

|                           | 7.3          | Future Directions           | 150       |  |  |

| Pι                        | ıblic        | tion 1                      | 51        |  |  |

| $\mathbf{B}^{\mathbf{i}}$ | bliog        | aphy 1                      | <b>52</b> |  |  |

# List of Figures

| 1-1<br>1-2 | Spinlock implementation in Linux Kernel                                                      | 2  |

|------------|----------------------------------------------------------------------------------------------|----|

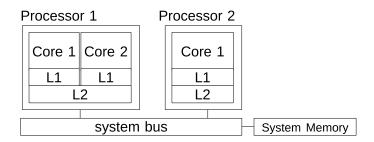

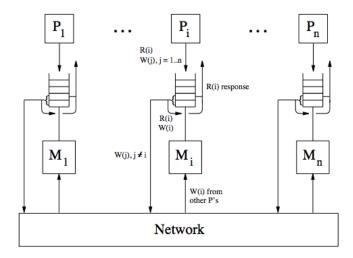

| 2-1        | Overview of an multiprocessor systems                                                        | 8  |

| 2-2        | Example for bypassing read access                                                            | 9  |

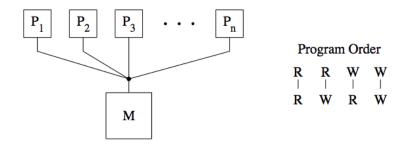

| 2-3        | Conceptual model for sequential consistency model (SC) [Gha95]                               | 10 |

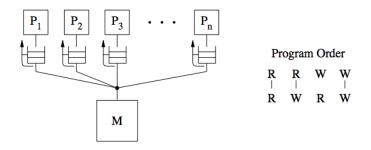

| 2-4        | Conceptual model for total store ordering (TSO)[Gha95]                                       | 12 |

| 2-5        | Store Buffer (SB)                                                                            | 12 |

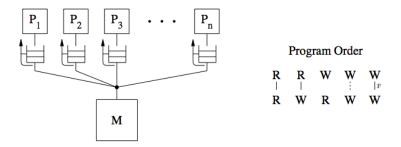

| 2-6        | Conceptual model for partial store ordering (PSO) [Gha95]                                    | 13 |

| 2-7        | Non-FIFO Buffer                                                                              | 13 |

| 2-8        | General model for shared-memory [Gha95]                                                      | 20 |

| 2-9        | Aggressive conditions for SC [Gha95]                                                         | 23 |

| 2-10       |                                                                                              | 24 |

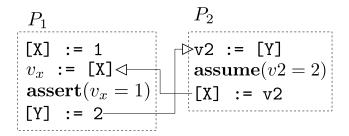

| 2-11       | An abstraction of message passing                                                            | 25 |

|            | SC constraints for Herding cats framework                                                    | 25 |

| 2-13       | SC constraints in cat language                                                               | 26 |

| 2-14       | TSO constraints in cat language                                                              | 26 |

| 2-15       | Transformation of a sequential program for SMT-based program verification                    | 29 |

| 2-16       | An example of control flow graph                                                             | 32 |

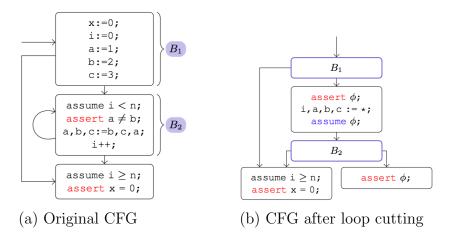

| 2-17       | A program, and CFG obtained using the inductive invariant approach                           |    |

|            | [DHKR11]                                                                                     | 33 |

| 2-18       | A data flow of concurrent programs allowed by POWER                                          | 34 |

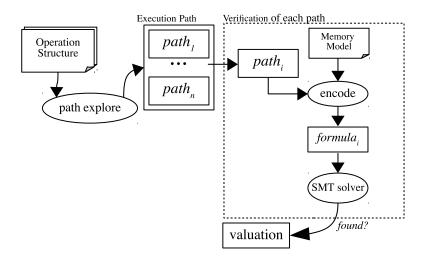

| 3-1        | Overview of Bounded SMT-based Verification                                                   | 37 |

| 3-2        | Representation of an assembly program                                                        | 39 |

| 3-3        | Example of program property                                                                  | 40 |

| 3-4        | Examples of corresponding execution structures for instructions                              | 49 |

| 3-5        | The difference between two statements                                                        | 50 |

| 3-6        | Example of Program Property                                                                  | 50 |

| 3-7        | An operation structure for message passing                                                   | 51 |

| 3-8        | Example operation structures contain synchronize operations                                  | 53 |

| 3-9        | The semantics of an expression                                                               | 56 |

| 3-10       | The semantics of a Boolean expression                                                        | 57 |

|            | Execution path $\pi_1 = (\psi_1^1 \cdot \psi_2^1) \dots \dots \dots \dots \dots \dots \dots$ | 65 |

| 3-12       | The control flow graph for operation structure $\Gamma_2$                                    | 66 |

| 3-14<br>3-15 | Eliminating execution condition                                                 |

|--------------|---------------------------------------------------------------------------------|

|              |                                                                                 |

| 4-1          | Concurrent Programs                                                             |

| 4-2          | Infinite Loop Programs with k reads                                             |

| 4-3          | k iteration with k reads                                                        |

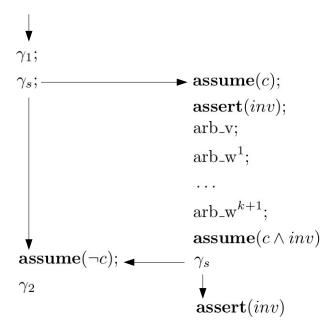

| 4-4          | Overview of Inductive Invariant Method                                          |

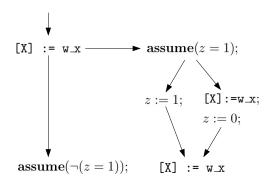

| 4-5          | Control flow graph for considering arbitrary assignments to memory locations 92 |

| 4-6          | Examples of branch behavior                                                     |

| 4-7          | An operation structure for message passing                                      |

| 4-8          | Auxiliary functions                                                             |

| 4-9          | Transform Function $\mathcal{E}$ of Operation Structure                         |

| 4-10         | PSO specification in cat language                                               |

| 5-1          | An operation structure of message passing for inductive invariant method . 121  |

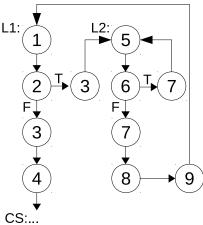

| 5-2          | Mutex Lock mechanism of TOPPERS Spinlock                                        |

| 5-3          | Execution Structures for synchronize instructions                               |

| 5-4          | Spinlock Implementation for SPARC                                               |

| 5-5          | A real PSO bug in an electron microscope software [kno]. This bug caused        |

|              | a \$12 million loss of equipment                                                |

| 5-6          | Simplified programs for Known PSO bug                                           |

| 5-7          | Infinite Program                                                                |

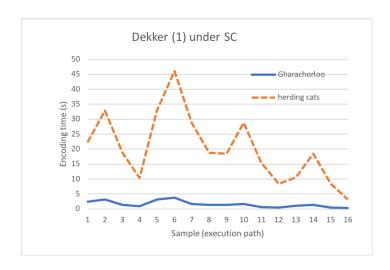

| 5-8          | Encoding time of Dekker's algorithm                                             |

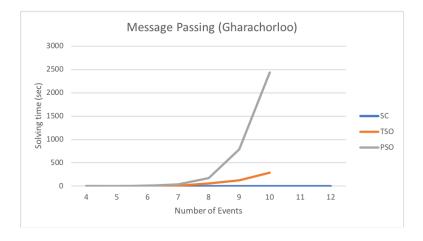

| 5-9          | Solving time of Message passing on Gharachorloo framework                       |

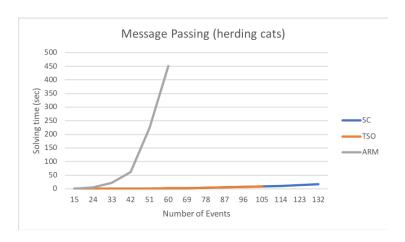

| 5-10         | ÿ - ÿ                                                                           |

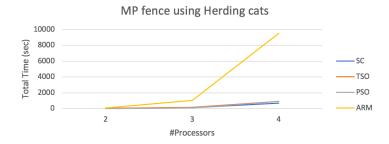

| 5-11         | Experiment on the number of processors                                          |

# List of Tables

| 2.1 | Miscellaneous Instructions                            |

|-----|-------------------------------------------------------|

| 5.1 | Bounded Gharachorloo Framework                        |

| 5.2 | Bounded Herding Cats                                  |

| 5.3 | Inductive Invariant Herding Cats (Runtime)            |

| 5.4 | Inductive Invariant Herding Cats (Violation)          |

| 5.5 | Solving time of 3 execution paths of Dekker under SC  |

| 5.6 | Encoding time of 3 execution paths of Dekker under SC |

| 5.7 | Experiment on the number of processors                |

# List of Definitions

| 2.1  | Definition – Sequential Consistency Model                       | 11 |

|------|-----------------------------------------------------------------|----|

| 3.1  | Definition – Variable                                           | 45 |

| 3.2  | Definition – Expression                                         | 45 |

| 3.3  | Definition – Boolean Expression                                 | 45 |

| 3.4  | Definition – Assignment                                         | 46 |

| 3.5  | Definition – Operation                                          | 46 |

| 3.6  | Definition – Label                                              | 47 |

| 3.7  | Definition – Execution Structure                                | 47 |

| 3.8  | Definition – Instruction Execution                              | 48 |

| 3.9  | Definition – Property Statement                                 | 49 |

|      | Definition – Operation Structure                                | 50 |

|      | Definition – A sequence of operation structure                  | 50 |

|      | Definition – Event                                              | 51 |

|      | Definition – Location of Memory Events                          | 52 |

|      | Definition – Uninterpreted Functions for Memory Events          | 52 |

|      | Definition – Event State                                        | 53 |

|      | Definition – Event Adding Operator                              | 54 |

|      | Definition – Unique Event                                       | 54 |

|      | Definition – Execution State                                    | 55 |

|      | Definition – Execution Units                                    | 55 |

|      | Definition – Register State                                     | 55 |

|      | Definition – Transition of an execution step                    | 56 |

|      | Definition – Evaluation Context of Execution Structure          | 56 |

|      | Definition – Substitutions of Operation Structures              | 57 |

|      | Definition – Generic Substitution                               | 58 |

|      | Definition – Substitution of Execution Units and Register State | 58 |

|      | Definition – Derivation Sequence                                | 62 |

|      | Definition – Semantics Function of Operation Structures         | 62 |

|      | Definition – Execution Path                                     | 63 |

|      | Definition – Unique operation structure                         | 63 |

|      | Definition – Unique branch                                      | 64 |

|      | Definition – The set of execution paths                         | 64 |

| 3.32 | Definition – Control Flow Graph of Operation Structure          | 64 |

| 3.33 | Definition – Path                                                  |  |  | 64  |

|------|--------------------------------------------------------------------|--|--|-----|

| 3.34 | Definition – Dominate                                              |  |  | 65  |

| 3.35 | Definition – Sub-Operation of Memory Event                         |  |  | 74  |

| 3.36 | Definition – Uninterpreted Functions for Gharachorloo framework    |  |  | 75  |

| 3.37 | Definition – Return value function for Gharchorloo framework       |  |  | 76  |

| 3.38 | Definition – Return value predicates for Gharachorloo framework    |  |  | 77  |

| 3.39 | Definition – Basic sets for Herding Cats framework                 |  |  | 79  |

| 4.1  | Definition – Assertion Expression                                  |  |  | 93  |

| 4.2  | Definition – Control Flow Structure                                |  |  | 93  |

| 4.3  | Definition – Symbolic Execution State                              |  |  |     |

| 4.4  | Definition – Symbolic Value                                        |  |  | 95  |

| 4.5  | Definition – Variable State                                        |  |  | 96  |

| 4.6  | Definition – Write Variable State                                  |  |  | 96  |

| 4.7  | Definition – Symbolic Expression                                   |  |  | 96  |

| 4.8  | Definition – State Merging Operator                                |  |  |     |

| 4.9  | Definition – Intermediate State                                    |  |  | 97  |

| 4.10 | Definition – Configuration                                         |  |  | 97  |

| 4.11 | Definition – Condition Extraction Function                         |  |  | 100 |

| 4.12 | Definition – Condition Execution Extraction Fucntion               |  |  | 100 |

| 4.13 | Definition – Counter of Read Events                                |  |  | 101 |

| 4.14 | Definition – Information of Read Event Counters                    |  |  | 101 |

| 4.15 | Definition – Read Counter Function                                 |  |  | 101 |

|      | Definition – Inductive Invariant Transform Function                |  |  |     |

| 4.17 | Definition – Loop Abstraction Transformation                       |  |  | 102 |

|      | Definition – Arbitrary Assignment                                  |  |  |     |

|      | Definition – Assignment Target                                     |  |  |     |

|      | Definition – Arbitrary Write Events                                |  |  |     |

| 4.21 | Definition – Correctness of Symbolic Execution                     |  |  | 105 |

| 4.22 | Definition – Partial Correctness of Operation Structures           |  |  | 105 |

| 4.23 | Definition – Partial Correctness using Indutive Invariant Method . |  |  | 106 |

| 4.24 | Definition – Adding Symbolic Execution State                       |  |  | 107 |

## Chapter 1

## Introduction

## 1.1 Background and Motivation

Nowadays, multi-core processors, or multiprocessor units, are usually adopted in various computer systems. Those processors allow us to execute concurrent programs and/or parallel programs in a system simultaneously to reduce the execution time. In addition to personal computers, multi-core systems are also adopted in various embedded systems, such as automotive systems, recently to serve the high-performance for the system. For parallel programs, each program does not communicate with each other and their tasks can be completed on their own. On the other hand, concurrent programs are not completely independent of each other, and they can access the same memory locations to exchange the program information. In particular, a flaw of concurrent programs executed on embedded systems is a critical issue to be aware of during the software development since the flaw might leads the failure of the whole systems and could risk our lives. Consequently, the correctness of concurrent programs on embedded systems must be ensured.

Besides, multiprocessors using shared memory is also our focus, which executes concurrent programs independently. Recently, most of the modern multiprocessors use various optimization techniques, such as using write buffer. Those techniques intend to reduce the memory latency of memory accesses to shared memory. Note that the effect of the techniques usually appears implicitly to programmers. In particular, modern multiprocessors aggressively use optimization techniques to improve the performance of program execution. As a result, the execution order of the program statements would be out-of-order. In multiprocessors using shared memory, even if the execution order is changed, memory model or memory consistency model is provided to confirm the consistency of shared memory among multiprocessors.

In practice, there is no standard to describe the memory model in a formal way; processors' vender also describes the memory model of the multiprocessors in their ways. This means the behavior of program execution would be different on each memory model. Consequently, the program correctness on each memory model could not be ensured in the same way. For example, if the concurrent programs are correct on a memory model, we cannot conclude the programs are correct on a different memory model. Thus, this

```

static inline void

arch_spin_lock(

arch_spinlock_t *lock){

unsigned long tmp;

static inline void arch_spin_lock

(arch_spinlock_t *lock){

__asm__ __volatile__(

"1: ldstub [%1], %0\n"

unsigned long tmp;

" brnz, pn %0, 2f\n"

__asm__ __volatile__(

5

nop\n"

"1: ldrex %0, [%1] \n"

6

" teq %0, \#0\n"

.subsection 2\n"

"2: ldub [%1], %0\n"

WFE("ne")

" brnz, pt %0, 2b\n"

strexeq %0, %2, [%1]\n"

" nop\n"

tegeq %0, \#0\n"

" bne 1b"

" ba, a, pt %%xcc, 1b\n"

.previous"

"=&r" (tmp)

10

12

: "=&r" (tmp)

: "r" (&lock->lock), "r" (1)

13

: "r" (lock)

: "cc");

12

: "memory");

smp_mb();

15

16 }

14 }

(a) For SPARC processors

(b) For ARM processors

```

Figure 1-1: Spinlock implementation in Linux Kernel

research aims to provide a way to ensure the program correctness on various memory models.

Moreover, this research also considers the program behavior at the hardware-level. In software development, the concurrent program could be implemented in a high-level language. For example, Figure 1-1 shows two implementations of Spinlock mechanism<sup>1</sup> in Linux kernel; each program contains a fragment of assembly instructions to exploit the processor functionality. Instead of considering C program mixing with various assembly syntax, this research considers assembly programs as the target for program verification. In particular, the program behaviors that affected by memory models are considered.

In software development, there are various techniques to verify the correctness of programs, such as providing test cases and code reviewing. However, such methods are not suited for verifying concurrent programs because they are required to highly reliable, and concurrent behavior must be exhaustively checked. *Formal verification* is a rigorous approach that applies to verify the correctness of concurrent programs. Thus, our research adopts the formal verification techniques to ensure the correctness of concurrent programs.

To summarize, this research would like to use formal verification techniques to ensure the correctness of concurrent programs. Besides, *memory model* is the primary concern for ensuring the program correctness on modern multiprocessors. In particular, this research considers the behaviors of concurrent programs affected by memory models; however,

<sup>&</sup>lt;sup>1</sup>Spinlock mechanism is a mutual exclusion algorithm usually used in kernel system, which is a busy-wait mechanism

```

1 L:

2 ldr r1, [y]

3 cmp r1, #1

4 bne L

2 str r1, [x]

3 str r1, [y]

6 assert(r2 = 1)

```

Figure 1-2: Message passing

the considered behaviors are expected to represent the concurrent assembly programs. Consequently, the correctness of the concurrent programs written in an assembly language could be ensured on a memory model.

## 1.2 Memory Models of Multiprocessors

In modern multiprocessor systems using shared memory, there are various mechanisms that affect the behavior of program executions. Those mechanisms could be used to reduce the memory latency to share memory. However, the mechanisms appearing in the systems are too concrete and specific to each processor to be considered in program verification. In general, the multiprocessors usually specify their memory model, or memory consistency model, to guarantee the effect of memory accesses to shared memory.

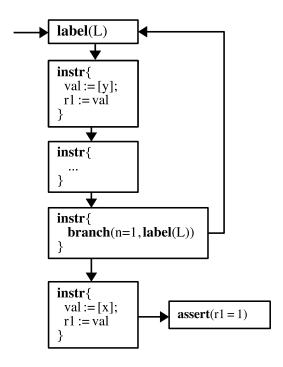

Sequential Consistency Sequential consistency model, denoted as SC, is a standard memory model in which the effect of memory accesses is always as same as the programs executed in a sequential way regardless the mechanisms inside the processors. Figure 1-2 shows message passing programs written in ARM assembly language. The program R1 writes the value 1 to the memory locations [x] and [y] in the order. On the other hand, program R2 reads memory location [Y] until the read value becomes 1, then, reads memory location [X] and writes to register r2. The program property requires the value of register r2 always equals 1 for any program execution. Although multiprocessors allow the latter write access issued by program R1 is completed before the former write access, the multiprocessors using sequential consistency model guarantee the effect of executions is always as same as the behaviors are changed implicitly. This means the program property is always satisfied by any execution from programs R1 and  $R_2$ .

**Relaxed Memory Models** Relaxed Memory Models, or weak memory models, are memory models usually used by modern multiprocessors. Since sequential consistency guarantees the effect of the program executions to be as same as the program executed sequentially, in such model, providing efficient mechanisms to reduce memory latency of the systems using shared-memory would be difficult. Consequently, most of the modern

processors decide to relax the effect of memory accesses to shared memory so as not to restrict themselves to the sequential way of an execution.

Total Store Ordering (TSO) is the relaxed memory model that allows the effect of a read access to appear before a non-conflicting write access. For instance, the following ARM program writes a value to memory location [X] and reads a value from memory location [Y].

```

1 str r1, [X]

2 ldr r2, [Y]

```

In TSO memory model, the read access is allowed to be completed before the prior write access, in particular, the effect of non-conflicting write accesses<sup>2</sup> can occur later than a read access, which would not affect the computation in a single processor. In a practical system, the write access can be stored in a write buffer before completing later, while the read access can be bypassed to read the memory location if there is no conflicting access to the location. However, in multiprocessor systems, the completion of write accesses can appear later to other processors' viewpoint and could cause anomalous effects in the system.

Partial Store Ordering (PSO) is another relaxed memory model which extends TSO memory model to allow the effect of non-conflicting writes to appear out-of-order. For instance, the following ARM program writes a value to memory locations [X] and [Y] in the program order.

```

1 str r1, [X]

2 str r1, [Y]

```

In PSO memory model, the latter write access is allowed to be completed before the prior write access, if the accesses are not in conflict. In a practical system, the write accesses can be stored in a write buffer before completing later, and the buffer could be a non-FIFO buffer, in which the order of issued writes can be out-of-order. By using PSO memory model, the effect can be observed by other processor and the program property could be violated.

Let's consider the programs in Figure 1-2 are executed on TSO and PSO memory models with the program property r2 = 1 for any execution. For TSO memory models, the effect of every execution from the programs is as same as the programs executed on sequential consistency model. On the other hand, PSO memory model allows the write accesses in program R1 to be completed out-of-order. This means if the latter write access in R1 is completed the latter read access in R2 can read the value of the initial value of location [X], which violates the program property r2 = 1. This shows that the effect of each relaxed memory model is different from each other and could violate the program property because of the implicit behavior.

Note that total store ordering (TSO) and partial store ordering (PSO) memory models are conceptual models to illustrate the behavior of a relaxed memory model in a shallow way. In practice, there are various relaxed memory models provided for each processor such as x86-TSO, SPARC-PSO, POWER, and ARM. The practical memory models are

<sup>&</sup>lt;sup>2</sup>Two memory accesses are considered as conflict if one of them is a write access and access to the same memory location.

usually described in the hardware manual and have no standard description. Besides, to exploit their hardware functionality, the behaviors of practical memory models are quite complicated than the conceptual memory models.

### 1.3 Program Verification

Due to the fact that the effect of concurrent programs executed on relaxed memory models is not the same as the program executed on sequential consistency models, the program property could be violated by anomalous executions permitted by relaxed memory models. This means the property to be verified must consider the effect of program execution on target memory model.

Although, in program verification, there are various researches to verify concurrent programs, the verification techniques in most of these cannot be adapted to verify programs on multiprocessor system directly because they do not take relaxed memory models into account. There are several works that provide formal ways to verify program property on specific memory models, such as [Rid10, LV15]. By considering on specific models or specific architectures, the behavior to be verified could be more concrete for their target. Instead of considering on specific memory models, our research would like to provide a verification method for a variety of memory models. In program verification, the effect of program executions is of interested to verify if the program property is preserved.

To realize the effect of program executions for verification, there are frameworks to model the program behavior regarding the specification of memory models. In these frameworks, although there is no standard description of a memory model, they provide their specification styles to determine a valid behavior regarding their abstraction. Given instances of memory accesses occurring in the system, those instances are then considered based on the abstraction of a modeling framework, and the behavior on a memory model must satisfy the memory model specification provided by the framework. Intuitively, we can decide which behavior is valid regarding a memory model using a memory model specification provided by a modeling framework. Note that behavior considered in each framework can be different from each other, such as Gharachorloo [Gha95] represents the behavior in term of execution order, while Alglave [AMT14] represents the behavior in term of the communication of events.

Our program verification adopts the way to abstract the behavior and memory model specifications to realize the effect of program executions for a variety of memory models, in which herding cats framework [AMT14] and a framework provided by Adve and Gharachorloo [Gha95] are considered in our research. In particular, SMT-based program verification is proposed in this research so as to adopt a memory model specification to determine the valid effect on a program execution automatically based on axioms on the instances of memory accesses.

### 1.4 Objective

The objective of this research is to propose a formal program verification method of concurrent programs executed on a multiprocessor system. In particular, the relaxed memory models are also considered in program verification, in which the concurrent programs is considered at the hardware-level. Instead of verifying a high-level language, such as C language, assembly languages are our concern because an assembly instruction is a granule of a statement in a high-level language to interact with a practical processor. In addition, due to a variety of assembly languages for various multiprocessor architectures, an abstraction of assembly instructions is considered for program verification. The abstraction would be proposed to focus on the behavior that is necessary for realizing the effect of the programs executed on a relaxed memory model. This means the assembly instructions that are not related to the computation are not considered, such as interrupt instructions. In program verification, we focus on the properties of programs, in which the safety property on the computations on relaxed memory models is our concern to ensure the program correctness.

#### 1.5 Thesis Outline

First of all, Chapter 2 explains the technical background of this research, which includes (1) the behavior of multiprocessors using shared memory, (2) the assembly instructions considered in this research, (3) frameworks to model the effect of programs executed on a relaxed memory model, and (4) program verification using SMT solver.

Then, Chapter 3 and Chapter 4 describe the methods proposed in this thesis. For Chapter 3, bounded loop unwinding method was described to verify assembly programs using SMT solvers. In particular, the method uses a bound to restrict the number of loop iterations to be unwound. Due to the restriction of the bounded method, Chapter 4 was described to abstract the loop behavior. In the latter method, the most definitions and approaches in the bounded method are adopted for program verification, while some mechanisms are changed to deal with the loop behavior which is a limitation of the bounded method.

After that, Chapter 5 shows the case studies and experiments on the proposed methods, then the evaluation of the methods is also shown. Then, Chapter 6 shows the related works to our research. Chapter 7 concludes the overall of this thesis and discuss the result of our method.

## Chapter 2

## **Preliminaries**

## 2.1 Multiprocessors using Shared Memory

Currently, there are various kinds of processors adopted in computer systems and embedded systems, such as automotive systems. Besides, multi-core processors become more popular to increase the performance of the systems. Although there are various kinds of processors, our research focuses on multiprocessor units that appear to execute program independently, called *multiprocessor systems*.

This research focuses on the concurrent programs that are executed on a multiprocessor system using shared memory. According to Figure 2-1, the system consists of 3 processing units to execute programs simultaneously. If there are concurrent programs, the read and write accesses are going to pass the caches L1, L2 and the system bus to system memory. Note that there are various mechanisms to optimize and/or reduce the memory latency such as write buffer and speculative executions.

An assembly program is assumed to be executed on a processing unit, in which its instructions must be performed in the order defined by the program. In users' point-of-view, a performed instruction is deemed to be completed before the next instructions are performed. However, in practice, various mechanisms are adopted to improve the execution performance, such as using write buffer and read-forwarding mechanisms. Consequently, these mechanisms permit out-of-order executions of memory accesses in a system. Although out-of-order executions can occur, a processor usually provides mechanisms to correct the result of return values of the read accesses to be the same as the sequential execution of memory accesses. For concurrent programs, the order of the read accesses and the write accesses is permitted to be executed out-of-order without the mechanisms of a processor to control the behavior among processing units. Thus, a cache's protocol can be adopted to synchronize the values of a location that can be observed among processors.

In modern multiprocessors, such as ARM and POWER, various complicated mechanisms are used to maximize the performance of their processors. In practice, maintaining the order of memory accesses along with the optimizing mechanisms is quite difficult. Thus, most modern processors usually permit out-of-order executions of memory accesses to occur globally. Accordingly, anomalous return values of the read accesses could be pro-

Figure 2-1: Overview of an multiprocessor systems

duced by concurrent programs. However, to correct the results of concurrent programs, synchronizing instructions are provided regarding a processor to ensure the executions of some fragments of programs.

The term *memory model*, or *memory consistency model* is used to describe the behavior of memory accesses to shared memory in multiprocessor systems. The behavior of programs occurring in a multiprocessor system can be determined by memory model, no matter what optimizing mechanisms are adopted in a practical processor. Note that the memory model of a multiprocessor is usually described in processor architecture's manual, which is described informally and differently to each processor's vendor.

### 2.1.1 Hardware Optimization

#### Out-of-order issuing

In the fetching instruction, normally the instructions are fetched in the order decided by a program counter. Sometimes the next instruction should wait until the necessary registers are available. Instead of waiting, this technique stores the instruction in a reservation station or an instruction buffer. The reservation station will issue an instruction that is required registers are available. That means these behaviors will allow out-of-order issuing of instructions. In some cases that the programs are executed in multiprocessor systems, this behavior is known by only its processor. Therefore, the unexpected results may be produced.

#### Non-blocking read access

In the execution units, the instruction will be performed as micro-operations and memory accesses. As for the read accesses, there are some situations that the read access cannot be performed immediately. The causes maybe read miss in caches or the memory locations is not available yet. Hence, these mechanisms have been introduced to skip such read accesses to perform next micro-operation or memory access. However, this read access will be performed again once the value of the read is needed. This behavior can be realized using the read buffers.

```

1 A = 1

2 B = 1

3 a = A

Program A

Program B

```

Figure 2-2: Example for bypassing read access

#### Bypassing read access

The write accesses usually are put into write buffers. To issue the read access in the program order, the read operation usually has to wait until the previous write accesses already be issued from buffers. In this case, the processor should be stalled itself before performing the next operations. To reduce the stalls, bypassing read access have been introduced. The read access can be performed immediately if and only if there are no write accesses that access to the same address as the read access. Hence, this behavior will cause that a read access may be executed before write accesses specified as earlier operations. In the same processor, this behavior will not produce unexpected results. Nevertheless, in the multi-core systems, the order of some write accesses and read accesses maybe significant order to be considered. For example, let's consider Figure 2-2, we define 'A =1' and 'B=1' as write access, and the remaining are read accesses. Assume that the write access 'A=1' already executed in the shared-memory and 'B=1' is stored in the write buffers. In this case, the read access 'a = A'can read the value 'A = 1' from shared-memory immediately, even if the write access 'B = 1' is not executed yet. In this case, the result of (x, y) is (0, 1) can be happened in the multi-core systems.

#### Read Forwarding

This mechanism also reduces the stalls of that processor by immediately issuing the read access if and only if there is a write access stored in write buffers which access the same memory locations as the read access. However, such return value should be the value from the last write access that appeared in the buffer. Although this mechanism can reduce the stalls in processors, some hardware does not allow this mechanism to be implemented due to it may provide some unexpected results.

#### Non FIFO read/write buffers

Generally, buffers usually act like queues which issue an entity in order as First-In-First-Out(FIFO). In some cases, the earlier read or write accesses cannot be executed yet, because accessing memory location is not available. Moreover, In the case of out-of-order issuing, some accesses should be issued in the program order, but buffers might have previous accesses which should be issued later. Hence, such accesses will be selected to be issued before the previous accesses in the buffers.

Figure 2-3: Conceptual model for sequential consistency model (SC) [Gha95]

#### 2.1.2 Memory Models

Due to the fact that the behavior of a program execution is a significant issue to verify the correctness of concurrent programs, this section would like to explain about memory models, which describes the behaviors of memory accesses among multiprocessors. By considering on memory models, the program verification could be done in an abstraction of the system regardless of the mechanisms used in the practical system.

In practice, the term memory model is used either in a programming language such as C++11 and Java Memory Model (JVM) or at the hardware level, such as SPARC-TSO and x86-TSO. In this research, we focus on the memory models at the hardware level to ensure concurrent assembly programs are correct on a memory model. Thus, this section explains the behavior of memory models at the hardware level.

To explain the behavior of memory models, the conceptual model provided by [Gha95] is adopted as an abstraction of a multiprocessor system to explain the behavior regarding a memory model. Figure 2-3 shows a standard representation for sequential consistency model. There are n processing units,  $P_1, \ldots, P_n$ , sharing a single logical memory M in the conceptual model, which shows the concept for programmer's point-of-view. Read and write accesses are treated as  $\mathbf{R}$  and  $\mathbf{W}$  in a conceptual model. Read access  $\mathbf{R}$  is considered as complete if the return value is determined. Write access  $\mathbf{W}$  is considered as complete once the target location in logical memory M is updated. The program order in the right-side of the figure shows conditions on the read and write accesses issued by programs, in which the completing order must follow the program order if there is a line between them. To determine the return value of a read access, the value must be the last write to the same location that completed before the read completes.

Note that a conceptual model could not be used to determine the complex behavior of modern memory models, such as ARM and POWER. Nevertheless, a conceptual model is used in this section to introduce the simple memory models intuitively. This would help readers to understand some basic behaviors that could occur, which cause a violation in concurrent programs.

#### Sequential Consistency Model

Sequential consistency model, denoted by SC, is a standard memory model that requires the result of programs must be the same as the program executed in a sequential way even if an out-of-order execution occurs. According to 2.1 provided by [Lam97], the constraint is given to implement a system that is a sequential consistency model.

**Definition 2.1** (Sequential Consistency Model). the result of any execution is the same as if operations of all the processors were executed in some sequential order, and the operations of each processor appear in this sequence in the order specified by its program.

This condition considers the side effects of executions that can occur by the behavior of program executions, in which no matter how the processor was implemented.

According to Figure 2-3, the completing order of all read and write accesses must follow the program order, by conditions appearing in the right-side of the figure. However, this conceptual model does not restrict the way to complete each of read and write accesses in a system. This means some processors might put a write access into a write buffer, and then a read access either enforces the conflicting writes to be completed in the order or read the writing value of the last conflicting write in a write buffer, which is the read-forwarding mechanism. However, both of implementations could provide the side effects as same as there are no optimizing mechanisms adopted in a processor.

This is a model which is usually easy for programmers to implement software on top of the model because the execution is always the same as they implement software. Besides, there are various verification techniques that can be used to verify this kind of multiprocessors using sequential consistency models, such as Hoare logic. As the side effect of executions always the same as the programs executed in an interleaving way, thus, program verification in an interleaving behavior is sufficient to ensure the correctness of the system.

However, in practice, this model could provide the low performance of a multiprocessor system. Due to the need for constraints to restrict the executions, the optimizing mechanisms could not be used. Therefore, most of the modern multiprocessors provide a relaxed memory model, or weak memory model, for its processor, which permits anomalous results to occur, but they are acceptable in some programs. By permitting anomalous results, considered as relaxing the execution, the processor can use more optimizing mechanisms to improve the performance of multiprocessors.

#### Relaxed Memory Models

Relaxed memory models are memory models permitting the execution orders not to follow the program order. Although the execution order is permitted to be changed implicitly, there are some restrictions of a relaxed memory model to control the behaviors as an acceptable relaxation permitted by the memory model. In general, each memory model usually provides different constraints for its conceptual system. Primarily, each multiprocessor's provider usually describes the behavior in an informal way and different from each other. However, using a conceptual model, readers could intuitively see how the execution order of programs is changed at an abstract level. Note that relaxed memory models explained in this section are abstracted models, in which the practical systems could provide more details for their memory model to facilitate the processors, such as fence instruction for a pair of write and read accesses.

Figure 2-4: Conceptual model for total store ordering (TSO)[Gha95]

Figure 2-5: Store Buffer (SB)

Total Store Ordering (TSO): Figure 2-4 shows the conceptual model for total store ordering (TSO), which relaxed the order of reads following a write access to be completed out-of-order. This conceptual model is deemed to be same as the model for sequential consistency model. In contrast to the sequential consistency model, this model provides a write buffer between a processor and the logical memory. These buffers store the issued write accesses to reduce the memory latency of the system. Besides, read accesses can read the write value from the last conflicting write access in the buffer if they are issued by the same processor. This means the conflicting reads can be complete before the former write accesses in a processor. In addition, there is no line condition for the pair of write and read accesses in the conceptual model for total store ordering. This means any read access can be completed before a write accesses is completed among processors.

Figure 2-5 shows concurrent programs that the processors write value 1 to the sharememory location [X] and [Y] for processing unit  $P_1$  and  $P_2$ , respectively. These write accesses are supposed to be stored in the write buffers of the processors. Consequently, each read access of each processor, which is non-conflicting accesses, could read the value from the shared memory directly, without any update from a write access. Consequently, the local variables u and v can be 0, which is the initial value of a memory location, in some executions on total store ordering (TSO). In contrast, if the programs are performed on sequential consistency model, the variables v and u are not permitted to be 0 at the same time. Note that total store ordering model adopted in practical processors usually provides fence operations to prevent the changing order between write and read accesses.

Partial Store Ordering (PSO): Figure 2-6 shows the conceptual model for partial store ordering (PSO), which is an extension of TSO memory model. PSO model is quite same as TSO model, excepts the conditions between write accesses. The dotted line appearing in the figure means the conflicting write accesses must be completed in the program order. The line with annotation **F** means non-conflicting write accesses are permitted to be completed out-of-order if there is no fence between them. In an imple-

Figure 2-6: Conceptual model for partial store ordering (PSO) [Gha95]

Figure 2-7: Non-FIFO Buffer

mentation, Non-FIFO write buffers could be used to issue the latter writes that can be completed faster than the former write to be completed in logical memory M.

Figure 2-7 shows concurrent programs that processor  $P_1$  writes value 1 to the location [X] and [Y] in the order, while processor  $P_2$  reads location [Y] and then location [X]. The write accesses are supposed to be stored in a Non-FIFO write buffer, in which the write accesses can be issued from the buffer in either order. Consequently, the first read to location [Y] can read the value 1, while the latter read to location [X] got value 0 in which the write access to [X] is not completed yet. In contrast, if the programs are performed on TSO memory model, the write accesses must be completed following the program order even if they do not conflict with each other. To prevent the out-of-order execution in PSO model, a fence must be added between write accesses to prevent such anomalous behaviors. Obviously, the multiprocessors using PSO model seems to be more efficient than the multiprocessors using TSO model, while there is a trade-off between ease of implementation and efficiency of program execution.

**POWER and ARM**: In modern processors such as ARM and POWER architectures, they provide memory models weaker than TSO and PSO. Intuitively, the completion order of the read accesses is allowed to be out-of-order if there is no dependency between the read accesses. However, as there is no standard description for memory models, it would be difficult to realize the memory behavior on POWER and ARM architectures. There are researches such as [AFI+09, ISS12, MHMS+12, AFI+09, SSA+11] to analyze the behavior of POWER processors. For ARM multiprocessors, the behavior is quite similar to POWER multiprocessors; thus, the intuitive way to consider the behavior on POWER and ARM multiprocessors would be similar.

In POWER and ARM multiprocessors, most of the memory accesses are allowed to be reordered if there is no dependency on them. In POWER multiprocessors, the sequential consistency of memory accesses can be achieved by using sync instruction. However, if sync instruction is added between any instruction, there might be time-consuming which causes the inefficient of program execution.

According to [SSA<sup>+</sup>11], there are dependencies detected by POWER multiprocessors to maintain the completing order on the memory accesses that have such dependencies. There are various kinds of dependencies:

- Address dependency (addr): if the read value of a read access is used as the memory address of the following read access or write access in the program order.

- Data dependency (data): if the following write access uses the read value of a read access in the program order.

- Control dependency (ctrl): if the read value of a read access is used as a branch condition, there is a control dependency from the read access to the following memory access after a branch.

- Control+isync dependency (crtlisync): if there is a control dependency from a read access to a read access after a branch and there is isync instruction after branch and before the second read access in the program order.

For address dependency, the dependency is from a read access to any memory access if the read value is used as the memory address. For example, the following program shows the dependency between two instructions such that register r1 is used as the memory address for the second instruction. Thus, there is an address dependency from the load instruction to store instruction.

```

1li r2, 2

2lwz r1,0(r2)

3 stw r1,0(r1)

```

For data dependency, the dependency is from a read access to a write access if the following write access uses the read value. This dependency also includes the address dependency; however, the behavior that the value to be stored is also considered. For example, the following programs used the value of register r3 as the write value of the write access. Hence, there is a data dependency from the load instruction to the store instruction.

```

1li r1, 1

2li r2, 2

3lwz r3, 0(r1)

4 stw r3, 0(r2)

```

For control dependency, the dependency is from a read access to any memory access if there the read value of the read access affecting the branch condition and the memory access appear after the branch instruction. For example, the following program show the condition of branch instruction bt eq L1 relies on the read value of load instruction lwz r3, O(r1). Thus, there is a control dependency from load instruction to store instruction stw r5, O(r2) appear after the branch instruction.

```

1 li r1, 1

2 li r2, 2

3 lwz r3, 0(r1)

4 cmpwi r3, 1

5 bt eq L1

6 stw r5, 0(r2)

```

For *control+isync dependency*, the dependency is between two read access which similar to the control dependency. In this dependency, the isync should appear before the second read access and after the branch instruction. For example, the following program shows the control+isync dependency between two load instructions.

```

1 li r1, 1

2 li r2, 2

3 lwz r3, 0(r1)

4 cmpwi r3, 1

5 bt eq L1

6 isync

7 stw r5, 0(r2)

```

## 2.2 Assembly Program

In program verification on systems using relaxed memory models, the behavior of read accesses and write accesses to shared memory is the concern. In particular, the target memory models in this research are at the hardware-level, in which assembly programs are considered to ensure the program correctness on relaxed memory model.

An assembly language is a low-level programing language to interact with specific processor architecture. Primarily, a compiler is usually provided for a specific processor to translate the language for facilitating the processor. In the kernel development, there could be various assembly languages used for implementing the same functionality in a kernel, such as Spinlock. Although each assembly language provides different mechanisms to facilitate target processor, there could be similar behaviors that are necessary for program verification on relaxed memory models.

As there are various assembly languages, Section 2.2.1 shows some assembly instructions based on ARM instruction set. This would shows the practical behaviors of assembly program. Then, Section 2.2.2 shows our assumption that an assembly instruction is not performed atomically in the hardware's point-of-view. Consequently, the precise behavior of assembly programs can be considered on relaxed memory models.

### 2.2.1 Assembly Instructions

In practice, there are various assembly instructions to be used for specific processor architectures. In this explanation, ARM instruction sets described in ARMv7 manual [ARM07] are used to show the practical instructions provided for program implementation. First,

the preliminary behavior for assembly instructions is introduced. Then, the explanations of some practical instructions are shown.

#### Preliminary behavior of Assembly Instructions

Conditional execution is introduced for the most of ARM instructions. In this research, the instructions that contain the condition to be considered are called predicated instructions. Intuitively, a condition can be put on an instruction for performing the instruction. In ARM processors, a condition flag appearing in application status program register (ASPR) on the executing processor are used to determine the execution of the instruction. For example, the following program uses compare instruction cmp r1, #1 and save the result to the condition flags in the application state program register (ASPR).

```

1 cmp r1, #0x01

2 streq r1, [0x01]

```

Note that ASPR is used to save the state of the executing program. Then, the store instruction streq r1, [0x01] checks the condition flags whether the condition is satisfied before performing the store instruction in a usual way. Intuitively, the condition denoted by 'eq' intents to check the value of register r1 equals 1. Note that, for other processors, the condition to be checked could be the register directly.

Writing to program counter (PC) is allowed in many data processing ARMv7 instructions. In general, program counter is a register in a processor to determine the instruction to be performed. To manipulate the value of the counter, branch instructions are the basic instruction to change the control flows of the program. Besides, ARMv7 allows other instructions, such as load instructions and data-processing instructions, to change the value of the program counter.

Label in Unified Assembler Language (UAL) syntax can be used in an ARM assembly program. In actual processing, the information to be used in the program must be indicated by the memory address. For instance, the program counter is used to indicate the instruction to be fetched. For the ease of implementation, UAL syntax allows users to use labels for indicating the program information at the specific program locations. Then, such labels would be translated to be the address of the program location using the value relating to the value of program counter. For example, the label would be replaced by [PC-32] which refers to the address before the current instruction.

#### **Branch Instructions**

In practice, there are various branch instructions to be used. The basic branch instruction (b) is to jump the program execution into the target address, which can be described by label in UAL syntax. Normally, this basic branch is used for defining the control flow of a program. The syntax of basic branch instruction in ARMv7 is of the form  $b\langle c \rangle \langle label \rangle$ , where  $\langle c \rangle$  is the condition to be checked and  $\langle label \rangle$  is to indicate the address to be indicated in the program.

In addition to checking the condition flag, compare and branch instruction (cb) can be

used to check the value of the target register before branch to the target address. The syntax of compare and branch instruction is of the form  $\mathtt{cb}\{n\}z\ \langle Rn\rangle\ \langle label\rangle$  where  $\langle Rn\rangle$  is the target register to be checked and  $\{n\}$  can be specified if we need to check the target register not equal to zero. Otherwise, the register equals zero is checked as the condition if there is no  $\{n\}$  in the instruction.

Moreover, ARM assembly language allows users to define subroutines for program implementation. Normally, subroutines would process on the given parameters stored in some registers and return the result in some registers. For the branch instruction to subroutines, branch link instruction (1b) is used to jump to the target label or pc-relative address. In addition to the basic branch instruction (b), the current address before changing is saved in the link register (LR). After the routine is completed, the branch and exchange instruction (bx) is used to jump to the address specified by the target register. For instance, the following program shows the usage of branch to subroutine.

```

1 __main:

2     ldr r1, [0x01]

3     mov r0, #0

4     bl AFUNC     ; Call subroutine AFUNC

5     str r0, [r3]

6     b STOP

7 AFUNC:

8     add r0, r0, r1

9     subs r1, r1, #1

10     bx LR     ; restore the address to PC

11 STOP:

```

#### **Data-Processing Instructions**

This group of instructions is used to manipulate the data in a program. These instructions provide the ways to compute on registers for each processor, such as arithmetic calculation. The following contents show some instructions that are provided for ARMv7 processor architecture.

Standard data-processing instructions provide basic calculations on the registers, such as adding and subtraction. These would compute the program using the basic operator for the data stored in the registers. Besides, there are some compare instructions and test instruction. These instructions provide some decision on the registers and store the result on the condition flag register, which is stored in application program status register (APSR).

Multiplication instructions and divide instructions provide more complicated calculation on the registers. For instance, instruction MUL r2, r1, r0 can be interpreted as the multiplication of r1 and r0 is stored in register r2.

Parallel addition and subtracting instructions provide the functionality to perform addition and subtractions on the values of two registers and write the result to a target register. These instructions are single instruction multiple data (SIMD) instruc-

tions that provide various actions within an instruction.

#### Status Register Access Instruction

In program execution, the application program status register (APSR) is used to indicate the state of programs during program execution, such as the state of condition flag registers. Besides, there are reservation bits in the register that can be used for a special purpose such as disable the interruption behavior of the program. To manipulate the behavior, ones can use MRS and MSR instructions to move the contents between APSR to or from an ARM core register.

#### Load/Store Instructions

Load/store instructions provide the functionality to communicate with a memory location. There is a variety of instructions to load or store the memory locations, such as the data type and the number of accesses to be performed. In the implementation, the data type is the matter in the implementation of an assembly program; thus, the variety of instructions regarding the data type is provided. Besides, ARMv7 architecture also provides the load/store multiple instructions to communicate with multiple memory locations.

**Push and pop instructions** are provided in ARMv7 multiprocessors to realize the stack behavior in the system. In particular, stack pointer register (SP) is used to refer the last register that is put in the stack. Moreover, in ARM multiprocessors, load-exclusive and store-exclusive instructions provides the functionality to facilitate synchronization behavior among multiprocessors. The behavior of load-exclusive and store-exclusive is considered as the behavior of load-link and store-condition in this research.

Load-link is a group of special instructions that are introduced in modern processors, such as ARM and POWER. This instruction is supposed to be used as a pair with store-condition instruction. Intuitively, load-link instruction issued a read access to the memory location and then trigger the processor unit to link the exclusive address, implemented in modern processors, to the target memory location. The exclusive address in a processor unit is used to check whether is there other load-link instructions or a write access to that target address or not.

Store-condition is a group of instructions that is also introduced in modern processors, such as ARM and POWER. The behavior of this kind of instructions is to check the exclusive address still be the same as the address of the instruction or not, and there is no write access that access the target memory location after the load-link instruction, which is used as a pair. If the condition is satisfied, the store-condition instruction issues a write access to the memory location and writes 0 to the result register to let users know that the write access is completed. Otherwise, there is no write access to the system and the instruction writes 1 to the result register to let users know the write access cannot be completed. Note that, in practical processors, the mechanism to link the address could use a cache-line in the processor, which relates more than one memory addresses. This means if there is a non-conflicting write access on the same cache-line, the store-condition

| Instruction                         | Summarize                                       |

|-------------------------------------|-------------------------------------------------|

| Clear Exclusive (clrex)             | Clears the local record of the executing pro-   |

|                                     | cessor that an address has had a request for    |

|                                     | an exclusive access.                            |

| Debug Hint                          | Provides a hint to debug and related systems.   |

| Data Memory Barrier (dmb)           | Ensures the ordering of observations of mem-    |

|                                     | ory accesses                                    |

| Data Synchronization Barrier (dsb)  | Ensures the completion of memory accesses       |

| Instruction Synchronization Barrier | Flushes the pipeline in the processor           |

| (isb)                               |                                                 |

| No Operation (nop)                  | does nothing                                    |

| Send Event (sev) and Wait For Event | wfe instruction permits the executing proces-   |

| (wfe)                               | sor to enter the low-power state until received |

|                                     | an event.                                       |

| Swap (swp)                          | Swaps a word between registers and memory       |

| Wait For Interrupt (wfi)            | wfi permits the executing processor to enter    |

|                                     | the low-power the low-power state until one     |

|                                     | of a number of asynchronous events occurs.      |

Table 2.1: Miscellaneous Instructions

might fail. Obviously, the semantics of these instructions depends on the implementation of a processor.

As the load/store instructions are used to communicate with memory locations, the memory address is used to indicate the target accessing of the instruction. Normally, the address is formed from a based register and an offset. The based register can be any ARM core register, while the offset is of either immediate, register, or scaled register. There are three different ways to indicate the memory address: offset, pre-indexed, and post-indexed.

#### **Miscellaneous Instructions**

In ARM multiprocessors, there are additional instructions such as barrier instructions and clear exclusive instructions. Table 2.1 shows the summarization of instructions in this category. Note that this table shows some of the instructions that can occur in actual implementation.

### 2.2.2 Granulity of Assembly Instruction

An assembly instruction is deemed to be completed atomically, however, the actual computation might not be complete yet. For instance, the write accesses of a write instruction are added to write buffers and the next instruction can be fetched instantly even if the write is not completed. In addition, a single assembly instruction can produce multiple micro-operations to the hardware, such as multiple writes. Thus, this research considers

Figure 2-8: General model for shared-memory [Gha95]

an **operation** as a granule of an assembly instruction and not consider the instruction is completed once the instruction is performed. In particular, the side effects of operations performed on a relaxed memory model are considered in program verification.

Given an assembly instruction, the corresponding operations must cover the behavior of the concerned instruction. In particular, the behavior must be sufficient for program verification on relaxed memory models. For example, read operation would be necessary to represent the behavior of load instruction. Consequently, each of the corresponding operations is then performed by a processor in a defined order regarding the behavior of the instruction.

## 2.3 Modeling Framework

Due to our research focuses on program verification for various memory models, proposing a semantics to each memory model is seemed to be not efficient for the program verification. In particular, the verifying property that we concern focuses on the return values of read accesses which could be produced differently on each memory model. Besides, the way to consider the value relies on the behavior of a memory model, which is described differently for each processor and there is no standard description.