| Title        | Suppression of drain-induced barrier lowering by double-recess overlapped gate structure in normally-off AlGaN-GaN MOSFETs                                                                                                                                                                                                                                                                                                    |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)    | Sato, Taku; Uryu, Kazuya; Okayasu, Junichi;<br>Kimishima, Masayuki; Suzuki, Toshi-kazu                                                                                                                                                                                                                                                                                                                                        |

| Citation     | Applied Physics Letters, 113(6): 063505-1-063505-                                                                                                                                                                                                                                                                                                                                                                             |

| Issue Date   | 2018-08-10                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Туре         | Journal Article                                                                                                                                                                                                                                                                                                                                                                                                               |

| Text version | publisher                                                                                                                                                                                                                                                                                                                                                                                                                     |

| URL          | http://hdl.handle.net/10119/16104                                                                                                                                                                                                                                                                                                                                                                                             |

| Rights       | Copyright 2018 American Institute of Physics. This article may be downloaded for personal use only. Any other use requires prior permission of the author and the American Institute of Physics. The following article appeared in Taku Sato, Kazuya Uryu, Junichi Okayasu, Masayuki Kimishima, and Toshi-kazu Suzuki, Applied Physics Letters, 113(6), 063505 (2018) and may be found at http://dx.doi.org/10.1063/1.5039886 |

| Description  |                                                                                                                                                                                                                                                                                                                                                                                                                               |

## Suppression of drain-induced barrier lowering by double-recess overlapped gate structure in normally-off AlGaN-GaN MOSFETs

Taku Sato, <sup>1,a)</sup> Kazuya Uryu, <sup>1</sup> Junichi Okayasu, <sup>1</sup> Masayuki Kimishima, <sup>1</sup> and Toshi-kazu Suzuki<sup>2,b)</sup>

<sup>1</sup>Advantest Laboratories Ltd., 48-2 Matsubara, Kami-Ayashi, Aoba-ku, Sendai, Miyagi 989-3124, Japan <sup>2</sup>Center for Nano Materials and Technology, Japan Advanced Institute of Science and Technology (JAIST), 1-1 Asahidai, Nomi, Ishikawa 923-1292, Japan

(Received 11 May 2018; accepted 25 July 2018; published online 10 August 2018)

We investigated drain-induced barrier lowering (DIBL) in normally-off AlGaN-GaN metal-oxide-semiconductor field-effect transistors (MOSFETs) with a double-recess overlapped gate structure. It is found that the double-recess overlapped gate structure can suppress DIBL; the threshold voltage is constant without lowering for high drain-source voltages, and sub-threshold characteristics remains excellent. We elucidate the mechanism of the DIBL suppression by considering a local potential in the MOSFETs. In addition, it is also found that the double-recess overlapped gate structure is beneficial for current collapse suppression. *Published by AIP Publishing*. https://doi.org/10.1063/1.5039886

AlGaN-GaN field-effect transistors (FETs)<sup>1</sup> are attractive for use in high-power and high-frequency applications.<sup>2</sup> While AlGaN-GaN FETs in many cases are normally-on devices with a negative threshold voltage, normally-off devices with a positive threshold voltage are highly desirable for fail-safe operations. In order to realize normally-off AlGaN-GaN FETs, several methods have been studied using a thin-AlGaN layer, 3,4 gate recess, 5-13 a p-type (Al)GaN cap layer, 14,15 fluoride plasma treatment, 16 selective electrochemical oxidation, <sup>17</sup> and interface charge engineering. <sup>18</sup> In particular, the gate recess method has been frequently employed, where the AlGaN barrier under the gate is recessetched. There are two categories of the gate recess method: the partial recess method, 5-9 in which a thin AlGaN layer remains in the recess region, and the full recess method, 10-13 in which etching through to the GaN removes the AlGaN barrier completely in the recess region. Although the partial recess method is suitable to obtain normally-off FETs with a low on-resistance and a high drain current, since the remaining AlGaN layer thickness significantly affects the threshold voltage, 19 extremely high precision control of the etching depth is required for threshold voltage control. This is a crucial problem in manufacturing stability. On the other hand, the full recess method, in which the etching depth does not affect the threshold voltage, is advantageous for threshold voltage control and manufacturing stability. The major disadvantage of AlGaN-GaN metal-oxide-semiconductor FETs (MOSFETs) obtained by the full recess method is a high on-resistance caused by a low electron mobility at the oxide/ etched-GaN interface. Thus, in order to realize a low onresistance in fully-recessed AlGaN-GaN MOSFETs, a short gate length is desirable. In general, however, short-gate FETs often suffer from short-channel effects, such as negative threshold voltage shifts and degradation of sub-threshold characteristics owing to drain-induced barrier lowering

(DIBL),<sup>20–22</sup> which are quite serious for normally-off AlGaN-GaN MOSFETs. In order to suppress DIBL, it is effective to relieve the electric field at the gate-drain edge. Lu et al. investigated AlGaN-GaN MOSFETs with a singlerecess overlapped gate structure (SRO), where the gate electrode overlaps both fully-recessed and non-recessed regions, showing a low on-resistance, a high threshold voltage, and a high breakdown voltage.<sup>23</sup> Although DIBL was not studied in Ref. 23, the gate structure is considered to be effective for DIBL suppression due to the fact that the high breakdown voltage is realized by relieving the electric field at the gatedrain edge. In this work, we investigated DIBL in AlGaN-GaN MOSFETs with a double-recess overlapped gate structure (DRO), where the gate electrode overlaps both fullyrecessed and partially-recessed regions, comparing with SRO. As a result, it is found that DRO can more strongly suppress DIBL than SRO. In addition, it is also found that DRO is more beneficial for current collapse suppression.

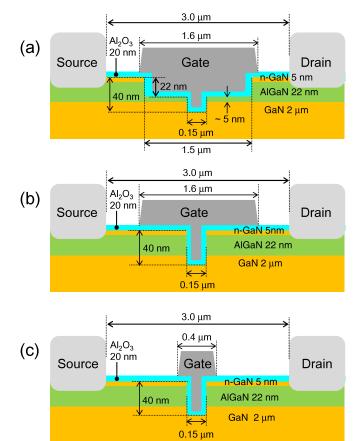

We fabricated short-gate AlGaN-GaN MOSFETs with DRO, SRO, and a reference non-overlapped gate structure (Ref.), whose schematic cross sections are shown in Figs. 1(a)-1(c), respectively. The fabrication process is as follows. For an n-GaN(5 nm)/Al<sub>0.2</sub>Ga<sub>0.8</sub>N(22 nm)/GaN(2  $\mu$ m) heterostructure grown by metal-organic chemical vapor deposition on a semi-insulating SiC substrate, device isolation was achieved by ion implantation. Ohmic recess and following gate recess were carried out by conventional dry etching using BCl<sub>3</sub>/Cl<sub>2</sub> mixture gas. The ohmic recess depth is  $\sim 10$  nm. For the gate recess of DRO, as shown in Fig. 1(a), a fully-recessed region ( $\sim 40 \, \text{nm}$  depth,  $\sim 150 \, \text{nm}$  length) and a partially-recessed region (~22 nm depth, i.e., AlGaN remaining thickness  $\sim 5$  nm,  $\sim 1.5 \,\mu m$  length) are formed, while only a fully-recessed region is formed for the gate recess of SRO and Ref., as shown in Figs. 1(b) and 1(c). By using atomic force microscope, it is confirmed that the designed etching depth profiles are realized. As a gate dielectric, a 20-nm-thick Al<sub>2</sub>O<sub>3</sub> film was deposited by atomic layer deposition using trimethylaluminum and oxygen plasma.

a)Electronic mail: taku.sato@advantest.com

b)Electronic mail: tosikazu@jaist.ac.jp

FIG. 1. Schematic cross sections of AlGaN-GaN MOSFETs with (a) DRO, (b) SRO, and (c) Ref.

Aluminum-based ohmic electrodes were formed on the ohmic recess region after  $Al_2O_3$  film removal, where transmission line model measurements show a contact resistance of  $\sim\!0.3~\Omega$  mm. Finally, Ni gate electrodes were formed on the  $Al_2O_3$  gate insulator, as shown in Figs. 1(a)–1(c), where the gate-length is  $\sim\!150\,\text{nm}$  corresponding to the fully-recessed region.

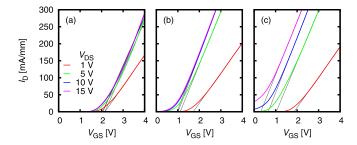

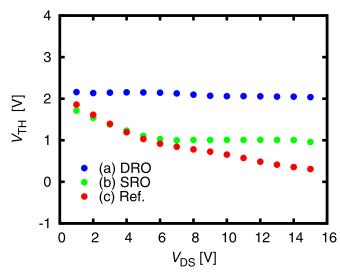

Figure 2 shows linear-scale gate characteristics (drain current  $I_{\rm D}$  vs. gate-source voltage  $V_{\rm GS}$ ) of the AlGaN-GaN MOSFETs with (a) DRO, (b) SRO, and (c) Ref. The drain-source voltages are  $V_{\rm DS}=1,5,10,$  and 15 V and the voltage sweep is  $V_{\rm GS}=+4\to-3$  V. For SRO and Ref., we observe negative threshold voltage shifts owing to DIBL, where the latter exhibits more significant shifts. In contrast, for DRO, DIBL is suppressed; almost no shifts are observed. Figure 3 shows threshold voltages  $V_{\rm TH}$  depending on  $V_{\rm DS}$ . We can confirm no DIBL for DRO in the range of  $V_{\rm DS}=1$ -15 V. On

FIG. 2. Linear-scale gate characteristics ( $I_{\rm D}$ - $V_{\rm GS}$ ) for (a) DRO, (b) SRO, and (c) Ref. The drain-source voltages are  $V_{\rm DS}=1$ , 5, 10, and 15 V, and the voltage sweep is  $V_{\rm GS}=+4\to-3$  V.

FIG. 3. Threshold voltages  $V_{\rm TH}$  depending on  $V_{\rm DS}$  for (a) DRO, (b) SRO, and (c) Ref.

the other hand, for SRO, we find that DIBL occurs in the range of  $V_{\rm DS}=1\text{-}7\,\mathrm{V}$ , but is suppressed in the range of  $V_{\rm DS}>7\,\mathrm{V}$ . For Ref., more significant DIBL occurs in the range of  $V_{\rm DS}=1\text{-}15\,\mathrm{V}$ . Both types of the recess overlapped gate structures, DRO and SRO, are effective for DIBL suppression. However, while SRO does not suppress DIBL in the low  $V_{\rm DS}$  range, DRO completely suppresses DIBL.

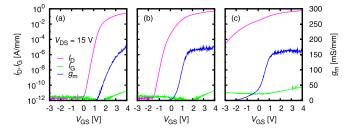

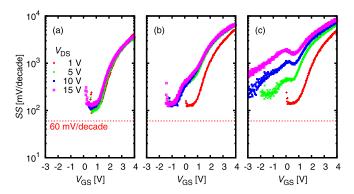

The effect of DIBL suppression for DRO is noticeable in the sub-threshold regime. Figure 4 shows logarithmic-scale gate characteristics for (a) DRO, (b) SRO, and (c) Ref., at  $V_{\rm DS}=15\,\rm V$  under the voltage sweep of  $V_{\rm GS}=+4\to-3\,\rm V$ . Figure 5 shows sub-threshold slope  $SS=\left[\partial(\log I_{\rm D})/\partial V_{\rm GS}\right]^{-1}$  as functions  $V_{\rm GS}$  for (a) DRO, (b) SRO, and (c) Ref., at  $V_{\rm DS}=1$ , 5, 10, and 15 V. For DRO, we observe excellent sub-threshold characteristics and the minimum  $SS\sim90\,\rm mV/$  decade. In contrast, we find poor sub-threshold characteristics for SRO and very poor one for Ref., both resulting in large leakage currents at  $V_{\rm GS}=0\,\rm V$ . The degradation in sub-threshold characteristics due to DIBL is a very serious problem in normally-off devices. DRO is effective for suppressing not only the negative threshold voltage shifts, but also the degradation in sub-threshold characteristics.

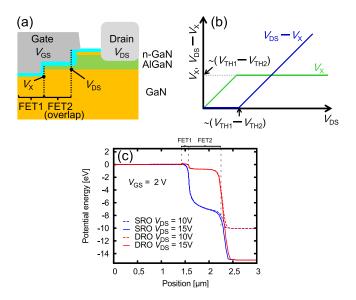

In order to elucidate the mechanism of the DIBL suppression in the DRO MOSFET, we employ a local FET model shown in Fig. 6(a), where local FET1 and FET2 are defined. The FET1 corresponding to the fully-recessed gate region has a local threshold voltage  $V_{\rm TH1}$ , and the FET2 to the partially-recessed overlapped gate region has a local

FIG. 4. Logarithmic-scale gate characteristics  $(I_{\rm D}\text{-}V_{\rm GS})$  for (a) DRO, (b) SRO, and (c) Ref. The drain-source voltage is  $V_{\rm DS}=15$  V, and the voltage sweep is  $V_{\rm GS}=+4\to-3$  V.  $I_{\rm G}$ : gate current,  $g_{\rm m}$ : transconductance.

FIG. 5. Sub-threshold slope characteristics (SS- $V_{\rm GS}$ ) at  $V_{\rm DS}=1,\,5,\,10,$  and 15 V, for (a) DRO, (b) SRO, and (c) Ref.

$V_{\rm TH2}$ . Since  $V_{\rm TH1} > V_{\rm TH2}$ , the total threshold voltage  $V_{\rm TH}$  of the DRO MOSFET is dominated by the local FET1,  $V_{\rm TH}$  $\sim V_{\rm TH1}$ . We define the local potential  $V_{\rm X}$  at the connection point between the FET1 and FET2, where the effective drain-source voltage of the FET1 is  $V_X$  and that of the FET2 is  $V_{\rm DS}-V_{\rm X}$ . It should be noted that the effective gate-source voltage of the FET2 is  $V_{\rm GS}-V_{\rm X}$ . Let us consider the nearthreshold regime  $V_{\rm GS} \sim V_{\rm TH} \sim V_{\rm TH1}$ , where the FET1 is in the near-threshold regime. For a high  $V_{\rm DS}$ , due to current continuity, the FET2 also must be in the near-threshold regime  $V_{\rm GS}-V_{\rm X}\!\sim\!V_{\rm TH1}-V_{\rm X}\!\sim\!V_{\rm TH2}$ ; thus  $V_{\rm X}$  is clamped at  $\sim V_{\rm TH1} - V_{\rm TH2}$ . On the other hand, for a low  $V_{\rm DS} < V_{\rm TH1}$  $-V_{\rm TH2}$ , since the FET2 cannot be in the near-threshold regime, the effective drain-source voltage of the FET2,  $V_{DS}$  $-V_{\rm X}$ , should almost vanish due to current continuity; thus,  $V_{\rm X} \sim V_{\rm DS}$ . In the same way, we can also consider the local FET1 and FET2 for the SRO MOSFET, where the FET2 corresponds to the non-recessed overlapped gate region. As a result, for the DRO and SRO MOSFETs,  $V_X$  and  $V_{DS} - V_X$ depend on  $V_{DS}$  as shown in Fig. 6(b). For  $V_{DS}$  higher than the threshold voltage difference  $V_{\rm TH1} - V_{\rm TH2}$ ,  $V_{\rm X}$  clamped at  $\sim V_{\rm TH1} - V_{\rm TH2}$  makes the FET1 immune to DIBL, leading to

FIG. 6. (a) A local FET model of the DRO MOSFET with local FET1 and FET2. (b) The local potential  $V_{\rm X}$  and  $V_{\rm DS}-V_{\rm X}$  in the near-threshold regime, as functions of  $V_{\rm DS}$ . (c) Simulated potential distributions along the channel of the DRO and SRO MOSFETs at  $V_{\rm DS}=10$  and 15 V.

the DIBL suppression for DRO and SRO. For DRO, DIBL can be more effectively suppressed, owing to the small  $V_{\rm TH1}$  –  $V_{\rm TH2}$  caused by the partial recess in the overlapped gate region. The above mechanism is confirmed by device simulations. Figure 6(c) shows examples of simulated potential distributions along the channel of the DRO and SRO MOSFETs at  $V_{\rm DS}=10$  and 15 V, in which we find that the effective drain-source voltage of the FET1 is clamped. Moreover, by the device simulations, it is confirmed that the potential distribution is not significantly affected by details of the sub-threshold characteristics of the local FETs.

From Fig. 3, the threshold voltage  $V_{\rm TH1}$  without DIBL is  $\sim\!2$  V, which is much smaller than the calculated  $\sim\!10\,V$  by assuming only GaN polarization charges. This difference in  $V_{\rm TH1}$  is attributed to insulator/semiconductor interface fixed charges. For GaN-based MIS devices, in general, interface fixed charges affect the threshold voltage. 24-30 In many cases, positive insulator/semiconductor interface fixed charges tend to be generated and to cancel negative polarization charges. The obtained  $V_{\rm TH1} \sim 2$  V suggests that positive Al<sub>2</sub>O<sub>3</sub>/GaN interface fixed charges with a density of  $\sim 2 \times 10^{13} \, \text{cm}^{-2}$  are generated almost canceling the negative polarization charges of the Ga-face GaN. From the value of  $V_{\rm DS}$  at which DIBL suppression occurs, we obtain the threshold voltage differences  $V_{\rm TH1}$  $-V_{\rm TH2} \sim 1 \, {\rm V}$  and  $\sim 7 \, {\rm V}$  for DRO and SRO, respectively. Therefore, we obtain  $V_{\rm TH2} \sim 1$  V for DRO. For SRO, considering  $V_{\rm TH1} \sim 1~\rm V$  owing to DIBL, we obtain  $V_{\rm TH2} \sim -6~\rm V$ . These values of  $V_{\mathrm{TH2}}$  for DRO and SRO are consistent with separate experiments for partially-recessed and non-recessed AlGaN-GaN MOSFETs.

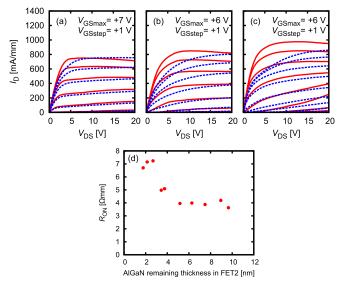

DRO is also beneficial for current collapse suppression. Figures 7(a)–7(c) show pulsed  $I_{\rm D}$ - $V_{\rm DS}$  characteristics for DRO, SRO, and Ref., respectively. The solid (red) and the dashed (blue) curves are obtained by pulsed measurements from the zero-bias condition ( $V_{\rm DS}=0\,{\rm V},\,V_{\rm GS}=0\,{\rm V}$ ) and from a bias condition ( $V_{\rm DS}=+25\,{\rm V},\,V_{\rm GS}=-10\,{\rm V}$ ), respectively. The used pulse-width is 5  $\mu$ s and pulse-cycle is 1 ms.

FIG. 7. Pulsed drain characteristics  $(I_{\rm D}\text{-}V_{\rm DS})$  for (a) DRO, (b) SRO, and (c) Ref. The solid (red) and the dashed (blue) curves are obtained by pulsed measurements from the zero-bias condition  $(V_{\rm DS}=0~{\rm V},~V_{\rm GS}=0~{\rm V})$  and from a bias condition  $(V_{\rm DS}=+25~{\rm V},~V_{\rm GS}=-10~{\rm V})$ , respectively. (d)  $R_{\rm ON}$  as a function of the AlGaN remaining thickness in the FET2.

From the degree of dispersion between the zero-biased and biased characteristics, we find that Ref. and SRO exhibit serious current collapse, even though SRO seems to be slightly effective for current collapse suppression. On the other hand, we find that the current collapse is strongly suppressed for DRO. This shows that DRO is effective to suppress not only DIBL, but also current collapse. The suppressed current collapse for DRO is attributed to small effective drain-source voltages of the local FET1. As in the case of the near-threshold regime described earlier, the effective drain-source voltage of the local FET1 is limited, and the electric field at the gate-drain edge is relieved. This reduces the electron density trapped at the insulator/semiconductor interface, leading to the current collapse suppression. From Figs. 7(a)–7(c), we obtain on-resistances  $R_{\rm ON} \sim 4$ ,  $\sim 4$ , and  $\sim 3 \Omega$  mm for DRO, SRO, and Ref., respectively. The DRO MOSFET exhibits a rather low on-resistance  $\sim 4 \Omega$  mm and a moderate threshold voltage  $\sim$  2 V, compared with reported fully-recessed AlGaN-GaN MOSFETs. 10-13,23 For the DRO MOSFETs, there is a trade-off between a low  $R_{ON}$  and DIBL/current collapse suppression. A deep recess etching in the FET2, which is beneficial for DIBL/current collapse suppression, may lead to a high  $R_{ON}$ , when the resistance of the FET2 is increased by the etching. In fact, Fig. 7(d) shows  $R_{\rm ON}$  as a function of the AlGaN remaining thickness in the FET2 obtained by separate experiments, where  $R_{ON}$  rapidly increases for the thicknesses  $\lesssim 4\,\mathrm{nm}$ , while the employed thickness  $\sim 5 \, \text{nm}$  in this work can avoid such increase in  $R_{\rm ON}$ . On the other hand, if we employ a larger AlGaN remaining thickness, the DIBL/current collapse suppression will become weak. However, our separate experiments show that the DIBL suppression is not significantly deteriorated for the thickness  $\lesssim 9 \, \text{nm}$ , suggesting that precise control of the etching depth is not so required for the DRO MOSFETs. It should be noted that a large voltage is applied to the FET2 in the DRO MOSFET under a high  $V_{DS}$ . Therefore, for very high voltage applications, it is necessary to employ technologies to enhance the operation voltage of the FET2, such as field-plate for the FET2.

In summary, we investigated DIBL in normally-off AlGaN-GaN MOSFETs with DRO, compared with SRO. It is found that DRO can more strongly suppress DIBL than SRO. We elucidate the mechanism of the DIBL suppression; DRO is effective for the DIBL suppression owing to the small threshold voltage difference between the local FETs, caused by the partial recess in the overlapped gate region. In addition, we found that DRO is also beneficial for current collapse suppression.

A part of this work was supported by JSPS KAKENHI Grant No. 15K13348 and Nanotechnology Platform Program (Molecule and Material Synthesis) of the Ministry of Education, Culture, Sports, Science and Technology (MEXT), Japan.

- <sup>1</sup>M. Khan, A. Bhattarai, J. Kuznia, and D. Olson, Appl. Phys. Lett. **63**, 1214 (1993).

- <sup>2</sup>U. K. Mishra, P. Parikh, and Y.-F. Wu, Proc. IEEE **90**, 1022 (2002).

- <sup>3</sup>M. A. Khan, Q. Chen, C. Sun, J. Yang, M. Blasingame, M. Shur, and H. Park, Appl. Phys. Lett. **68**, 514 (1996).

- <sup>4</sup>A. Endoh, Y. Yamashita, K. Ikeda, M. Higashiwaki, K. Hikosaka, T. Matsui, S. Hiyamizu, and T. Mimura, Jpn. J. Appl. Phys., Part 1 **43**, 2255 (2004).

- <sup>5</sup>J. S. Moon, D. Wong, T. Hussain, M. Micovic, P. Deelman, M. Hu, M. Antcliffe, C. Ngo, P. Hashimoto, and L. McCray, in *Proceedings of the 60th Device Research Conference* (IEEE, 2002), pp. 23–24.

- <sup>6</sup>V. Kumar, A. Kuliev, T. Tanaka, Y. Otoki, and I. Adesida, Electron. Lett. 39, 1758 (2003).

- <sup>7</sup>W. Lanford, T. Tanaka, Y. Otoki, and I. Adesida, Electron. Lett. 41, 449 (2005).

- <sup>8</sup>M. Kanamura, T. Ohki, T. Kikkawa, K. Imanishi, T. Imada, A. Yamada, and N. Hara, IEEE Electron Device Lett. 31, 189 (2010).

- <sup>9</sup>N. Maeda, M. Hiroki, S. Sasaki, and Y. Harada, Appl. Phys. Express 5, 084201 (2012).

- <sup>10</sup>T. Oka and T. Nozawa, IEEE Electron Device Lett. **29**, 668 (2008).

- <sup>11</sup>W. Huang, Z. Li, T. Chow, Y. Niiyama, T. Nomura, and S. Yoshida, in Proceedings of the International Symposium on Power Semiconductor Devices and ICs (IEEE, 2008), pp. 295–298.

- <sup>12</sup>Y. Wang, M. Wang, B. Xie, C. P. Wen, J. Wang, Y. Hao, W. Wu, K. J. Chen, and B. Shen, IEEE Electron Device Lett. 34, 1370 (2013).

- <sup>13</sup>S. Liu, S. Yang, Z. Tang, Q. Jiang, C. Liu, M. Wang, and K. J. Chen, IEEE Electron Device Lett. 35, 723 (2014).

- <sup>14</sup>X. Hu, G. Simin, J. Yang, M. A. Khan, R. Gaska, and M. Shur, Electron. Lett. 36, 753 (2000).

- <sup>15</sup>Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihara, T. Ueda, T. Tanaka, and D. Ueda, IEEE Trans. Electron Devices 54, 3393 (2007).

- <sup>16</sup>Y. Cai, Y. Zhou, K. J. Chen, and K. M. Lau, IEEE Electron Device Lett. 26, 435 (2005).

- <sup>17</sup>N. Harada, Y. Hori, N. Azumaishi, K. Ohi, and T. Hashizume, Appl. Phys. Express 4, 021002 (2011).

- <sup>18</sup>M. Blaho, D. Gregušová, Š. Haščík, M. Jurkovič, M. Ťapajna, K. Fröhlich, J. Dérer, J.-F. Carlin, N. Grandjean, and J. Kuzmík, Phys. Status Solidi A 212, 1086 (2015).

- <sup>19</sup>Z. Wang, B. Zhang, W. Chen, and Z. Li, IEEE Trans. Electron Devices 60, 1607 (2013).

- <sup>20</sup>U. Singisetti, M. H. Wong, S. Dasgupta, Nidhi, B. Swenson, B. J. Thibeault, J. S. Speck, and U. K. Mishra, IEEE Electron Device Lett. 32, 137 (2011).

- <sup>21</sup>P. S. Park and S. Rajan, IEEE Trans. Electron Devices **58**, 704 (2011).

- <sup>22</sup>Z. Guo and T. P. Chow, Phys. Status Solidi A 212, 1137 (2015).

- <sup>23</sup>B. Lu, O. I. Saadat, and T. Palacios, IEEE Electron Device Lett. 31, 990 (2010).

- <sup>24</sup>S. Ganguly, J. Verma, G. Li, T. Zimmermann, H. Xing, and D. Jena, Appl. Phys. Lett. **99**, 193504 (2011).

- <sup>25</sup>M. Esposto, S. Krishnamoorthy, D. N. Nath, S. Bajaj, T.-H. Hung, and S. Rajan, Appl. Phys. Lett. **99**, 133503 (2011).

- <sup>26</sup>M. Ťapajna and J. Kuzmík, Appl. Phys. Lett. **100**, 113509 (2012).

- <sup>27</sup>T.-H. Hung, S. Krishnamoorthy, M. Esposto, D. N. Nath, P. S. Park, and S. Rajan, Appl. Phys. Lett. **102**, 072105 (2013).

- <sup>28</sup>M. Ťapajna, M. Jurkovič, L. Válik, Š. Haščík, D. Gregušová, F. Brunner, E.-M. Cho, T. Hashizume, and J. Kuzmík, J. Appl. Phys. 116, 104501 (2014)

- <sup>29</sup>M. Matys, B. Adamowicz, A. Domanowska, A. Michalewicz, R. Stoklas, M. Akazawa, Z. Yatabe, and T. Hashizume, J. Appl. Phys. **120**, 225305 (2016).

- <sup>30</sup>S. P. Le, D. D. Nguyen, and T. Suzuki, J. Appl. Phys. **123**, 034504 (2018).