## **JAIST Repository**

https://dspace.jaist.ac.jp/

| Title        | Automatic Stub Generation for Dynamic Symbolic Execution of ARM binary |  |  |

|--------------|------------------------------------------------------------------------|--|--|

| Author(s)    | Nguyen, Thi Van Anh                                                    |  |  |

| Citation     |                                                                        |  |  |

| Issue Date   | 2021-09                                                                |  |  |

| Туре         | Thesis or Dissertation                                                 |  |  |

| Text version | author                                                                 |  |  |

| URL          | http://hdl.handle.net/10119/17543                                      |  |  |

| Rights       |                                                                        |  |  |

| Description  | Supervisor:小川 瑞史, 先端科学技術研究科, 修士(情報科学)                                  |  |  |

#### Master's Thesis

# Automatic Stub Generation for Dynamic Symbolic Execution of ARM binary

1910407 Nguyen Thi Van Anh

Supervisor Prof. Mizuhito Ogawa Main Examiner Prof. Mizuhito Ogawa Examiners Prof. Satoshi Tojo

> Associate Prof. Nao Hirokawa Associate Prof. Daisuke Ishii

Graduate School of Advanced Science and Technology Japan Advanced Institute of Science and Technology (Information Science)

September, 2021

#### Abstract

In a recent survey, it is reported that the number of IoT attacks in 2020 has been rose to 66% compared to the previous year. Due to the vast number of IoT devices with weak authentication and lack of security protection ability, IoT devices have become easy targets for exploitation. With the rapidly increasing number of IoT devices, even when the computing power of each IoT device is low, they can collaborate for making large-scale attacks (e.g., DDoS, and crypto-jacking). Therefore dealing with IoT malware has become more and more urgent and necessary. There are many existing approaches for analyzing malware including static analysis and dynamic analysis. However, disassemblers can be easily cheated by obfuscation techniques, and dynamic analyses can be detected and prevented by VM awareness, anti-debugging, and trigger-based behavior. To bypass obfuscation techniques, especially for indirect jump resolution, it is necessary to apply Dynamic Symbolic Execution to reconstruct malware execution trace.

ARM is a processor family, which is most popularly used for IoT devices. In previous work, a DSE tool for ARM Cortex-M - CORANA was preliminarily built by extracting ARM formal semantics from natural language descriptions. However, malware frequently runs in both user mode and kernel mode, and they also connect with other external systems (e.g, C&C servers, or other end-user devices). The result of the external calls might affect deeply the analysis, especially in the presence of anti-debugging or trigger-based code. An approach is to prepare API Stub of system calls to interact with the external environment. Automatically generation of API Stub can help the symbolic execution engine produce meaningful execution traces while reducing the cost of manual API implementation.

We target ARM on Linux, where its API specification is available in the Linux Manual Page. This thesis proposed an approach to systematically generate Linux API Stub from the C library function interface description. For each library function, first, we apply pattern matching to retrieve the information on its name, parameters, and return type. After that, we using predefined type conversion rules to statically decided on the types of parameters. Then, three kinds of Java classes of the target function which are structure definition class, interface-mapped class, and API Stub class are generated. By 1659 collected API descriptions, we are able to produce 1129 API Stubs and 267 structure definition classes. We also proposed using serialization to handle the execution of multiple processes. To demonstrate the ability of CORANA after adding the generated API Stubs to support external calls (CORANA/API), we performed a detailed analysis on a Mirai sample using the tool. The result shows that CORANA/API is able to trace real-world IoT malware samples and is resilient against several obfuscation techniques, which overcomes the existing DSE tools, e.g., angr.

Keywords— IoT malware, malware analysis, Dynamic Symbolic Execution, ARM Cortex-M

## Contents

| Li         | st of          | Figure  | es                                                       | 3  |

|------------|----------------|---------|----------------------------------------------------------|----|

| $_{ m Li}$ | st of          | Tables  | 5                                                        | C  |

| 1          | Intr           | oducti  | on                                                       | 1  |

| 2          | <b>DSI</b> 2.1 |         | Malware Analysis are analysis difficulties               | 8  |

|            |                | 2.1.1   | Obfuscation technique                                    | 8  |

|            |                | 2.1.2   | Infection technique                                      | 11 |

|            | 2.2            | Dynan   | nic Symbolic Execution                                   | 13 |

|            | 2.3            | SE too  | ols for binary                                           | 15 |

|            |                | 2.3.1   | MAYHEM                                                   | 15 |

|            |                | 2.3.2   | KLEE-MC                                                  | 15 |

|            |                | 2.3.3   | angr                                                     | 16 |

|            |                | 2.3.4   | BINSEC/SE                                                | 17 |

| 3          | DSI            | E for A | ARM Instructions: CORANA                                 | 19 |

| Ū          | 3.1            |         | l semantics of ARM                                       |    |

|            | 3.2            |         | condition generation                                     |    |

|            |                | 3.2.1   | Conditional branching in ARM                             |    |

|            |                | 3.2.2   | Path condition in ARM                                    |    |

|            | 3.3            | -       |                                                          | 26 |

|            | 0.0            | 3.3.1   | Semantic extraction from natural language specifications |    |

|            |                | 3.3.2   | CORANA architecture                                      |    |

|            | Баг            | - A - T |                                                          |    |

| 4          |                |         | •                                                        | 30 |

|            | 4.1            |         | v                                                        | 30 |

|            | 4.2            |         | nal call template in JNA                                 |    |

|            | 4.3            |         | nal call handling                                        |    |

|            | 4.4            | Multip  | ble process handling                                     | 37 |

| 5          | Ext            | ernal o | call specification extraction                            | 40 |

|            | 5.1            | API el  | lements extraction                                       | 40 |

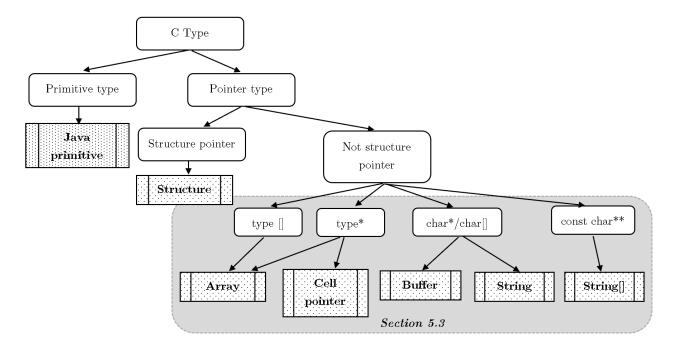

|              | 5.2 | Type conversion                                 | 41        |

|--------------|-----|-------------------------------------------------|-----------|

|              | 5.3 | Deciding on pointer types for parameters        |           |

| 6            | Aut | comated API Stub generation                     | <b>46</b> |

|              | 6.1 | Generated Java Classes                          | 46        |

|              |     | 6.1.1 Structure definition class                | 46        |

|              |     | 6.1.2 C library interface class                 | 47        |

|              |     |                                                 | 48        |

|              | 6.2 |                                                 | 49        |

|              |     | 6.2.1 Structure class generation                | 49        |

|              |     | 6.2.2 Library interface-mapped class generation | 50        |

|              |     | 6.2.3 API stubs generation                      | 50        |

| 7            | Exp | periments                                       | 54        |

|              | 7.1 | CORANA/API performance                          | 54        |

|              |     | 7.1.1 Generated API Stubs                       |           |

|              |     | 7.1.2 Trace generation performance              |           |

|              | 7.2 | Analysis of Mirai malware sample                |           |

| 8            | Con | nclusion                                        | 62        |

|              | 8.1 | Conclusion and Current limitation               | 62        |

|              | 8.2 | Future works                                    |           |

| $\mathbf{A}$ | Exe | ecution trace of Mirai                          | 66        |

# List of Figures

| 2.1 | Example of anti-debugging techniques                            | 8  |

|-----|-----------------------------------------------------------------|----|

| 2.2 | Obfuscated code with opaque predicates                          | 9  |

| 2.3 | Example of opaque predicate code                                | 9  |

| 2.4 | Example of indirect jumps                                       | 11 |

| 2.5 | Stack overflows attack                                          | 12 |

| 2.6 | Examples of symbolic execution                                  | 14 |

| 2.7 | Hybrid symbolic execution in MAYHEM                             | 16 |

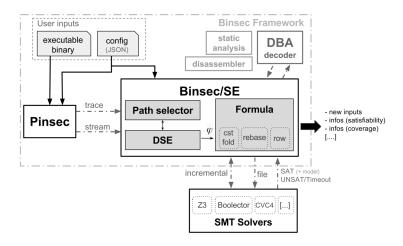

| 2.8 | Architecture of BINSEC/SE                                       | 18 |

| 2.9 | Corresponding DBA instructions of a x86 instruction             | 18 |

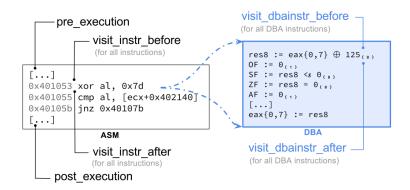

| 3.1 | The semantics transition $t_i$ of the instruction $i$           | 21 |

| 3.2 | Some examples of the operational semantics                      | 21 |

| 3.3 | Path condition in the execution of ARM instructions             | 24 |

| 3.4 | The specification of UASX in ARM Cortex-M7                      | 26 |

| 3.5 | Semantic extraction from NLP specification of ARM               | 27 |

| 3.6 | Semantic interpretation of ARM instruction                      | 28 |

| 3.7 | CORANA Architecture                                             | 28 |

| 4.1 | C Standard Library                                              | 30 |

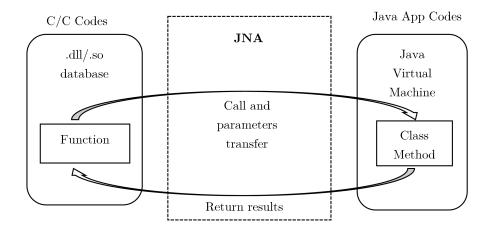

| 4.2 | Java Native Access                                              | 31 |

| 4.3 | Solution for external call handling                             | 36 |

| 4.4 | Memory handling in API Stub                                     | 37 |

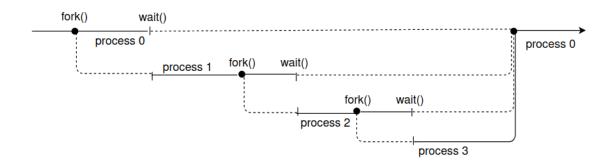

| 4.5 | Execution order of two processes                                | 39 |

| 4.6 | Execution order of multiple processes                           | 39 |

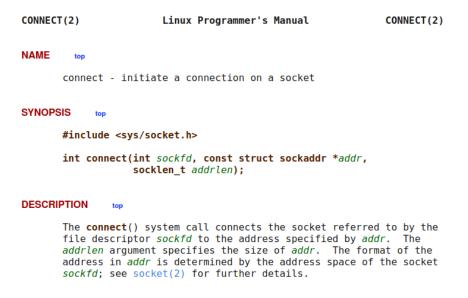

| 5.1 | Description of connect() API from the manpage                   | 40 |

| 5.2 | Type conversion rule from C to JNA                              | 45 |

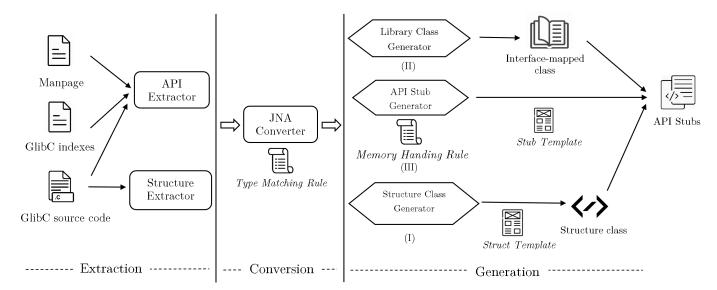

| 6.1 | Generation of structure, library interface and API stub classes | 46 |

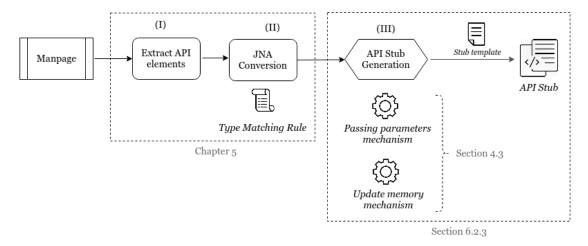

| 6.2 | API Stub generation                                             | 51 |

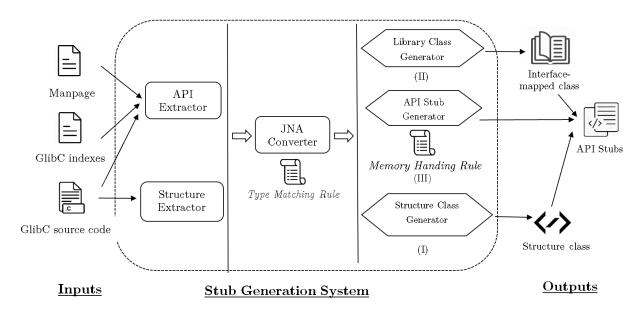

| 7.1 | API Stub generation system                                      | 54 |

| 7.2 | Comparison on external call handling                            | 57 |

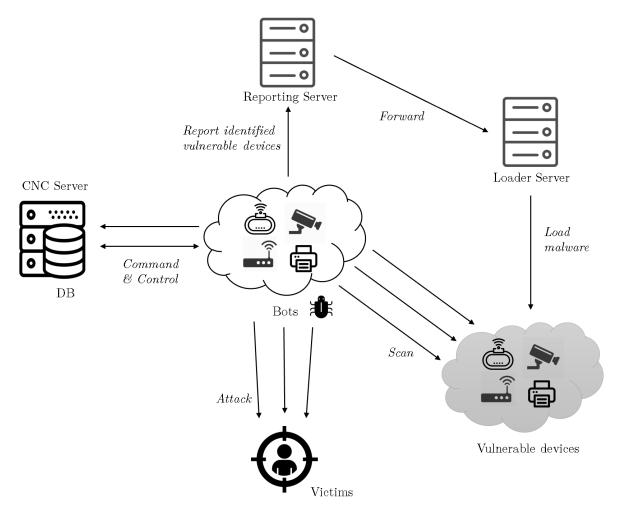

| 7.3 | Mirai logical infrastructure                                    | 59 |

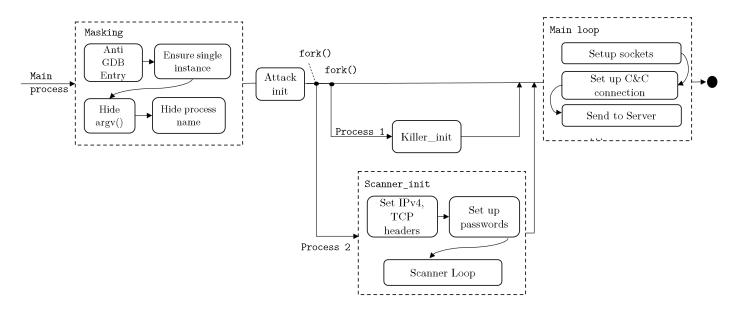

| 7.4 | Mirai execution flow                                            | 60 |

# List of Tables

| 3.1 | ARM Conditional Suffix               | 23 |

|-----|--------------------------------------|----|

| 4.2 | Types supported by JNA library       | 38 |

| 5.1 | Multiple process in IoT malware      | 42 |

|     | Result of execution trace generation |    |

## Chapter 1

## Introduction

Symbolic execution [1] is a classical method in software engineering, especially aimed at test data generation for the control flow coverage. There are lots of tools for high-level programming languages, such as C/C++ and Java are developed. For instance, KLEE [2], CUTE [3], and JPF-SE [4] are just examples from a long list.

Recently, the tools for symbolic execution on binary code gradually increases, e.g., McVeto[5] is an early static symbolic execution example, and from around 2015, several dynamic symbolic execution tools, miasm[6], Mayhem[7], Klee-MC[8], CoDisasm[9], S2E[10], angr[11], and BEPUM[12], become available. They mostly set the first target as x86.

Different from high-level programming languages, binary code has

- no syntax, i.e., no grammar constraints on the order of instructions,

- no distinction on data and code, i.e., everything is a binary sequence, and

- often rigid specification (even described by natural languages).

and its control flow graph is not directly obtained, where the control flow graph of a high-level programming language is obtained for free during the parsing.<sup>1</sup> The need to directly analyze binary code may be on *legacy code*, which will have no available source code, and *malware*. The control flow graph construction, and equivalently the disassembly become a challenge when malware adopts the obfuscation techniques. The syntactic disassembler, e.g., IDApro[15] and CAPSTONE[16], are easily cheated by the obfuscation techniques, especially combined with indirect jumps and self-modification to confuse the next control point. This is also difficult to solve by dynamic analyze when VM awareness, anti-debugging, and/or trigger-based behavior exist. Dynamic symbolic execution on binary code is especially useful for such a challenge [17], [18].

Note that most binary code is not self-contained. The execution environment of binary is on an OS, which has the *privillege hierarchy* and the *API (system library functions)* to request higher privileged tasks and/or common system tasks. We can regrad three levels of binary code actions.

<sup>&</sup>lt;sup>1</sup>For object-oriented languages, an inter-procedural control flow like a call graph requires a *points-to* analysis [13], [14].

- 1. Instruction level, the same level execution, which can be rearded as the state transition.

- 2. System level, the higher privilleged tasks by external function calls.

- 3. Inter-system level, communication with external systems.

Typically, malware consists of three levels of techniques.

- 1. Obfuscation, e.g., indirect jump, self-modification, opaque predicates, antidebugging and trigger-based behavior.

- 2. Infection, e.g., heap/stack overrun, and brute-force attack.

- 3. Malicious action, e.g., information leakage, and remote control.

Among them, the obfuscations without using API calls are at the instruction level execution. The obfuscation techniques with using API calls (e.g., anti-debugging and trigger-based behavior) [19] and the typical infection techniques are at the system level execution. The malicious actions are mostly at the inter-system level via the internet. Some infection techniques to scan surrounding devices are also at the inter-system level.

Another dimension of malware is, either PC malware or IoT malware.

- *PC malware* focuses on mostly x86 with typical OSs, e.g., Windows, Linux, and macOS. To bypass anti-virus protection, it often uses heavy obfuscations, typically introduced by various *packers*.

- *IoT malware* is often naive compared to PC malware. However, the target platforms vary a lot. e.g.,

- MPU (Micro Processor Unit) is mostly 32/64 bits, e.g., x86, ARM Cortex-A, MIPS32/64, MC68000, Sparc, and PowerPC.

- MCU (Micro Controller Unit) is either 4/8/16/32 bits, e.g., ARM Cortex-M,

Z80, PIC, AVR, MSP430 (TI), and various own MCUs (like Runesas, NEC,

Hitachi, and Mitsubishi).

Thus, there are demands to develop binary DSE tools not only on x86, but on various platforms.

For the instruction level, there are two approaches to cover various platforms.

- Use of intermediate assembly language (IAL), e.g., VEX, LLVM, and BAP (used in angr, Klee-MC, and MAYHEM, respectively). Pro is that one can apply a popular disassembler like CAPSTONE to translate into an IAL, but as the opposite side of a coin, Con is that a syntactical disassembler can be easily cheated since the translation is equivalent to disassembly.

- Automatic extraction of formal semantics of each instruction set and automatically generate an individual binary DSE tool.

Our approach is the latter, e.g., BEPUM for x86 [20], CORANA for ARM [21], and SyMIPS [22] for MIPS, based on the observations that

- Malware rarely uses the floating-point instructions. Therefore, we can avoid FPU.

- Malware is often a user-level process and even if it forks processes, mostly they do not communicate with each other, i.e., no synchronization. Therefore, we can simplify the model as a sequential state transition system on the environment model consisting of memory, stack, registers, and flags.

- Each instruction set often has a rigid specification (though in natural language) as a developer's manual. It describes the action of instruction and the flag updates. The former is sometimes associated with the pseudo-code description and the latter is easily processed by the similarity analysis to decide binary actions (i.e., update a flag or not).

For the system level, since DSE cannot trace all the system behavior, we need to model the system environment or the stubs to simulate the system function calls. Of course, we can try manually to prepare a more accurate simulation, but OSs are not only Windows, Linux, and macOS, especially small IoT devices. Even if we restrict ourselves to typical OSs, they already have lots of library functions. For instance, we have found more than thousands of APIs for Windows [23] and Linux (Chapter 7.1). There are three approaches to cover various platforms.

- Klee-MC abstracts the environment as a model [2]. However, this is a quite rough approximation and rarely achieves enough accuracy.

- MAYHEM [7] and angr [11] fuse the concrete execution and symbolic execution of the program by allowing switching between GDB debugger and their symbolic engine.

- BEPUM [12] and Syman [24] prepare the *API Stub* of system calls to execute it in the external environment to obtain an exact snapshot of the environment update. An API Stub requires an interface as a proxy to invoke the native function, retrieves the return value, and updates the environment after the system/library function call.

Our approach is the last. To handle more than thousands of API functions, we follow an automatic generation of API stubs of BEPUM for Windows API [23], but applying to Linux to extend CORANA. It is based on the observation that

- For API stubs, it is enough to collect the interface information (e.g., the type information to avoid errors) instead of the full semantics.

- Similar to the instruction set, OS library functions have rigid specifications (even in natural language) and often follow to the naming convention.

This approach helps the symbolic execution engine produce meaningful execution traces while reducing the cost of manual API implementation.

This thesis proposes an extension CORANA/API of DSE tool CORANA with the API stubs of Linux system functions, i.e.,

- A method for automatic generation of API Stubs for ARM on Linux systems. The same approach can be extended to multiple platforms that run on Linux systems.

- The API generation system is able to produce 1129 API stubs from 1659 collected API descriptions, in addition, are 267 structure definition classes.

With CORANA/API, we analyze IoT malware on ARM/Linux, e.g., Mirai. The result shows that CORANA/API is able to trace real-world IoT malware samples and is resilient against several obfuscation techniques, which overcomes the existing DSE tools, e.g., angr.

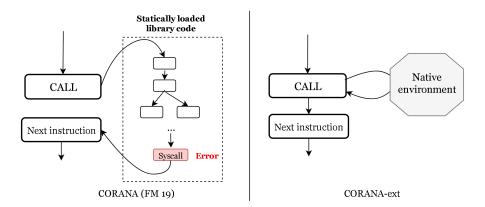

DSE tool CORANA for ARM-Cortex M. ARM is a processor family, which is most popularly used for IoT devices. It has many variations call Cortex (e.g., Cortex-A, Cortex-M, Cortex-R). we focus on the Cortex-M series since it was popular for IoT devices. In previous work, a DSE tool for ARM CortexM - CORANA was preliminarily built by extracting ARM formal semantics from natural language descriptions [21]. It considers the program execution as a sequential user-mode process. However, this is rarely the case in malware when malware frequently runs in both user mode and kernel mode, and they also connect with other external systems (e.g, C&C servers, or other end-user devices). To fully symbolically execute a program, we have to consider three different labels: instruction, external call, and external system. Our prior work in [21] only focused on the dynamic symbolic execution of ARM binaries on the instruction label, making the DSE tool - CORANA encounter problems when the binary contains library function calls and system calls.

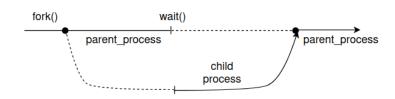

Handling fork. Malware is also frequently used fork() to create several processes. Therefore, a method to generate API Stubs for external calls automatically and handle multiple concurrent processes is much needed to complete the framework for the DSE tool. Our ultimate goal is to propose a method to semi-automatically generate API Stub for ARM on Linux from the description. Moreover, we expect to handle the concurrent processes by serialization with the assumption that processes are executed without overlapping and do not interact with each other.

Linux API specification. We target ARM on Linux, where its API specification is available in the Linux Manual Page. Manually preparing API Stub for each external call to the Linux system is a tedious and time-consuming task. The good news is that we can automatically generate API Stubs because of the following reasons:

• We can invoke a native function in Java by defining the JNA interface that is equivalent to the C library function interface.

- Only information on the C library function interface is sufficient enough to generate API Stub.

- The data transferred on demand between the emulated environment and the actual environment complies with certain conventions (e.g., passing parameters rule, memory allocation rule).

The systematic generation of the Linux API Stub from the C library function interface description proceeds as follows. For each library function, first, we apply pattern matching to retrieve the information on its name, parameters, return type, and other related details. After that, we using predefined type conversion rules to statically decided on the types of function parameters. Then, three kinds of Java classes of the target function which are structure definition class, interface-mapped class, and API Stub class are generated.

#### Related work

Although symbolic execution was introduced in the 70s, it has regained interest since the 2000's due to the advances in constraint solving and the availability of high-performance computing systems. Early works on symbolic execution tools mostly focus on the source code level ([2], [3], [25]). Recently, the target of many symbolic execution tools have been extended to binary code (e.g., McVeto[5], CoDisasm[9], MAYHEM[7], KLEE-MC[8], BE-PUM[12], angr[11], CORANA[21]). Most of them using existing disassemblers or binary lifters to translate binary code to an intermediate binary representation such as LLVM in KLEE-MC, VEX in angr, and BAP in MAYHEM. This approach ensures the symbolic execution tools can analyze binaries from multiple architectures (e.g., x86-64, x86, ARM, MIPS) without preparing execution engines for specific architectures. However, this method does not perform well in the presence of obfuscated code such as indirect jumps, self-modifying code, and over-lapping instructions. To overcome this limitation, some works have directly interpreted binary using a one-step disassembler. McVeto[5] and BE-PUM[12] are both directly apply symbolic execution on x86 binaries. However, McVeto resolves indirect jumps by analyzing the possible candidates statically and use an SMT solver to solve the path constraints to decide the jump destination, whereas BE-PUM decides the destination of indirect jumps by performing concolic testing. The strategy employed by McVeto mostly only works for compiled binary code. On the other hand, BE-PUM execution engine requires a huge effort to implement the binary emulator. Therefore a method to automatically extract the formal semantics of binary instructions is much needed.

Previously, the semantic extraction of the x86 specifications has been investigated to extend BE-PUM[20]. Later, the semantics of ARM and MIPS are automatically extracted to built CORANA[21] and SyMIPS[22], respectively. The extraction of ARM instructions' semantics is more challenging since there exists only natural language descriptions for ARM, without the pseudocode description like x86 and MIPS. Across 6 variants of ARM

Cortex-M, 692 instructions among 1039 collected specifications have been successfully extracted. However, the work in [21] focus on the execution of ARM Cortex-M binaries on the instruction label, without considering the external call label. Therefore in this thesis, we investigate the method to automatically generate API Stub for external calls to complete the DSE tools for ARM binaries run on Linux. Our idea of using API Stub to handle external calls follows the previous work that automatically generates Windows API Stubs for x86 binaries in BE-PUM [23]. There are some fundamental differences between our work and the automatic generation of Windows API Stubs in [23]:

- We focus on the function library calls of ARM binaries run on Linux, instead of Windows API on x86.

- The Windows API descriptions from Microsoft Developer Network (MSDN) are well documented and contains description in natural language for each parameter, while for Linux APIs we can only obtain the function interface and its source code from the GNU C Library.

- To decide variable types in the API Stub, we based on some observed conventions to statically determine the type, instead of using Machine earning techniques since there is no detailed description of the parameters.

- We proposed serialization to deal with multi-processes since multi-processing is a common property of Linux's programs.

#### Thesis Outline

This thesis is composed of 8 chapters. Chapter 1 is the introduction, the next chapters are summarized as follows:

- Chapter 2 presents some obfuscation and infection techniques that are often employed by malware to bypass analysis and detection. It also presents Dynamic Symbolic Execution (concolic testing) for binary analysis and some notable tools for analyzing ARM binaries.

- Chapter 3 introduces the formal semantics of ARM and their extraction process from the natural language description to preliminarily built the Dynamic Symbolic Execution tool for ARM binary on the instruction label CORANA.

- Chapter 4 discusses the interaction between the symbolic execution engine of a program's user process and the OS environment, which is Linux/Unix OS in this case. This chapter presents our choice of approach to handle external calls by implementing API Stubs running the calls in the actual environment. We also handle the execution of multiple processes by serialization.

- Chapter 5 mentions the information extraction of the API description. After extracting API elements from the description, we present a statistical method to

transform and represent those elements (e.g., function name, parameter names, types) in JNA.

- Chapter 6 explains the automated API Stub generation processes.

- Chapter 7 shows the result of the API Stub generation. We analyze the execution trace of CORANA after adding the support for handling external calls and multiple processes against some obfuscated code. Finally, a detailed analysis of Mirai, a variant of IoT malware, is represented.

- Chapter 8 summarize the main contributions of the thesis and its current limitations. After that, several future works are described to show potential directions to improve and extend our study.

## Chapter 2

## DSE for Malware Analysis

## 2.1 Malware analysis difficulties

In this section, we discussed typical obfuscation (e.g., anti-debugging, opaque predicate, self-modification, indirect jump) and infection techniques (e.g., stack overflow, brute-force attack) which are widely employed by malicious software.

#### 2.1.1 Obfuscation technique

Malware often includes various obfuscation techniques to bypass anti-virus software and resit the reverse engineering e.g., indirect jump, opaque predicate, and self-modification for cheating disassemblers and static analysis, and VM awareness, anti-debugging and trigger-based behavior to hide malicious intention from virtual machine or sandbox.

#### Anti-debugging

Anti-debugging techniques are used to check whether the program is running on a debugger and change its behavior if in a debugger. There are several anti-debugging methods such as breakpoint detection which set false breakpoints or checking ptrace.

```

signal(0x11, 1);

signal(5, anti_gdb_entry);

LOCAL_ADDR = util_local_addr();

srv_addr = 2;

C2_addr = inet_addr((int)"VAMPWROTESATORI");

C2_port = 0xF50E;

table_init();

resolve_func = resolve_cnc_addr;

}

void anti_gdb_entry()

{

resolve_func = resolve_cnc_addr;

}

```

Figure 2.1: Example of anti-debugging techniques

Figure 2.1 show the anti-debugging technique employed in Mirai, a popular IoT malware. The malware registers function that returns the real C&C address as a handler for SIGTRAP(5) signal. If debugging is not involved, then the malware normally executes the handler function that was previously registered to obtain the real C&C address. If running

in the debugging environment, fake C&C address will eventually acquired. Another popular technique is debugger detection by using library functions (e.g., isDebuggerPresent() in Windows and ptrace() in Linux). ptrace() can be used since a program can be traced by only one process at a time and almost all debuggers use ptrace() (including GDB).

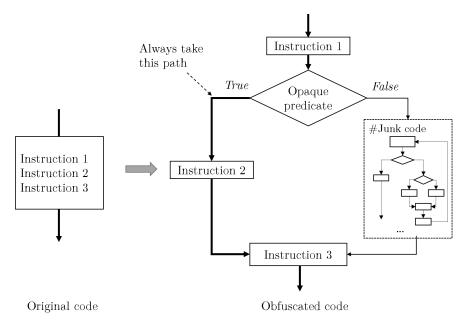

#### Opaque-predicate

Opaque predicates are constant predicates that always true or always false. Opaque predicates can be used to make static analysis more difficult by creating extra control flow, or to add deadcode. Figure 2.3 shows an simple example of opaque predicates, the

Figure 2.2: Obfuscated code with opaque predicates

instructions at label\_1 are never jumped to, but modern disassemblers like IDA Pro or Ghidra cannot determine that property. This leads to inaccurate disassembly.

```

start:

mov r1, #5

cmp r1, #5

beq label_1

label_2:

bx lr

label_1:

mov r3,#0x2e4

```

Figure 2.3: Example of opaque predicate code

#### Self-modification

Self-modifying code [26] is an effective method to hide the real behaviour of the program since only at run-time that the true code is exposed through transformation. Self-

modifying code can be used for protecting property right or concealing malicious behaviour to bypass detection. The key mechanism is that code instructions will be replaced during the program execution. Self-modifying code poses a great challenge for *static analysis*. Two main implementations of self-modifying codes are *packing* and using *self-modifying instruction*.

Originally, *packing* applies compression to make executable size smaller and now it is used to hide the executable content. A packed binary contains a unpacking code section, which decrypts the packed file back to the original file at runtime.

Self-modifying instructions are used in the case where code is considered as data that can be read and written. The program below shows an example of self-modifying code in the C language <sup>1</sup>.

```

#include <stdlib.h>

char code[]= "\xe8\x1f\x00\x00\x00\x58\xc6\x40\x0e\xeb\x43\xc6\x40\x06\xeb"

"\xc6\x40\x07\x08\x50\xf5\x42\x51\x4b\xb8\x01\x00\x00\x00\x00\xbb"

"\x00\x00\x00\x00\xcd\x80\xeb\xdf";

int main() {

int (*func)() = (int (*)()) code;

(int)(*func)();

return EXIT_SUCCESS;}

```

After disassembling this program, the actual opcodes are not shown and hidden in the data section.

| Assembled Code |                                            | Actual Code |                         |

|----------------|--------------------------------------------|-------------|-------------------------|

|                |                                            | call        | 0x24                    |

|                |                                            | pop         | eax                     |

| 401f85         | ENDBR64                                    | mov         | BYTE PTR [eax+0xe],0xeb |

| 401f89         | <pre>push rbp</pre>                        | inc         | ebx                     |

| 401f8a         | mov rbp, rsp                               | mov         | BYTE PTR [eax+0x6],0xeb |

| 401f8d         | <pre>sub rsp,0x10</pre>                    | mov         | BYTE PTR [eax+0x7],0x8  |

| 401f91         | <pre>lea rax,[code]</pre>                  | push        | eax                     |

| 401f98         | <pre>mov qword ptr[RBP+local_10],rax</pre> | cmc         |                         |

| 401f9c         | <pre>mov rdx,qword ptr[RBP+local_10]</pre> | inc         | edx                     |

| 401fa0         | mov eax,0x0                                | push        | ecx                     |

| 401fa5         | call rdx=>code                             | dec         | ebx                     |

| 401fa7         | mov eax,0x0                                | mov         | eax,0x1                 |

|                |                                            | mov         | ebx,0x0                 |

|                |                                            | int         | 0x80                    |

|                |                                            | jmp         | 0x5                     |

$<sup>^{1}</sup> https://github.com/JonathanSalwan/binary-samples/blob/master/anti-disassembler/Linux/self-modifying\_code/self-modifying\_code-i386.c$

#### Indirect jump

Indirect jump stores the jump target in a register or memory instead of a value of the target address. In contrast to a direct jump, which statically points to a location in the program, the target of an indirect jump is dynamically decided. Since static analyses are easily confused by arithmetic operations, it is difficult to resolve indirect jumps using static analyses. At 0x9a50 in the example, the jump destination of the branching instruction bx 1r is not directly specified but depends on the information stored at register 1r.

| 0x9a48 | <b>sub</b> sp, fp, #12           |

|--------|----------------------------------|

| 0x9a4c | ldm sp,fp, sp, lr                |

| 0x9a50 | bx lr                            |

| 0x9a54 | mov ip, sp                       |

| 0x9a58 | <pre>push {fp, ip, lr, pc}</pre> |

|        | - (                              |

Figure 2.4: Example of indirect jumps

We have discussed some popular obfuscation techniques that exist and are frequently used by malicious software. Dynamic symbolic execution can be used to overcome the limitation of both dynamic and static analysis [17], [27].

#### 2.1.2 Infection technique

Many malware aim to exploit software security holes or operating system vulnerabilities to spread and simultaneously infect million of computers. Characterize infection techniques of malware can play an important role in detecting and preventing malicious programs.

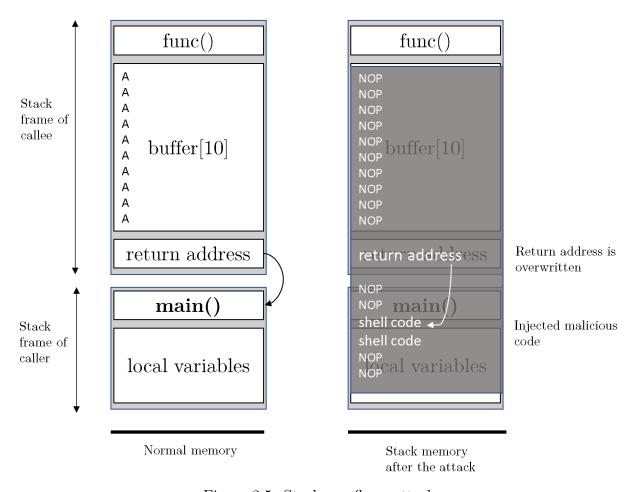

#### Stack (heap) overflow exploitation

Buffer overflow [28] is probably one of the most well-known form of security vulnerability. Overflows take advantage of data stored in the stack or the heap. The goal is to inject instructions into a buffer and overwrite the return address to take the control of the program's execution flow and gain root privileges.

The stack locates a memory area that used as temporary data storage for executing functions and local variables. There are several ways attackers can manipulate the system by exploiting stack buffer overflow. A common technique is overwriting the stack frame return address to continue execution at a location contains injected malicious shell code. This scenario is described in Figure 2.5. When the func() function finishes running, the current function returns to the caller, which is the main() function. To exploit the stack-based vulnerability, the attacker sends to the program some malicious contents consists of: (i) a chain of NOP instructions, (ii) a new return address that points to a specified location and (iii) some malicious code (usually shellcode) in the middle of the NOP chain. The buffer overflow occurs will cause the program jump to the sequence of NOP bytes. The

system ignores the NOP instructions and read the next bytes until encounters the injected shellcode. The shellcode now is executed in the operating system shell, give the attacker full access to the system.

Figure 2.5: Stack overflows attack

In addition to the previously described technique, attackers can also manipulate the system by other techniques such as overwriting and executing an exception handler or more advanced methods.

#### Brute-force attack

Despite of its simplicity, brute-forcing is still one of the most common methods used for attempting to gain access to systems and execute malware especially on IoT devices. Brute-force attacks are trial and error methods guessing the credential of the target system to gain the system's root privilege. Some attacks will loop through large combinations of usernames and passwords until finding the correct one, others will try a predefined set of usernames and passwords on as many systems as possible.

Many malware have used brute-force to attack Windows machines through guessing SMB (Server Message Block) or RDP (Remote Desktop Protocol) passwords, which are connection protocols of Windows computers. One of the most popular ransomware WannaCry exploited the vulnerability of SMB to infect millions of computers.

A brute-force way is simple but incredibly effective to infect IoT devices since most IoT devices still use their default credentials for authentication, or do not use any credentials. IoT devices, such as routers, printers, televisions, and cameras can be found everywhere and have been continuously growing for years. With the weak protection, millions of highly vulnerable devices connecting to the Internet have become easy targets for attackers to be recruited as a part of a botnet to create DDoS attacks or cryptocurrency mining. IoT devices are mostly attacked with the default credentials on SSH, Telnet or HTTP ports. The code below is from the leaked source code of Mirai, a popular IoT malware variant, which shows a part of the predefined username and password set that the malware used to try to gain access control of the target devices.

```

add_auth_entry("\x50\x4D\x4D\x56", "\x5A\x41\x11\x17\x13\x13", 10); // root xc3511

add_auth_entry("\x50\x4D\x4D\x56", "\x54\x4B\x58\x5A\x54", 9); // root vizxv

add_auth_entry("\x50\x4D\x4D\x56", "\x43\x46\x4F\x4B\x4C", 8); // root admin

add_auth_entry("\x43\x46\x4F\x4B\x4C", "\x43\x46\x4F\x4B\x4C", 7); // admin admin

add_auth_entry("\x50\x4D\x4D\x56", "\x1A\x1A\x1A\x1A\x1A\x1A\x1A\x1A", 6); // root 888888

add_auth_entry("\x50\x4D\x4D\x56", "\x5A\x4F\x4A\x46\x4B\x52", 5); // root xmhdipc

add_auth_entry("\x50\x4D\x4D\x56", "\x46\x47\x44\x43\x57", 5); // root default

...

```

Listing 1: The default credentials Mirai used for brute-forcing [29]

## 2.2 Dynamic Symbolic Execution

Symbolic execution [1] is a technique to explore possible states of a program. Instead of running on a specific input as in concrete execution, symbolic execution can take in symbolic values and explore multiple possible paths of a program. For each path, the execution engine maintains a first-order formula that describes the condition satisfied the path.

The interence rule of Hoare Logic is the Hoare triple:

```

\{Precondition\}\ Command\ \{Postcondition\}

```

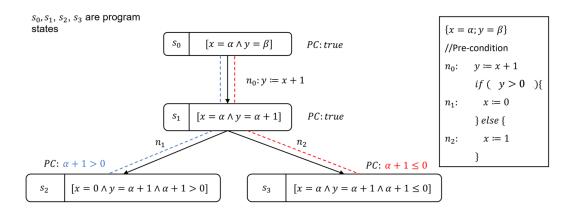

From the Hoare Logic viewpoint, symbolic execution computes new states of the program by applying Hoare logic inference rules on the formulae that describe the states. Consider the following program:

```

\{x = \alpha \land y = \beta\}

\{x = \alpha \land y = \beta\}

y := x + 1;

y := x + 1;

\{x = \alpha \land y = \alpha + 1\}

if (y > 0) {

if (y > 0) {

x := 0;

x := 0;

\{x = 0 \land y = \alpha + 1 \land \alpha + 1 > 0\} (1)

} else {

} else {

x := 1;

x := 1;

\{x = 0 \land y = \alpha + 1 \land \alpha + 1 \le 0\} (2)

}

Post-Cond: \{(x=0 \land y=\alpha+1 \land \alpha+1>0)\}

\forall (x = 0 \land y = \alpha + 1 \land \alpha + 1 < 0) \}

```

By applying appropriate inference rule at each execution step, the formulae that describe the states are generated. Symbolic state and path condition are two properties that corresponding to those formulae. A path condition describes the pre-condition of the execution path to the current statement, starting from the program entry. For example, symbolic state  $[x \Rightarrow \alpha, y \Rightarrow \alpha + 1]$  and path condition  $\alpha + 1 > 0$  correspond to the formula that is true at (1). Similarly, formula at (2) have symbolic state  $[x \Rightarrow \alpha, y \Rightarrow \alpha + 1]$  and path condition  $\alpha + 1 \leq 0$ .

Figure 2.6: Examples of symbolic execution

An SMT solver (e.g., Z3[30]) is often used to verify whether the explored path is *feasible*, i.e, check if the path condition is *satisfiable*. Classical (static) symbolic execution can face difficulty when dealing with external code not traceable by the executor, complex constraints or indirect jumps in binary code. A fundamental idea to make symbolic execution more feasible in practice is using dynamic symbolic execution (DSE).

• Static symbolic execution. The next instruction candidates are statically detected. Then each destination is checked by using a SMT solver to decide the feasibility of each newly create path condition.

• Dynamic symbolic execution (or concolic testing). The feasibility of next instruction is checked by testing with an instance from the precondition, which requires a binary emulator.

When dealing with indirect jump, it is insufficient to use a constraint solver to find all possible targets of the branching instruction, so the next instruction needs to be dynamically decided. For example, at the time of the indirect jump instruction  $bx\ lr$ , the state of the register lr is an expression of symbolic values. Therefore, an satisfiable instance of precondition are used to get the concrete value of lr.

## 2.3 SE tools for binary

This section introduces some notable symbolic execution tools for analysis of binary codes.

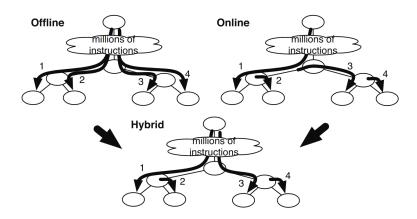

#### 2.3.1 **MAYHEM**

MAYHEM [7] proposed the technique of hybrid symbolic execution, which is a combination of online and offline (concolic) execution. MAYHEM combines both techniques by swapping between symbolic execution engines when memory is under pressure. MAYHEM focus on taint analysis for exploitable bug finding.

#### Binary Representation

MAYHEM leverage BAP [31] to convert each x86 assembly instruction to BAP IL. The symbolic execution rules are based on the defined operational semantics for IL statement types [32].

#### Hybrid Symbolic Execution

Hybrid symbolic execution is introduced to maximize the effectiveness between ofline and online executor. First, the analysis is started in online mode. When the system reaches a certain memory usage, the analysis is switch to offline mode. In offline mode, no more new executors are forked, but the system produces checkpoints for online executions later. The idea behind this technique is distributing the online executor tasks into subtasks without losing potential paths.

#### External system interaction

MAYHEM prepares models for system and library calls (about 30 system call in Linux and 12 library calls in Windows). For multiple threads handling, it does not deal with multiple threads/multiple processes program when there are interaction between threads.

#### 2.3.2 KLEE-MC

KLEE-MC [8] is a symbolic execution engine for binary, which is built on KLEE.

Figure 2.7: Hybrid symbolic execution in MAYHEM

#### Intermediate Representation

KLEE-MC [8] uses a binary translation to translate from machine code into IR (e.g., x86-64 to LLVM). KLEE first converts machine code to VEX IR using Valgrind, then from VEX IR into LLVM IR. The binary codes are loaded into VEX IR as basic blocks.

#### Symbolic Execution Model

In the original version of KLEE, it expects that all code is loaded without concerning about self-modification and dynamically loaded libraries. KLEE-MC use a new strategy, it loaded each basic block. Then it analyse the return value of a basic block to decide the next executed block.

#### System Models

KLEE-MC models the system calls to interact between the symbolic engine and the underlying system. The system model in C supports both Linux (x86, x86-64, and 32-bit ARM) and Windows (x86). The return value of the modeled system calls are symbolic values, which means the model "over-approximate" the system interaction. KLEE-MC also provide a framework for users to use system hooks to modify program's control flow.

#### 2.3.3 angr

angr [11] is a widely used open source binary analysis framework that support many analyses such that dynamic symbolic execution, backward slicing, or data-dependency analysis.

#### Intermediate Representation

angr translates native binary code (e.g., ARM, MIPS, PPC, x86, and amd64) to an intermediate representation - VEX IR. Beside VEX IR, angr is also support several different

representations (e.g., Capstone [16]). angr loads the binary by basic blocks of VEX IR statements.

#### Control flow graph (CFG) and Indirect jumps

Angr contains several strategies to construct a control flow graph from binary samples. In angr, there are two types of CFG that can be generated: a static CFG (CFGFast) and a dynamic symbolic execution CFG (CFGEmulated).

- CFGFast uses static analysis to generate a CFG. It is significantly faster, but does not contain the control flow information. This is the same analysis performed by other popular reverse-engineering tools, such as IDA Pro, Ghidra.

- CFGEmulated uses symbolic execution to capture the CFG. While it is theoretically more accurate, it is much more slower and less complete due to missing system calls, missing hardware features, and so on.

CFGEmulated first analyses a list of basic blocks and adds corresponding direct jumps for each block. Indirect jumps can not be resolved this way. For indirect jump, it traverses backwards until encounter a *merge point* (where multiple paths converged) or a threshold number of blocks. From that point, angr perform symbolic execution and use a constraint solver to resolve the indirect jump value.

#### External call

One of the biggest limitations of angr when analyzing real-world software is the environment model. angr models some external calls by their own implementation in Python, called SimProcedure. Since having a SimProcedure for every library function is unrealistic, angr ends up executing statically loaded binary code and encounters errors with unsupported system calls. Although angr provides the framework for users to hook to a place and directly return any desired value at any given call, this is not an easy task for a large binary file, especially when malware usually contains more than 100 external function calls.

## 2.3.4 BINSEC/SE

BINSEC/SE [33] is a binary analysis engine focusing on the interaction between a tracer and the symbolic execution component.

#### Binary Representation and PINSEC

BINSEC/SE is built on the platform of BINSEC, which transforms the trace of x86 instructions to the intermediate representation in DBA [34] (Figure 2.9). The tracer, which is called PINSEC[35] is used to generate execution trace of Linux and Windows binaries. After retrieving the result from PINSEC, the data is passed as the input of BINSEC/SE.

Figure 2.8: Architecture of BINSEC/SE

Figure 2.9: Corresponding DBA instructions of a x86 instruction

Two most notable differences between PINSEC and other pintools [35] are: (i) allowing injection of concrete or symbolic values in any location during the execution steps, and (ii) a remote C&C system for interaction between the DSE core and PINSEC (Figure 2.8).

#### DSE engine

The path predicates that computed from the PINSEC trace are passed to the *Path Selection* module. The criteria to choose the best path is based on a user-defined *score* function of some properties such as trace length, call-depth, etc. Some strategies (e.g., DFS, BFS, and random path) are already provided.

## Chapter 3

# DSE for ARM Instructions: CORANA

This chapter discussed the formal semantics of ARM and the dynamic symbolic execution of ARM binaries on the instruction label. The semantic extraction process of ARM instructions from the natural language description to preliminarily built a DSE tool for ARM Cortex-M called CORANA (<u>Cortex Analyser</u>) is also described in this chapter.

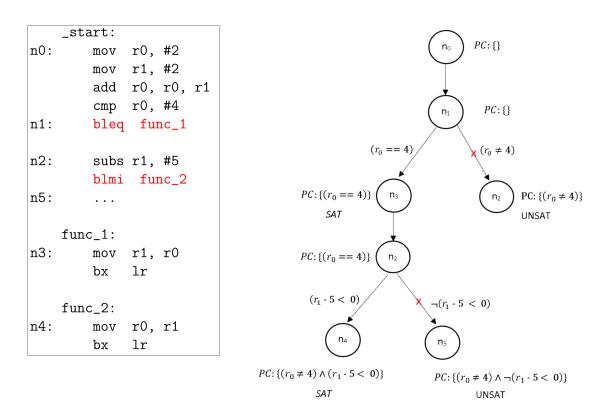

#### 3.1 Formal semantics of ARM

To build the emulator for the verification tools, the modeling of the instruction semantics [36] is required (CoDisam[9], BE-PUM[12]). Therefore we need to define the operational semantics of ARM in order to build the binary emulator for DSE. The main difficulties in defining formal semantics are weak memory model and synchronization. Luckily, our target is IoT malware, particularly ARM binary, which is mostly sequentially consistent. This implies that operations must appear to execute one at a time and in program order. In this study, the execution of each ARM instruction is regarded as a transition on the environment model made by registers, memory, stack, and flags. Based on the architecture design of ARM Cortex-M [37], we can define the environment model.

**Definition 3.1.1.** For the environment elements, *Values* is a domain for an interpretation, the environment model of ARM Cortex-M is defined as a mapping:

$$Env: (R \to Values) \times (F \to Values) \times (M \to Values) \times (S \to Values)$$

(3.1)

- referred by  $\langle R, F, M, S \rangle$  where the tuple  $\langle R, F, M, S \rangle$  consists of:

- R: a set of registers  $R = \{r_0, r_1, r_2, r_3, r_4, r_5, r_6, r_7, r_8, r_9, r_{10}, r_{11}, r_{12}, sp, lr, pc, apsr\}$  where apsr keeps the control code flags N,Z,C,V (and Q, GE in some ARM versions).

- F: a set of flags  $F = \{N, Z, C, V, Q, GE\}$

- M: a set of n memory locations  $M = \{m_0, m_1, m_2, ...\}$

- S: a stack  $(S \subset M)$

• Values represent the domain of the environment elements (e.g, 32-bit BitSet in concrete execution, or Expression(Sym) in symbolic execution).

For a shorter notation, we denote  $Env = \langle R, F, M, S \rangle$  to represent the mapping in Equation 3.1 as the environment model.

The description of the environment elements of ARM Cortex-M is written in the ARM Architecture Reference Manual [37] as follows:

- 1. **Registers:** The ARM registers are divided into two kinds: general purpose and special purpose registers.

- R0-R12: General purpose registers

- R13: SP (Stack Pointer). The stack pointer points to the top of the stack, which is a specially area in the memory. The stack pointer is used to allocate space on the stack.

- R14: LR (Link Register). When a function call is made, the link register is updated as the memory address of the next instruction after the call.

- R15: PC (Program Counter). The program counter tracks the current instruction location by storing the address of the current instruction plus 8.

- 2. **Flags:** The ARM flags are updated by execution of instructions. They might be used for branch decisions, or as input of the next instruction.

- N: Set when the last operation result in a Negative value.

- Z: Set when the result of the operation is Zero.

- C: Set when the last operation resulted in a Carry.

- V: Set when operation caused oVerflow, which means the result is greater than or equal to 2<sup>31</sup>, or less than −2<sup>31</sup>.

The combinations of these four flags (N, Z, C, and V) can create 15 branch conditions (Table 3.1).

- 3. **Memory:** A set of contiguous memory locations. Before the execution, the binary program is loaded on a memory area M.

- 4. **Stack:** Stack is a subset of memory where data is pushed or pop in a last-in-first-out (LIFO) manner.

The execution of an instruction i is regarded as a transition  $t_i$  on the environment model. In CORANA, each register in R, memory location in M and S are represented by a 32-bit vector, while flags in F are boolean variables. The values of the registers and flags are initialized by symbolic values. Those values are updated throughout the execution of each instruction. The register PC points to the address of the next instruction and the register SP points to the top of Stack.

Figure 3.1: The semantics transition  $t_i$  of the instruction i

The figure 3.2 shows some rules of the operational semantics of ARM instructions that are implemented in CORANA. Each rule describes a transition of the environment model caused by the corresponding ARM instruction. For example, the mov instruction copies the data item referred into the register and updates pc register.

$$\frac{R_{pc} = k; \; instr(k) = mov \; i \; j; R_{j} = m}{\langle F, R, M, S \rangle \rightarrow \langle F, R[pc \leftarrow k + | instr(k) | ; R_{i} \leftarrow m], M, S \rangle} \; [\text{MOV}]$$

$$R_{pc} = k; \; instr(k) = ands \; i \; j \; h; \; R_{j} = m; R_{h} = n; a = m \; \& \; n;$$

$$N' = (a < 0); Z' = (a = 0); C' = (a \ge 2^{32} - 1); V' = (a \le -2^{31}) \lor (a \ge 2^{31} - 1)$$

$$\langle F, R, M, S \rangle \rightarrow \langle F[N \leftarrow N'; Z \leftarrow Z'; C \leftarrow C'; V \leftarrow V'], R[pc \leftarrow k + | instr(k) | ; R_{i} \leftarrow a], M, S \rangle} \; [ANDS]$$

$$\frac{R_{pc} = k; \; instr(k) = neg \; i \; j; \; R_{j} = n}{\langle F, R, M, S \rangle \rightarrow \langle F, R[pc \leftarrow k + | instr(k) | ; R_{i} \leftarrow !n], M, S \rangle} \; [NEG]$$

$$R_{pc} = k; \; instr(k) = cmp \; i \; j; \; R_{i} = m; R_{j} = n; a = m - n;$$

$$N' = (a < 0); Z' = (a = 0); C' = (a \ge 2^{32} - 1); V' = (a \le -2^{31}) \lor (a \ge 2^{31} - 1)$$

$$\langle F, R, M, S \rangle \rightarrow \langle F[N \leftarrow N'; Z \leftarrow Z'; C \leftarrow C'; V \leftarrow V'], R[pc \leftarrow k + | instr(k) | ], M, S \rangle} \; [CMP]$$

$$\frac{R_{pc} = k; \; instr(k) = ldr \; i \; j; \; M_{j} = m}{\langle F, R, M, S \rangle \rightarrow \langle F, R[pc \leftarrow k + | instr(k) | ; R_{i} \leftarrow m], M, S \rangle} \; [LDR]$$

Figure 3.2: Some examples of the operational semantics

In CORANA, the formal semantics of each ARM instruction is represented as a Java method build on top of a customized **BitVec** class, which is a pair  $\langle bs, s \rangle$  where bs is a **BitSet** 32-bit vector and s is a string. Corresponding to the BitVector theory of SMT solvers, 35 basic methods had been manually implemented as basic functions for the binary emulator. All automatically generated Java methods are operated based on them.

#### Example 1

According to the operation instruction, the UMAAL (Unsigned Multiply Accumulate Accumulate Long)<sup>1</sup> "multiplies the 32-bit values in Rn and Rm, adds the two 32-bit values in RdHi and RdLo, and stores the 64-bit result to RdLo, RdHi". Its operation can be

$<sup>^{1} \</sup>rm https://developer.arm.com/documentation/arm-and-thumb-instructions/multiply-instructions/umaal$

described in the operational semantic and a corresponding Java method as the followings [38].

```

R_{pc} = k; inst(k) = umaall \ rdlo \ rdhi \ rn \ rm; R_{rdlo} = lo; R_{rdhi} = hi;

R_{rn} = n; R_{rm} = m; a = m*n + lo + hi; hi' = a \gg 32; lo' = (a \ll 32) \gg 32;

\langle F, R, M, S \rangle \rightarrow \langle F, R[pc \leftarrow k + |inst(k)|; R_{rdlo} \leftarrow lo'; R_{rdhi} \leftarrow hi'], M, S \rangle

[UMAAL]

```

Listing 2: The semantic of UMAAL instruction written in Java [21]

## 3.2 Path condition generation

## 3.2.1 Conditional branching in ARM

Every computing architecture has a mechanism for checking condition (e.g., if-else in C). In ARM, conditional execution are implemented using a set of flags that store the information of previous operations. In other words, the branch condition is checked based on the status of four flags (N, Z, C, and V) in the APSR (Application Process Status Register).

The flags is updated with the execution of instructions. The most common way to set condition flags is using the comparison operation (e.g., CMP, CMN, TST, TEQ). In addition, many arithmetic and logical instructions such as SUBS, ADDS can update the condition flags based on the results of the operations. The example below shows how the ADDS instruction updates the flags.

#### Example 2

The following code fragment shows how the flags are set in ARM:

The result of this operation should be r0=0x100000000. However, since the 32-bit destination register cannot fit the result, the actual result saved in r0 is 0x00000000 and the flags are also updated accordingly.

- N = 0. The result is 0x0, which is positive, so N bit is 0.

- Z = 1. The Z bit is set to 1 since the result is 0x0.

- C = 1. C bit is 1.

- V = 0. The operation (which equivalent to -1 + 1 = 0) did not caused overflow, so V (oVerflow) is 0.

By using those four flags, we can control the program's flow by making jumps or executing certain instructions when a condition is satisfied. With combinations of the four conditional flags, 15 branch conditions are defined Table 3.1.

| Symbol | Meaning                | Condition    |

|--------|------------------------|--------------|

| EQ     | Equal                  | Z==1         |

| NE     | Not equal              | Z==0         |

| CS/HS  | Carry set              | C==1         |

| CC/LO  | Carry clear            | C==0         |

| MI     | Minus V1               | N==1         |

| PL     | Plus                   | N==0         |

| VS     | Overflow               | V==1         |

| VC     | No overflow            | V==0         |

| HI     | Unsigned higher        | C==1 && Z==0 |

| LS     | Unsigned lower or      | C==0    Z==1 |

|        | same                   |              |

| GE     | Signed greater than or | N==V         |

|        | equal                  |              |

| LT     | Signed less than       | N!=V         |

| GT     | Signed greater than    | Z==0 && N==V |

| LE     | Signed less than or    | Z==1    N!=V |

|        | equal                  |              |

| AL     | Always                 |              |

|        |                        |              |

Table 3.1: ARM Conditional Suffix [39]

#### 3.2.2 Path condition in ARM

The path condition is a formula that describes the precondition of the execution path from the entry point to the current nodes. At current assembly instruction i, the path

condition  $\phi_i$  from initial node to i is updated through each step of the computation as:

$$\begin{cases} \phi_0 = true \\ \phi_i = \phi_{i-1} \wedge c_i \end{cases}$$

(3.2)

with  $c_i$  is the constraint generated by instruction i.

As discussed previously, ARM instructions can be made to execute conditionally by postfixing with certain condition codes. During the execution, the path condition is updated based on branching mechanism of ARM assembly.

#### Example 3

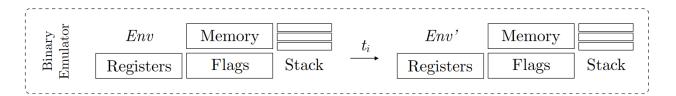

This figure show how path conditions are generated in CORANA.

Figure 3.3: Path condition in the execution of ARM instructions

The control flow graph in the right hand describes the represented assembly codes. The instructions from location  $n_0$  to  $n_1$  performs two assignments ( $r_0 = 2$  and  $r_1 = 2$ ), then adds  $r_0 = r_0 + r_1$  to make the states of  $r_0$  and  $r_1$  become 4 and 2, respectively. The *cmp* instruction compares the current value of  $r_0$  to 4, makes Z = 1 (Zero flag is set).

At  $n_1$ , a conditional branch bleq occur and the prefix eq checks for Z flag. The condition eq returns true when Z == 1, which means  $r_0 == 4$  and returns false when  $r_0 \neq 4$ . Using the SMT Solver to check the satisfiability of each path constraint, the negation branch returns UNSAT.

Continuing on the feasible path, at  $n_2$  the register  $r_2$  becomes -1 and the N flag (Negation) is set because of the negative result. The branching condition blmi checks if N == 1 i.e.,  $r_1 - 5 < 0$ . The path condition for two new branches are updated by conjunction as  $(r_0 \neq 4) \land (r_1 - 5 < 0)$  and  $(r_0 \neq 4) \land \neg (r_1 - 5 < 0)$ . Same as the previous branching condition, each path is checked whether it is SAT or UNSAT.

#### Path condition in Hoare Logic

As previous mentioned in Section 2.2, the triple of Hoare Logic defined as:

$$\frac{Precondition}{Postcondition}$$

[Instruction] (3.3)

shows how the execution of a *Instruction* transform the system state.

**Definition 3.2.1.** A symbolic state (pre/post-condition) at location i is a tuple  $\langle \alpha_i, Env \rangle$  where:

- $\alpha_i$  is the path condition formula at *i*.  $Var(\alpha_i) \subseteq Sym$ , Sym is the set of symbolic symbols.

- $Env = \langle F, R, M, S \rangle$  is the environment model. The value stored at a register, a flag or a cell in the memory can be a constant (e.g., specific address, arithmetic constant), a symbolic value, or a formula.

In previous section, we represent each ARM instruction as an operation semantic rule. By applying the formal semantics, we can almost immediately obtain the post-condition.

$$\frac{\langle \alpha, Env \rangle}{\langle \alpha', Env' \rangle} \quad [\text{Instruction}]$$

$$\frac{\langle \alpha, \langle F, R, M, S \rangle \rangle}{\langle \alpha, \langle F, R[pc \leftarrow pc'; R_i \leftarrow m], M, S \rangle \rangle} \quad [\text{MOV Ri, m}]$$

$$\frac{\langle \alpha, \langle F, R, M, S \rangle \rangle}{\langle \alpha, \langle F[N \leftarrow N'; Z \leftarrow Z'; C \leftarrow C'; V \leftarrow V'], R[pc \leftarrow pc'; R_i \leftarrow a], M, S \rangle \rangle} \quad [\text{CMP m, n}]$$

with  $a = m - n$ ,

and  $N' = (a < 0), Z' = (a == 0), C' = (a \ge 2^{32} - 1), V = (a \le -2^{31}) \lor (a \ge 2^{31} - 1)$

$$\frac{\langle \alpha, \langle F, R, M, S \rangle \rangle}{\langle \alpha \land \langle Z_{flag} == 0\rangle, \langle F, R[pc \leftarrow k], M, S \rangle \rangle} \quad [\text{BNE k}] \quad \text{if } Z_{flag} \text{ is not set}$$

$$\frac{\langle \alpha, \langle F, R, M, S \rangle \rangle}{\langle \alpha \land \neg \langle Z_{flag} == 0\rangle, \langle F, R[pc \leftarrow pc + 4], M, S \rangle \rangle} \quad [\text{BNE k}] \quad \text{if } Z_{flag} \text{ is set}$$

#### 3.3 Formal semantics extraction of ARM instructions

#### 3.3.1 Semantic extraction from natural language specifications

Each ARM architecture has a relatively small number of instructions (around 60-300), but various variants exist (e.g., Cortex-A, Cortex-M, Cortex-R). Our study focuses on ARM Cortex-M, which is mostly used for micro-controllers such as IoT devices. To built the binary emulator for the dynamic execution tool, the operational semantic of ARM instructions need to be extracted from its natural language specification. The specification of ARM instruction from the official ARM documentation [39] contains five sections: mnemonic, description, syntax, operation, and flags-update.

| Mnemonic     | UASX                                                                     |  |

|--------------|--------------------------------------------------------------------------|--|

| Description  | Unsigned Add and Subtract with Exchange                                  |  |

| Syntax       | UASX{cond} {Rd,} Rn, Rm                                                  |  |

|              | Subtracts the top halfword of the second operand from the bottom         |  |

|              | halfword of the first operand. Writes the unsigned result to the bottom  |  |

| Operation    | halfword of the destination register. Adds the top halfword of the first |  |

|              | operand with the bottom halfword of the second operand. Writes the       |  |

|              | unsigned result to the top halfword of the destination register.         |  |

| Flags-update | This instruction set the APSR_GE bits according to the results.          |  |

Figure 3.4: The specification of UASX in ARM Cortex-M7 [39]

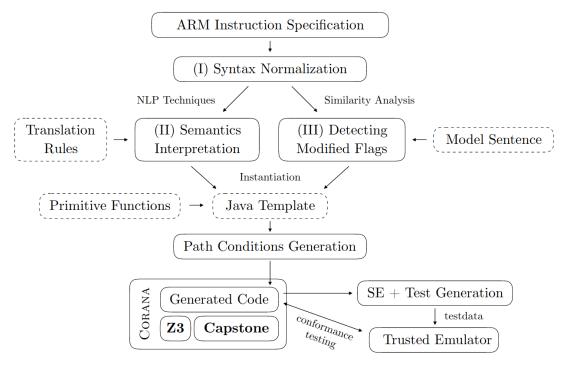

In the previous work [21], the formal semantics of ARM have been semi-automatically extracted from the instruction specifications. Each ARM instruction is interpreted and represented by a Java method to build the binary emulator for the DSE tool (as shown in Example 1). Figure 3.5 illustrates an overview of the extraction process, with the dashes boxes representing manually prepared tasks.

The first step in the process, each sentence in the ARM instruction specification is normalized by parsing, lemmatization and word refinement. After normalizing, two parts of the instruction needs to be analyzed are operational semantic (Figure 3.5 - II) and flag modification information (Figure 3.5 - III).

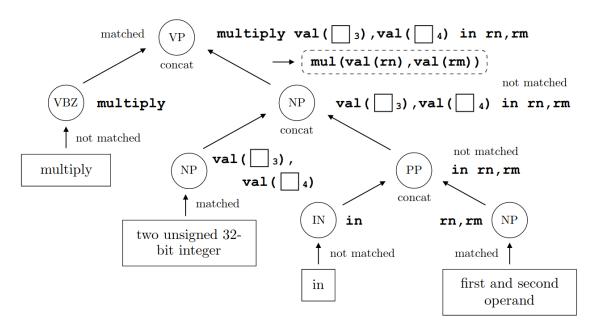

#### • Semantics Interpretation by Translation Rules

The interpretation follows a rule-based method by utilizing popular *NP-Phrases*. We manually prepared around 200 predefined rewriting rules to interpret the the formal semantics of instructions in a bottom-up manner.

For example, a set  $\{c_1, c_2, c_3\}$  of NP-Phrases is obtained through syntax normalization, where  $c_1$  is "first and second operand",  $c_2$  is "two unsigned 32-bit integer", and  $c_3$  is "multiply  $\square_2$  in  $\square_1$ ". Based on the set of NP-Phrases, the following rules are repaired [38]:

1. Rule r1: first and second operand  $\rightarrow rn$ , rm

Figure 3.5: Semantic extraction from NLP specification of ARM [38]

- 2. Rule r2: two unsigned 32-bit integer  $\rightarrow val(\square_3)$ ,  $val(\square_4)$

- 3. Rule r3: multiply  $val(\square_3)$ ,  $val(\square_4)$  in rn, rm  $\rightarrow mul(val(rn), val(rm))$

The instruction sentence is then transformed to a Java statement by applying the above rules in a bottom-up manner.

#### Modified Flag Detection

The descriptions about flags-update are written in natural language. To decide whether the flags information is changed or not, a topic modelling method - Latent Dirichlet Allocation (LDA)[40] is used. After training the LDA model, the simility between the topic distribution of the target sentence and the model sentence "update effect set change modify" are calculated. The flag is consider as modified or unmodified base on whether the result exceed a predefined threshold t.

After obtaining the interpretation of the instruction, the method represents for its operational semantic is built based on a Java template. The generated methods combining with predefined primitive functions are used to construct a binary symbolic execution engine for the DSE tool CORANA.

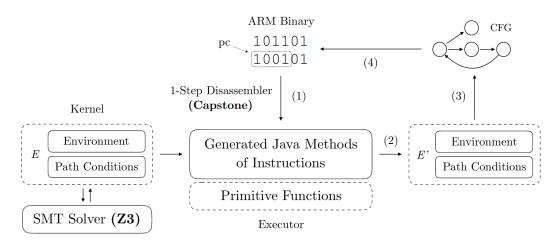

#### 3.3.2 CORANA architecture

CORANA[21] consits of two main components: (I) A kernel including the emulated environments and the generated path conditions, and (II) A symbolic executor which built

Figure 3.6: Semantic interpretation of ARM instruction [21]

from the generated Java methods and predefined primitive functions.

Figure 3.7: CORANA Architecture

Figure 3.7 shows the execution flow of CORANA to generate a control flow graph from an input binary file.

- (1) First, the ARM binary file is single-step disassembled from the  $\_start$  location of the program to obtain instruction i.

- (2) The symbolic executor executes instruction i and updates the kernel (including the environment and the path condition).

- (3) If the next instruction is an indirect jump, SMT solver solves the path condition to obtain possible initial environment to reach the point. Then concolic testing will decide

the next location. A new node and its connected edge are then added to the control flow graph.

(4) Disassembles the next instruction and repeats the process until reaching the end of the program.

CORANA has covered 66.6% of ARM instructions over 6 variants. However, programs are usually not self-contained, they need to interact with the surrounding environment. Particularly in the case of malware binaries, system calls and library function calls are largely used. External calls that occur lead to an exception in CORANA and make the execution process be interrupted. To make symbolic execution more tractable, in the next chapter, we propose a solution in handling external calls of the program to the Linux/Unix system using API Stubs.

# Chapter 4

# DSE for Library Functions of Linux: CORANA/API

# 4.1 C Standard Library

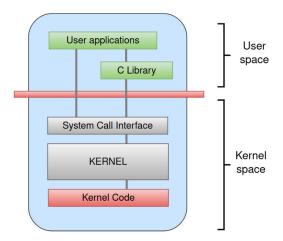

Most programs are not self-contained but frequently interact with the underlying operating system and external systems. Typical examples are the interaction with the resource of the operating system (e.g., system variables, file system, and network) and the interaction with other devices that are beyond the current system over the network (e.g., Command & Control Server, and peer devices).

Figure 4.1: C Standard Library<sup>1</sup>

Linux/POSIX API. An user-level programs communicate with the kernel is by using system calls. When the program requires resources, it sends a request as a system call to the kernel and the mode changes to the kernel mode. Application programs do not usually contain direct system calls. In Linux system, the API allows user processes to access system resources and services of the kernel. Linux APIs mostly follow the POSIX

standard.

C Standard Library. A C standard library is a wrapper for the Linux kernel system calls (e.g., GlibC, UClibc). A C standard library such as The GNU C Library<sup>2</sup> (GlibC) provides a cross-platform to execute functions that would otherwise require system-specific system calls. It provides the APIs for many systems that use Linux or Unix as the kernel. We collected source codes and descriptions of 1659 APIs from *qlibc*.

# 4.2 External call template in JNA

Java Native Access (JNA) is a Java library that provides access to native shared libraries. JNA allows Java program to invoke native code via JNI.

Figure 4.2: Java Native Access

#### Example 4

The following program loads the native C standard library implementation and invoke native *gettimeofday* function.

```

public interface CLibrary extends Library {

CLibrary INSTANCE = Native.load("c", CLibrary.class);

int gettimeofday(CStruct.timeval tv, CStruct.timezone tz);

}

public static void main(String[] args) {

CStruct.timeval tv = new CStruct.timeval();

CStruct.timezone tz = new CStruct.timezone();

int ret = CLibrary.INSTANCE.gettimeofday(tv,tz);

System.out.println("Result: " + ret);

```

<sup>&</sup>lt;sup>2</sup>https://www.gnu.org/software/libc/

```

System.out.println("Seconds since 1/1/1978: " + tv.tv_sec);

System.out.println("Microseconds: " + tv.tv_usec);

}

```

### Library Mapping

To access to the methods of a shared library, a class corresponding to that library needs to be created. For example, a mapping for the C library itself can be defined in two ways: interface-mapped class and direct-mapped class.

```

// Alternative 1: interface-mapped class, dynamically load the C library

public interface CLibrary extends Library {

CLibrary INSTANCE = (CLibrary)Native.loadLibrary("c", CLibrary.class);

}

// Alternative 2: direct-mapped class

public class CLibrary {

static {

Native.register("c");

}}

```

Listing 3: C library loaded class in JNA [41]

When we instantiate a native library interface via Native.load() to dynamically load the C library, JNA creates a proxy which routes all method invocations through a single handler. This handler has the responsibility to look up and invoke the appropriate function object which represents the corresponding function in the native library.

#### **Function Mapping**

With interface-mapping, function names are mapped directly from their Java interface to the native library. Native libraries, such as C standard library contains many functions in the source code, but only a set of functions are used by the actual programs. JNA handles the run-time mapping of the function in the interface class to the method in the native library. We only need to call the method in the interface to call the native corresponding method. For instance, the *atoi* function in C can be called via JNA by the following.

```

public interface CLibrary extends Library {

int atoi(String s);

}

```

Listing 4: The function atoi in JNA

## Type Mapping

Types in C need to be mapped to type with same size in JNA<sup>3</sup>. In C, types can generally divided into two kinds: primitive types and pointers. Parameters with primitive types are directly passed by value, while pointers are passed by reference to a cell or a block of cells in the memory. To map to JNA, all other types must be converted to one of the types in the Table 4.1.

Table 4.1: Types supported by JNA library [41]

| C Type               | Native Representation                                  | Java Type   |

|----------------------|--------------------------------------------------------|-------------|

| char                 | 8-bit integer                                          | byte        |

| wchar_t              | platform-dependent                                     | char        |

| short                | 16-bit integer                                         | short       |

| int                  | 32-bit integer                                         | int         |

| int                  | boolean flag                                           | boolean     |

| enum                 | enumeration type                                       | int         |

| long long,int64      | 64-bit integer                                         | long        |

| float                | 32-bit floating point                                  | float       |

| double               | 64-bit floating point                                  | double      |

| pointer (e.g. void*) | platform-dependent (32- or 64-bit pointer to memory)   | Buffer      |

| long                 | platform-dependent (32- or 64-bit integer)             | NativeLong  |

| const char*          | NUL-terminated array (native encoding or jna.encoding) | String      |

| char**               | NULL-terminated array of C strings                     | String[]    |

| void**               | NULL-terminated array of pointers                      | Pointer[]   |

| struct*              | pointer to struct (argument or return)                 | Structure   |

| struct               | struct by value (member of struct) (or explicitly)     | Structure   |

| union                | same as Structure                                      | Union       |

| struct[]             | array of structs, contiguous in memory                 | Structure[] |

| other                | integer type                                           | IntegerType |

| void (*FP)()         | function pointer (Java or native)                      | Callback    |

# 4.3 External call handling

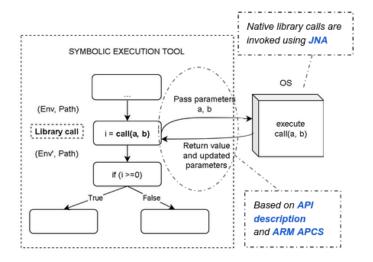

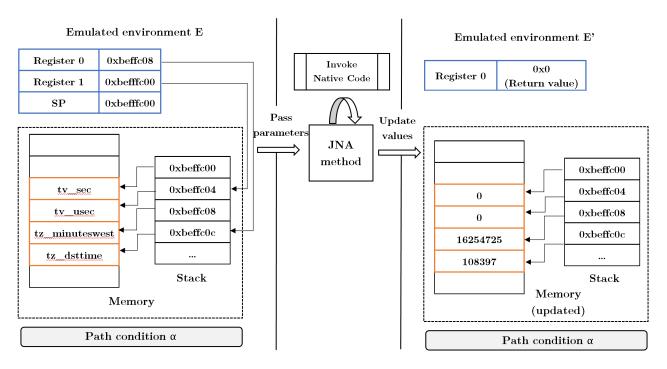

As discussed in Chapter 1, it is preferable that the programs interact directly with their real environment while performing symbolic execution. Our approach follows to previous work such as Syman[24] and BEPUM[12] and prepares the API Stub of system calls to interact with external environment. An API Stub requires a interface as a proxy to invoke the native function, retrieves the return value, and updates the environment after the system/library function call. JNA is used to invoke the native C function in the API Stub.

<sup>&</sup>lt;sup>3</sup>https://java-native-access.github.io/jna/4.2.0/overview-summary.html

For the symbolic execution with external function calls, two updates are matters, i.e., the path condition update and the environment update. Note that external function calls are mostly OS library function calls or API calls, which are executed in the kernel level. Thus, a user-level process cannot observe how it is computed. We show the extension of Hoare logic and the soundness of the API stub approach.

# Hoare Logic Revisited

Definition 3.2.1 presents the instruction level Hoare logic

$$\frac{Precondition}{Postcondition}$$

[Instruction]