|              |                                                                                                                                                   |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Title        | 生成AIとチップレット時代におけるEB直描アプローチの検討                                                                                                                     |

| Author(s)    | 若林, 秀樹                                                                                                                                            |

| Citation     | 年次学術大会講演要旨集, 40: 452-457                                                                                                                          |

| Issue Date   | 2025-11-08                                                                                                                                        |

| Type         | Conference Paper                                                                                                                                  |

| Text version | publisher                                                                                                                                         |

| URL          | <a href="https://hdl.handle.net/10119/20233">https://hdl.handle.net/10119/20233</a>                                                               |

| Rights       | 本著作物は研究・イノベーション学会の許可のもとに掲載するものです。This material is posted here with permission of the Japan Society for Research Policy and Innovation Management. |

| Description  | 一般講演要旨                                                                                                                                            |

## 生成AIとチップレット時代におけるEB直描アプローチの検討

○若林秀樹(熊本大学 半導体デジタル研究教育機構)

[wakawaka@kumamoto-u.ac.jp](mailto:wakawaka@kumamoto-u.ac.jp)

### 1. はじめに

半導体産業はMoore則の中、微細化を中心とした巨額先行投資競争の結果、ファブレスはNVIDIA、ファウンドリはTSMC、製造装置はASMLと、三大寡占企業に依存する構造が強まっている。巨額な投資負担と高価なマスク代からEUVL<sup>1</sup>による製造は基本的にCPUやGPUやメモリなど汎用チップの小品種大量生産が向いており、ASICなど少量多品種には不向きで、GPUの雄NVIDIAが有利となる。これでは資金規模が少ないベンチャーはチップの自社開発生産は難しい。多様なアイデアニーズに対応するイノベーションは停滞する。安全保障観点では国家覇権を決める高度AI先端半導体チップの製造が地政学リスクのある台湾TSMCと蘭ASMLだけに依存するのも好ましいとは言えない。更に電力の大量消費が大問題である。脱TSMC一極依存の観点ではラピダスが設立、立上げ中で世界から期待されている。脱EUVではキヤノンのナノインプリント商用化はあるが部分的な工程に留まっている。

他方、生成AI時代を迎える、学習はクラウド、推論はエッジ側でアプリケーション特化という新たなトレンドが生まれ専用AIチップが注目されつつある。またMoore則も60年近く転換点にありチップレットはじめMore than Mooreへの技術トレンドが注目される。そこで生成AIとチップレットの組み合わせによるビジネスモデルを生みだすことが必要である。こうした大変革期にこそ過去の先行投資と量産競争から脱し新たなビジネスモデルを考えなければならない。そこに日本復活の機会もある。

生成AIとチップレットにマスクレスなEB直描<sup>2</sup>を組み合わせれば、柔軟性に富み多品種少量向き低価格で電力消費も少ない生産が可能になる。EB直描はスループットが課題だがヘテロジニアスも含めたチップレットと組み合わせることでボトルネックを除く。この新ビジネスモデルは半導体業界にスマートな新たなトレンドをもたらす。特に多品種少量を目指すラピダスには効果が大きい。

### 2. 先行研究

半導体ビジネスモデルについてはアカデミアの論文の他、ムーアの著作[1]、アナリストレポートも含め多くの先行研究がある。ビジネスモデル一覧を示す(図表1)。ここでは生成AIやチップレットに関連したビジネスモデルとEB直描の事業化に関する先行研究に絞って論じる。

図表1 ビジネスモデル一覧 (出所)若林秀樹

| 日本                 |                  |                    |                     | ソ連                | 米国           |                                   |                            |                    | 台湾                           |                                     | 中国           |  |

|--------------------|------------------|--------------------|---------------------|-------------------|--------------|-----------------------------------|----------------------------|--------------------|------------------------------|-------------------------------------|--------------|--|

| 70年代               | 80年代             | 90年代以降             | これから                | ソ連                | 基本           | 90年代                              | 2000年代                     | イスラエル、ウクライナ<br>も類似 | 伝統                           | 2010年以降                             |              |  |

| 米学び+<br>品質量産<br>政府 | 大型先行<br>投資コストダウン | 戦略不在               | 短TAT<br>変種変量<br>変価格 | 丸ごと<br>コピー<br>霸権  | ハイテク<br>霸権   | 先行逃げ切り<br>ロードマップ                  | チック・<br>タック戦略              | 高株価+M&A<br>水平分業    | ハイテクシールド<br>米と両輪<br>水平分業を支える | ハイテク<br>導入                          | 不動産投資<br>モデル |  |

| 補足                 | 通産省+<br>電電通研     | 低金利と<br>低期待<br>ROE | 日米摩擦、<br>バブル崩壊      | 社会主<br>義国家<br>の限界 | 軍事、<br>DARPA | 水平分業を韓国台湾と<br>両輪で主導、ビジネス<br>モデル利用 | ファブレスは<br>ウォールスト<br>リートと両輪 | 米と補完               | 知財等<br>何でも                   | 工場投資は政府<br>工場都市で地価<br>アップ政府資金<br>回収 |              |  |

チップレットを活かしたビジネスモデルについては、若林の研究がある[2]。チップレットならではの前工程FEOL(Front End of Line:トランジスタ)とBEOL(Back end of line:配線)の並列・短TAT(turn-around-time)生産を先端ロジック半導体工場に導入想定し、財務シミュレーションで効果を検証した。稼働率を下げても1.25~1.4倍の値上げでフル生産と短TAT生産で5年間の累損は同じ営業利益率は安定することを示した。複数のケースで並列生産の効果を確認、通常生産に対し黒字化が1年早まり、累損1/3となることを示した。効果の背景は、①無駄な投資無し②歩留まりや需要に応じた最適生産である。しかしラピダスには、マスク代やEUV投資負担によるコスト増を懸念する指摘も多かった。

<sup>1</sup> EUVL: Extreme ultraviolet lithography 数十の世界拠点から部品を集め、立上げに数百人のエンジニアと数か月が必要。一台500億円以上な金額と製造に大量の消費電力が必要。先行巨額投資モデルの象徴

<sup>2</sup> Electron Beamでマスクを使わずにlithography(リゾ:パターン形成)を行う。

EB 直描の可能性については、光リソ等の比較など、理工学系の学会などで多くの先行研究がある。日立評論 1994 年 7 月で、①微細加工性と高精度な重ね合わせ、②パターニング多様性とスループット改善により、クオーターミクロソルト時代には光リソ限界で、6 μm で ASIC1 品種当たり総ウェハー投入枚数 250 枚以下では有利になると論じた[3]。その後 2006 年には光リソ限界と EUV 開発の困難、システム LSI 期待からアドバンテストは新たに 65nm/45nm 製造プロセスに対応した EB 装置を開発、富士通と共同で EB 直描技術対応プロセスを開発するイー・シャトル社を共同設立した[4]。2013 年には 1xnm プロセス対応 EB 装置を東大や京大などから受注、現在も大学や研究機関で稼働している。

しかし、現在、EB 直描はマスク製造の他、MEMS、6 μm の小口径、大学研究所の試作サービスには有効利用されているが 300mm 量産ラインへの導入は無い。その後、光リソは ArF 液浸パターンニング等の技術開発がなされた。多くの問題点を指摘された EUVL も ASML の不断の長期に亘る開発成果により最先端では独壇場となった。EB 直描はスループット問題から適用範囲はマスク、MEMS、試作等に留まっており、EB 直描によるビジネスは議論出尽くしの感がある。

それゆえ生成 AI とチップレットを生かす EB 直描アプローチに関して議論が無かったが、垂井康夫元超 LSI 研究組合所長が「ラピダスが目指す主要な用途は AI であり、AI 半導体は多品種少量生産であり、そこでは EUV もいいが最近性能向上が著しい EB を使いまた立体構造が鍵になることを考えると、AI 半導体に向けた EB による微細化と立体構造のための共同研究所が必要だ」[5]と提案した。ただし詳細な議論やビジネスモデルの議論は無い。そこで、このアイデアをヒントに可能性を検証する。

### 3. 生成 AI とチップレットを生かす EB 直描アプローチとビジネスモデル

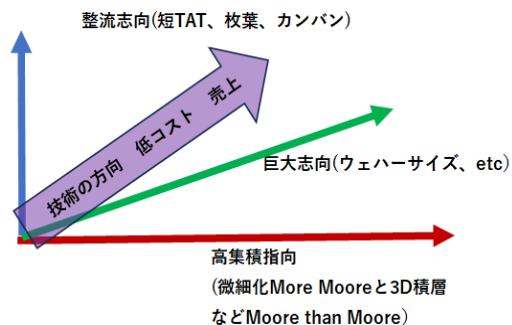

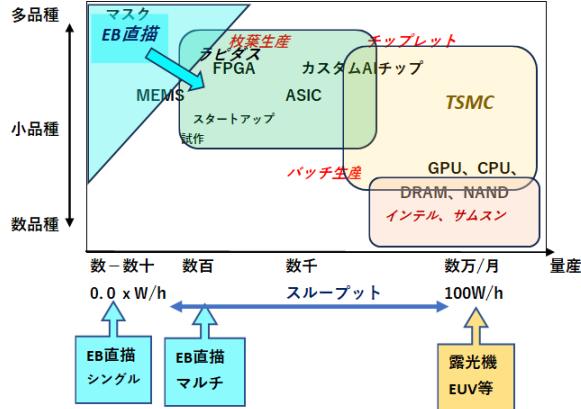

これまで EB 直描が何度も期待されながらも光リソに破れたのは先行研究が指摘する低スループットであり光リソ弱点に対する相対メリットが期待されたが、光リソ側が多くの課題を克服した(図表 2)。また、スループットや大面積化は大量生産コストダウンのビジネスの方向性であり(図表 3)は EB 直描が不利に働く方向性であった。他方で 2000 年以降、ウェハー大面積化は 300mm で飽和、450mm 化は消えた。Moore 法則、微細化も周波数特性飽和からモノリシックでの集積化ではないチップレットアプローチが普及し始めている。このチップレットも含めて 3D 実装など More than Moore は大きなトレンド変化であり、過去は EB 直描が難しかった前提条件が一変する可能性がある。もちろん、カーボンニュートラルや国家安全保障からの脱 ASML 依存も大きな風向きの変化である。

図表 2 EB 直描のこれまでこれから(出所)若林秀樹

| これまで   |                                            | これから                                                                                 |

|--------|--------------------------------------------|--------------------------------------------------------------------------------------|

| 90年代   | 一括露光の難しさから機会<br>⇒ステップ重ね合わせ克服               | 2025年以降 チップレット                                                                       |

| 2000年代 | EUVの難しさや高コスト、<br>電力の問題から機会<br>⇒EUV実用、あとは無視 | スループットは遅いが、マルチ化で<br>改善、小さく多様なダイを作りあと<br>で統合、段差や複雑なパターン、<br>RDLや検査テストや修正リペアとも<br>シナジー |

|        | スループットの致命的遅さを他の利点<br>で補おうとしたが              |                                                                                      |

図表 3 技術の 3 つの方向性 (出所)若林秀樹

どのようなニーズや技術トレンドが EB 直描に有利か不利かを示すが、チップレットによるダイの小面積化や 3D による段差などは有利である。

図表 4 EB 直描に有利か不利か (出所)若林秀樹

| EB直描 有利    |            | EB直描 不利 EUV 有利                                     |                        |  |

|------------|------------|----------------------------------------------------|------------------------|--|

| ニーズ        | 低スループットでも可 | 高スループット<br>高電力でも可<br>修正頻度少ない<br>同一パターン<br>精度・微細 粗い | 大量生産<br>コスト志向<br>技術の進化 |  |

|            | 省電力        |                                                    |                        |  |

|            | 修正頻度多い     |                                                    |                        |  |

|            | 変形パターン     |                                                    |                        |  |

|            | 精度・微細 重要   |                                                    |                        |  |

| チップ<br>レット | 凹凸・段差・トレンチ | 平面<br>大面積化(ウェハー)<br>大面積化(ダイサイズ)<br>EUVも不利だが克服      |                        |  |

|            | 小面積        |                                                    |                        |  |

|            | 小面積(ダイサイズ) |                                                    |                        |  |

## カスタマイズ多品種少量となるエッジ AI 半導体

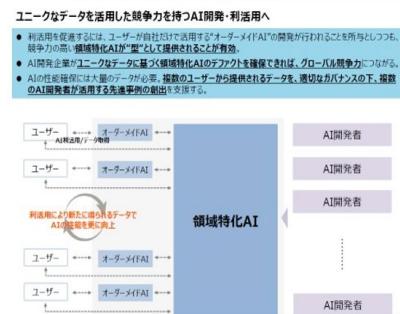

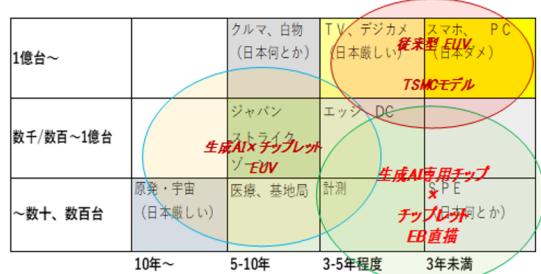

需要面では、これまで EB 直描の適用は多品種少量の ASIC や FPGA 向けが期待されてきたが、巨大な市場でなくメインは依然、CPU や GPU、DRAM や NAND フラッシュといった大量生産製品である。需要が拡大している生成 AI でも DC 向けは NVIDIA の GPU や HBM であり大量生産である。

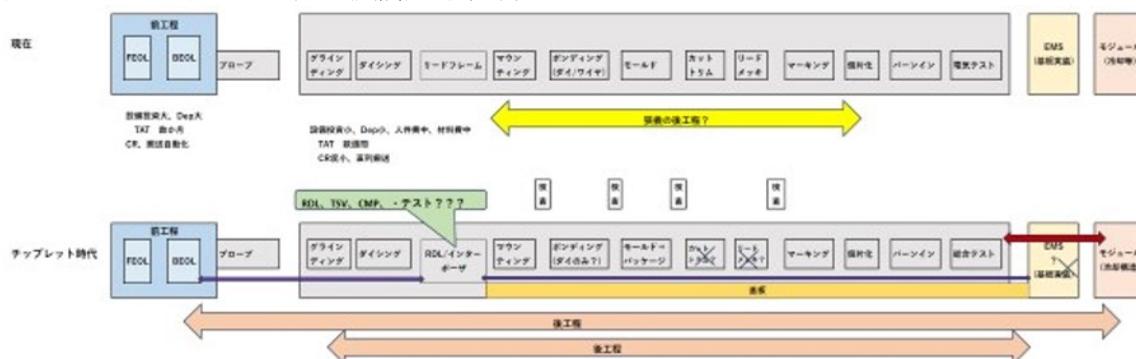

しかし、生成系 AI は、新応用分野である DC のあり方を変えつつある。2000 年以降は Web 閲覧やメールを処理するインターネット DC だったものが、2020 年から現在は、クラウド処理のハイパースケーラー DC、そして 2025 年以降は、生成系 AI 時代が本格化、学習推論の AI-DC となり、学習はセンター(量子と共に)、推論はエッジとなる。そこでは、クラウド側では GAFAM が支配する汎用 GPU の世界だが、エッジ側、端末側、あるいは、エッジ側の分散型 DC では、アプリケーションに特化することから GAFAM は自社専用チップを開発、生成 AI カスタムチップ多品種少量が必然になる(図表 5)。

図表 5 生成 AI 専用チップ CPU⇒GPU⇒AI チップ (出所)経産省

◎各企業のカスタムチップ(例)

CPU(汎用・大量・端末⇒GPU(汎用・大量:中央⇒AIチップ(専用・多品種少量・端末/中央)

(出所): 経産省

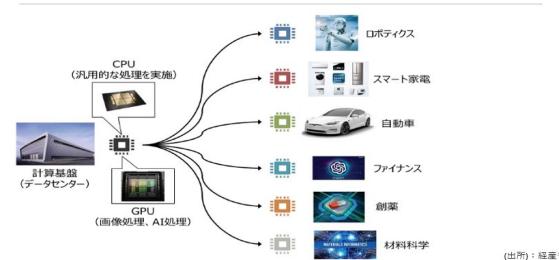

## 前工程と中・後工程が一体化し設計と結びつくチップレット技術

チップレットは異なる前工程で製造したダイをプリント基板上で RD ポーラー<sup>3</sup>に搭載するため(図表 6)、パッケージチップを別のプリント基板に搭載する可能性は減り EMS 工程が変わる。熱問題から冷却構造が鍵でありパワーモジュールの冷却部品工程も必要である。RDL 形成を中心工程と呼ぶが、リソや CMP などが必要で装置構成は前工程に近い。基板上に先端ロジックやメモリだけでなくパワー や光チップも搭載が可能となる。

図表 6 チップレットと工程 (出所)若林秀樹

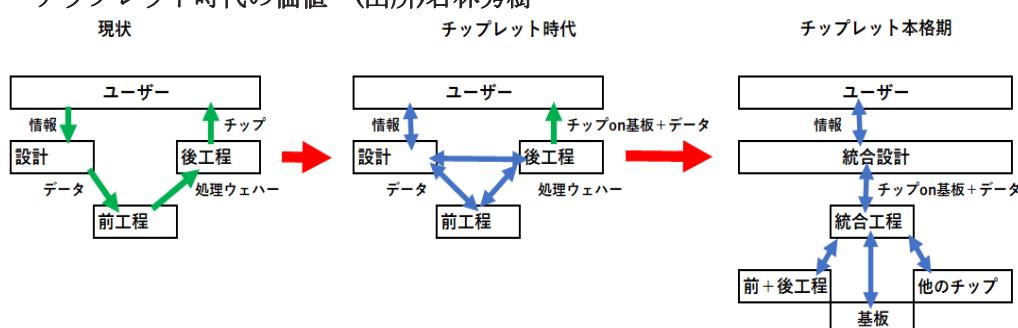

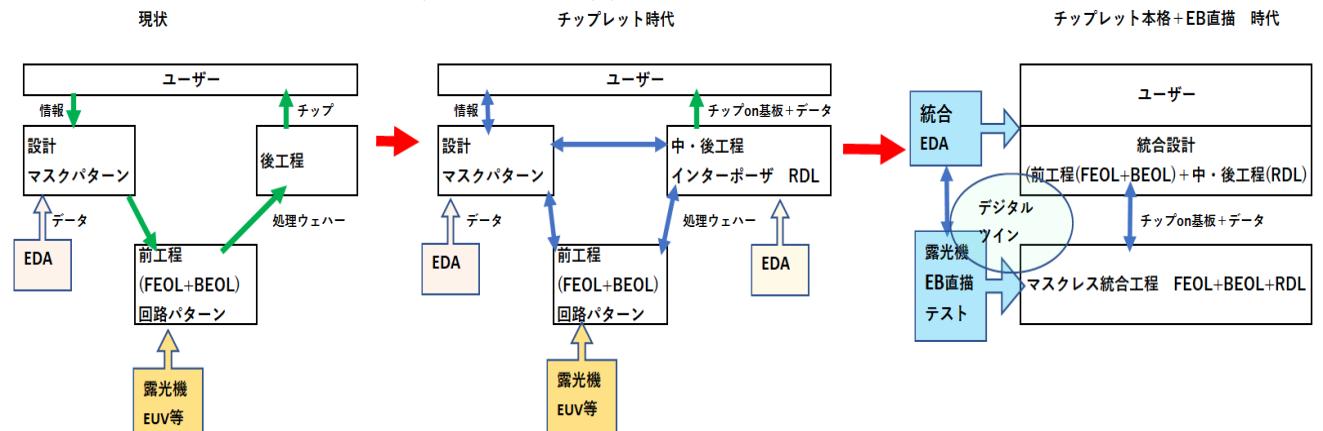

チップレット化で前工程優位の生産から中・後工程へ価値がシフト、設計が前工程だけでなく中・後工程と直結する。また、チップレットは前後工程融合や異種チップ接合、設計と後工程の融合が起きる。

図表 7 チップレット時代の価値 (出所)若林秀樹

<sup>3</sup> Re Distribution Layer Interposer(再配線層インター ポーラー)

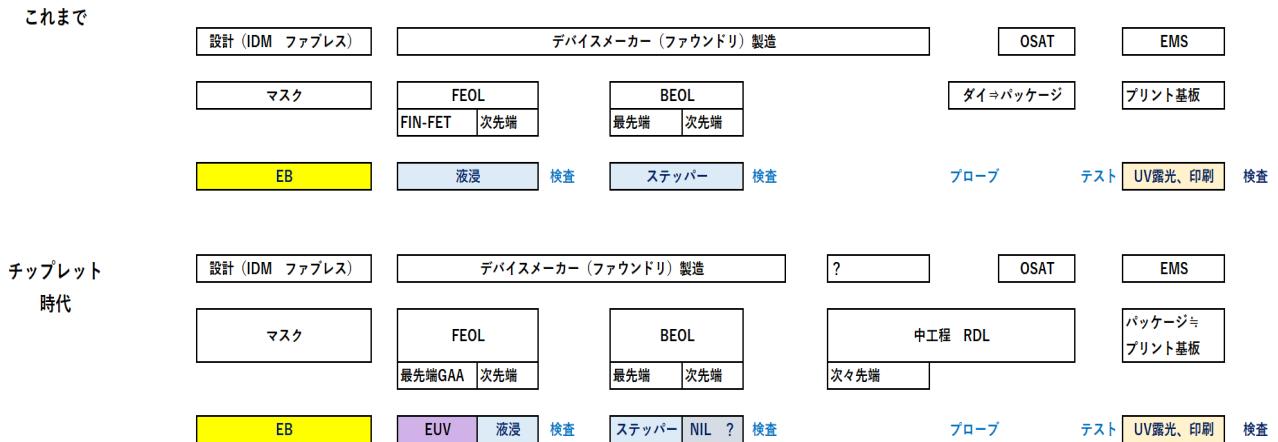

これを微細化の観点で考えると現状では設計はユーザーニーズに基づき EDA ツールを生かしマスクを EB により製造する。これがマスクセット数億円から最近は数十億円と高価である。また、前工程では EB でなく EUV や液浸によるリソである。後工程はプリント基板の配線パターン別のリソ技術で形成している(図表 8)。

図表 8 チッププレット時代の EB 直描効果 (出所)若林秀樹

これがチッププレット時代には、後工程に RDL が必要となり光リソやナノインプリントが描く。配線幅は前工程 BEOL が RDL に近い。RDL 向け EDA が必要だが熟や強度設計が重要になる。現状では設計データが前工程と後工程では十分に連携されず EDA も別である。チッププレットでは多様なチップを後から統合するためテストが重要である。更にチッププレット本格時代には EDA は統合され、FEOL と BEOL と RDL のデータも一体化、設計データから生まれるデジタルツインと実チップを比較、テストデータの特性データが設計データにフィードバックされるであろう(図表 9)。

図表 9 チッププレット時代は設計と露光が統合 (出所)若林秀樹

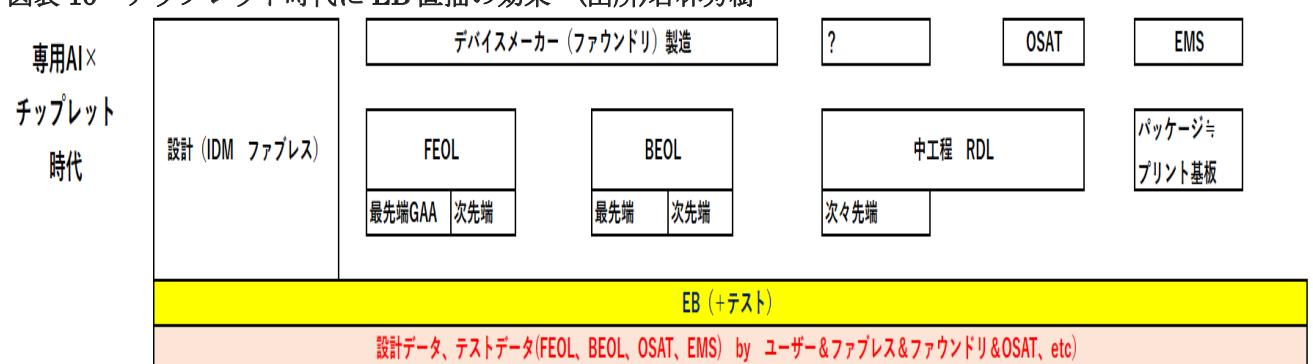

そこではリソ一体運用されるメリットが生まれてくる。もし EB 直描が全工程に導入されれば、設計、FEOL、BEOL、OSAT、EMS で別々だったパターン形成が全て EB に統一、テストも統合、リペアなども容易になる可能性がある(図表 10)。

図表 10 チッププレット時代に EB 直描の効果 (出所)若林秀樹

#### 4. 効果検証によるビジネスモデル成立領域

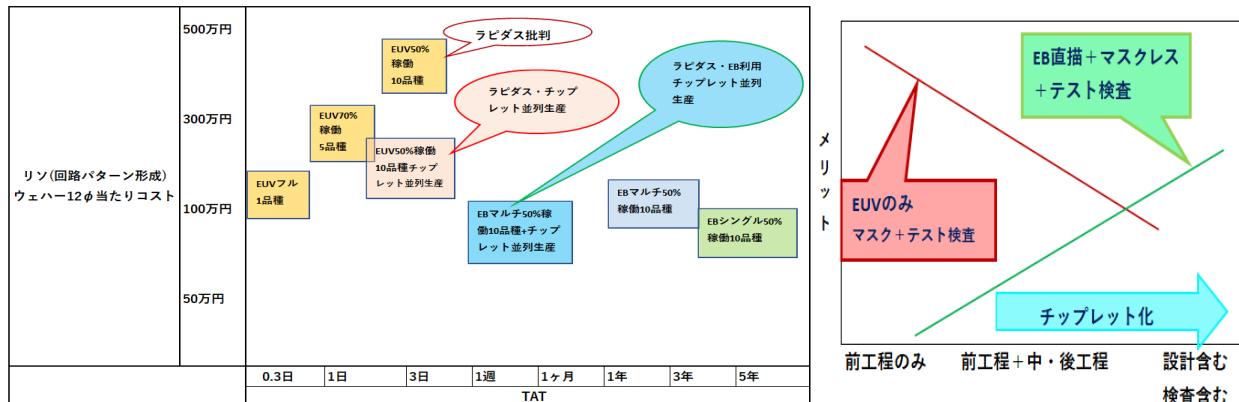

EB直描のメリットは多いが、低スループットの問題から、EUVを上回るには、多品種少量の程度やチップレット活用の並列生産が必要である。そこで、ここでは、EB直描ビジネスモデルの成立領域を考える。公開情報を参考に、EUVやEB、マスクのコスト、TAT等、幾つかの前提をおいて、ケーススタディを行った(図表11)。なお、実際は各社で異なり、あくまで成立条件の傾向を示すに過ぎない。評価の二軸マップとしてウェハー(300mm)当たり露光コストと露光時間を選び、多品種を1、5、10とし、それに応じた稼働率を設定、チップレット並列生産も加味し、財務シミュレーションを行った。

図表11 EB直描とEUVの財務シミュレーションとケース (出所)若林秀樹

|                           | EUV                  |                       |                      |                          |                      | EB                                      |                       |                                        |       |

|---------------------------|----------------------|-----------------------|----------------------|--------------------------|----------------------|-----------------------------------------|-----------------------|----------------------------------------|-------|

|                           | EUV<br>量産1品種<br>フル稼働 | EUV<br>量産5品種<br>稼働70% | EUV<br>10品種<br>50%稼働 | EUV<br>10品種50%稼働<br>並列生産 | 10品種50%稼働<br>EB直描マルチ | 10品種50%稼働<br>EB直描マルチ<br>+チップレット<br>並列生産 | 10品種50%稼働<br>EB直描シングル | 10品種50%稼働<br>直描シングル+<br>チップレット並列<br>生産 |       |

| 年間Wキャバ 100万枚              | 100                  | 70                    | 50                   | 50                       | 50                   | 50                                      | 50                    | 50                                     | 50    |

| 稼働率                       | 100%                 | 70%                   | 50%                  | 50%                      | 50%                  | 50%                                     | 50%                   | 50%                                    | 50%   |

| 品種数                       | 1                    | 5                     | 10                   | 10                       | 10                   | 10                                      | 10                    | 10                                     | 10    |

| 露光時間(マスク取り換え時間5分+1分/EB直描) | 6                    | 6                     | 6                    | 6                        | 600                  | 60                                      | 6000                  | 600                                    | 600   |

| コスト 年間 億円                 | 11250                | 16250                 | 22500                | 22500                    | 50                   | 50                                      | 5                     | 5                                      | 5     |

| ウェハー当たり 万円(リソのみ)          | 113                  | 232                   | 450                  | 158                      | 100                  | 35                                      | 100                   | 35                                     | 35    |

| TAT 日                     | 0.3                  | 1.7                   | 3.3                  | 1.7                      | 333.3                | 16.7                                    | 1666.7                | 166.7                                  | 166.7 |

EUVの1品種フル稼働では約100万円強でTATは1日以下であり、多品種少量にすると、TATはやや長くなるが、それ以上にマスク代や稼働率低下によるコストアップが大きく10品種では450万円と高く難しい。これが、まさにラビダスが多品種少量で採算が難しいと指摘されている点である。EB直描はEUVに比べ装置代は1/10以下であり、償却負担やメンテコスト、マスク代も不要で、コストは安い。しかしマルチビームでも1年、シングルビームでは5年近くかかり非現実的であるのは指摘されている通りである。しかし、これに、GAA(Gate All Around)中心のFEOLと配線中心のBEOLを分けて並列生産する、チップレットを組み合わせれば、マルチビームなら、2週間程度、シングルでも半年と現実的になる。更に、これに全工程EDAデータ共有化やテスティング、リペア等の効果を加えれば、チップレットを考慮していけば、EB直描が成立する領域が見えてこよう(図表12)。

図表12 コストとTATで棲み分けだがチップレット化で広がる (出所)若林秀樹

技術面でのメリット定量分析は難しいが考慮に入れる必要がある。まず設計の柔軟性と変更反映時間の短縮である。エッジAI向け統合チップではAIコアとFPGAの混載チップにおいて、AI部が高頻度で設計変更に対しFPGA部分は安定設計が求められるが、EB直描の部分露光によりAI領域のみを迅速に更新でき、AIコア最適化サイクル加速に有効である。データ変換時間短縮も大きい。また、GAA フィン構造はナノ幅制御が可能である。位置合わせ精度は3D積層に必須だが、異種チップの統合ではインターポーラ上での微細TSV形成にも有効である。RDLの多様なパッド配置にEBの柔軟性が効く。前工程のゲートコンタクト層にEBを重点導入、チップレット接続部の高精度位置合わせにEBを活用、配線層形成では1xnm層はEB、上層をEUVとするハイブリッド方式もある。

スループット以外に課題も多い。荷電効果では高抵抗材料による位置ずれ発生、プロセス統合ではEBレジストとEUV現像液の互換性問題や界面剥離リスクもある。

## 5. ラピダスが勝てるビジネスモデル

ラピダス RUMS (Rapid & Unified Manufacturing Service) モデルに EB 直描チップレット並列生産を組み合わせることで更に成功確率は高まる。縦軸に品種数、横軸に生産数量をとると、左上が多品種少生産でありマスクや MEMS など EB 直描の領域である。右下が CPU や GPU の小品種大量生産 EUV 領域の TSMC がある。この間に多品種適量市場のラピダスのストライクゾーンがある(図表 13)。

図表 13 ラピダスと TSMC の棲み分け チップレット EB 直描成立領域と経営重心 (出所)若林秀樹

チップレットEB直描が成立する領域と

経営重心ジャパンストライクゾーン

新たな時代には EB 直描とチップレット並列生産導入によるビジネスモデル、エコシステム形成が求められる(図表 14)。市場特性もサプライチェーンも異なる。極論すれば、低スループットの欠点が無くなる 6~7 年未満で作成、チップレットで並べれば良い。AI チップのコア部のサイズ次第であるといえる。

図表 14 新たな時代のエコシステムとビジネスモデルの対比 (出所)若林秀樹

| 市場の特性                  | 汎用最先端 ASSP的 市場                                            | 中間の市場                       | 専用最先端 生成AI×チップレット FPGA的 市場                 |

|------------------------|-----------------------------------------------------------|-----------------------------|--------------------------------------------|

|                        | スマホ、PCなど、数億、1個 数千円                                        | クルマ、ロボット、医療、SPE等            | DC、基地局、スタートアップ向け                           |

|                        | 1億から数億個のボリューム<br>2~3年サイクル、設計変更少                           | 1000万~1億個ボリューム<br>5~10年サイクル | 数百万個のボリューム<br>2~3年サイクル、設計変更多               |

|                        | 大量生産、過大性能、熱多くても可                                          | 多品種少量、最適性能 熱少い要求            |                                            |

| 生産の特徴、<br>サプライチェーン     | 見込み生産、在庫、トライ&エラー                                          | ↔                           | 設計と OSAT が近く、早くエラーを回せる生成AIで<br>サプライチェーン最適化 |

|                        | 需給管理難、在庫リスク、低コスト<br>リスクある長サプライチェーン                        |                             | カンバン、一見、高コストだが地産地消<br>リスク小の短サプライチェーン       |

| ビジネスモデル                | 価値は高価な装置、Dep から                                           | ↔                           | 価値は組合せや設計から                                |

|                        | 水平分業 ファブレス/ファンドリ モデル                                      |                             | 新垂直統合、チップレット モデル                           |

|                        | 先行巨大投資 M&A                                                |                             | 工程最適 (BEOL/BEOL、ノード別) 投資                   |

| 露光<br>EUV モデルか EB<br>か | 量産 EUV                                                    | ↔                           | マスクレス EB 直描 (テスト一体)                        |

|                        | EUV は蘭、ステッパーとマスクは日本<br>検査・テストは日米                          |                             | EB は日米 (日本電子 & IMS、ニューフレア)<br>検査・テストは日米    |

|                        | マイナス要素: 消費電力、メンテ、マスク代 長TAT<br>プラス要素: 高稼働、既存エコシステム (既存EDA) |                             | マイナス要素: 低稼働 新EDA<br>プラス要素: 低消費電力、短TAT、リペア可 |

## 6. おわりに

本検討により、エッジ AI 専用チップ向け多品種少量市場にチップレットを利用した並列生産導入で、EB 直描が戦略的選択肢となり得ることを示した。マルチ方式でスループットが高め、デジタルツイン等を導入し一体 EDA とテストイングを組み合わせれば優位性がある。今後の技術進化次第では EUV 依存度を下げられる。また、ラピダスが勝てる戦略の選択肢になるだろう。

超 LSI 研究組合時代に EB かステッパーかの議論であり、当時は大量生産の DRAM ゆえに光リソのステッパーだったが、枚葉多品種少量低稼働なら EB が見直されることは温故知新である。この考察を踏まえ、NEDO や JST 等でプロジェクトとすることが期待される。

参考文献 URL は 2025 年 9 月 22 日アクセス

- [1] ムーア「インテルとともに: ゴードン・ムーア私の半導体人生」1995 日経

- [2] [JAIST Repository: 新時代の半導体ビジネスモデル：チップレットの影響と稼働率とカスタム性の関係：大型設備投資と大量生産時代から抜け出し、新たな価値を](#)

- [3] [日立評論 1994 年 7 月号:高スループットを実現した電子ビーム直接描画システム](#)

- [4] [65nm 以降の EB 直描に賭けるイー・シャトル・セミコンポータル](#)