## **JAIST Repository**

https://dspace.jaist.ac.jp/

| Title        | 金属/YSZ/Si構造上への単結晶強誘電体PZT薄膜の作製    |

|--------------|----------------------------------|

| Author(s)    | 堀井,貞義                            |

| Citation     |                                  |

| Issue Date   | 1998-09                          |

| Туре         | Thesis or Dissertation           |

| Text version | none                             |

| URL          | http://hdl.handle.net/10119/2572 |

| Rights       |                                  |

| Description  | Supervisor:堀田 將,材料科学研究科,修士       |

## 金属/YSZ/Si 構造上への単結晶強誘電体 PZT 薄膜の作製

堀井 貞義 (堀田研究室)

【はじめに】強誘電体薄膜を用いたMFIS(Metal Ferroelectric Insulator Semiconductor)-FET型メモリは、高速動作、低消費電力などの特徴を持つため理想的なメモリとして期待されている。このMFIS-FETでは、Si 基板中への強誘電体材料の拡散や反応などの抑制の目的で、Si と強誘電体薄膜間にバッファ層を挿入している。以前本研究室では、PZT薄膜のバッファ層としてエピタキシャル(100)YSZ薄膜を用いていたが、YSZとPZTの格子不整合が10.8%もあるために界面付近で多数の結晶欠陥が生じ、電気的特性に悪影響を及ぼしていることがわかった。そこで本研究では、PZTとYSZの格子不整合を緩和するために、その間に金属薄膜を挿入したMFMIS(Metal Ferroelectric Metal Insulator Semiconductor)構造を採用し、Ir金属およびPZT薄膜をエピタキシャル成長させ、良好な強誘電体特性を得ることを目的としている。

【実験方法】YSZ 薄膜は、反応性スパッタ法により (100)Si 基板上にヘテロエピタキシャル成長させた。Ir 薄膜は、スパッタ法により YSZ/Si 基板上に基板温度  $600\sim700^{\circ}$ C で堆積した。PZT 薄膜は、反応性スパッタ法により基板温度  $600\sim650^{\circ}$ C で厚さ 200nm 堆積した。最後に電気的特性の測定のため、真空蒸着により Au 上部電極を形成した。

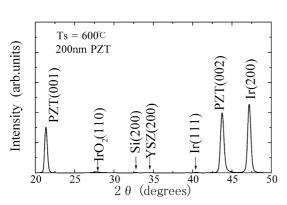

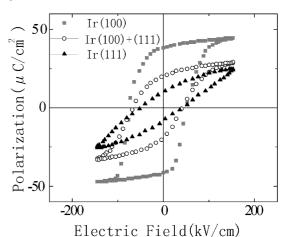

【結果】単結晶 (100) YSZ 薄膜上の Ir 薄膜の配向は、堆積速度により (1) Ir(100) 主配向、(2) Ir(100)+(111) 混在配向、(3) Ir(111) 主配向と制御できた。試料 (1)(2) の上に基板温度 600 °C で堆積した PZT 薄膜は (001) にエピタキシャル成長した。その一例として、(100) Ir 薄膜上に PZT 薄膜を堆積した試料の XRD パターンを図 1 に示す。また、試料 (3) 上では、基板温度 650 °C で、PZT(111) に優先配向した。これら 3 種類の PZT 薄膜の Au-Ir 間の分極-電界 (P-E) 特性を図 2 に示す。図から、下地の Ir 薄膜の (100) への配向度が強いほど、残留分極が大きく、エピタキシャル (001) PZT 薄膜の残留分極 2 Pr、抗電界 2 Ec は、それぞれ  $80\mu$ C/cm²、130 kV/cm であることがわかる。また、リーク電流は Ir 薄膜の (100) への配向度が強いほど小さかった。

図1: PZT/Ir/YSZ/Si 構造の XRD パターン

図 2: PZT 薄膜の P-E 特性

keywords MFMIS, PZT, Iridium, YSZ, 強誘電体, Si, メモリー

Copyright © 1998 by Sadayoshi Horii