## **JAIST Repository**

https://dspace.jaist.ac.jp/

|              | 45 T ( 1 % )                     |  |

|--------------|----------------------------------|--|

| Title        | 矩形パッキングとそのVLSIモジュール配置問題への応<br> 用 |  |

| Author(s)    | 村田,洋                             |  |

| Citation     |                                  |  |

| Issue Date   | 1997-03                          |  |

| Туре         | Thesis or Dissertation           |  |

| Text version | author                           |  |

| URL          | http://hdl.handle.net/10119/833  |  |

| Rights       |                                  |  |

| Description  | Supervisor:岡本 栄司,情報科学研究科,博士      |  |

## Rectangle Packing and Its Applications to VLSI Module Placement Problem

By Hiroshi Murata

A thesis submitted to

School of Information Science,

Japan Advanced Institute of Science and Technology,

in partial fulfillment of the requirements

for the degree of

Doctor of Information Science

Graduate Program in Information Science

Written under the direction of Professor Eiji Okamoto

January 16, 1997

### Abstract

The first and the most critical stage in VLSI layout design is the placement. Its background is the rectangle packing problem: Given a set of rectangular modules of arbitrary sizes, place them without overlap on a plane within a rectangle of the minimum area. Since the variety of the packing is uncountably infinite, the key issue for successful optimization is the introduction of a finite solution space which includes an optimal solution and excludes all the infeasible solutions. The main contribution of this thesis is in the introduction of such a solution space where each packing is represented by a pair of module name sequences, called sequence-pair. The introduction of this solution space enables us to use stochastic optimization method such as simulated annealing, and it is demonstrated that hundreds of modules was packed very efficiently. The biggest MCNC benchmark example is also shown to be placed very promisingly with a conventional wiring consideration method.

Although module positions are successfully represented by the sequence-pair, it is desired frequently in VLSI design that channels are represented together with modules, because a channel router is often used in the following routing stage. For this request, this thesis gives a mapping from a sequence-pair to a rectangular dissection, which represents channels by line segments.

Placement with obstacles in the chip is also discussed in this thesis, for dealing with pre-placed modules and with a rectilinear placement region. The obstacles are easily included in a sequence-pair to eliminate the overlaps, but the sequence-pair cannot guarantee to recover the assigned coordinates of the obstacles. To solve this practical problem, this thesis gives an algorithm which changes an inconsistent sequence-pair to a consistent one.

## Acknowledgments

The author indebted to his principal advisor Professor Eiji Okamoto of Japan Advanced Institute of Science and Technology for his constant encouragement.

The author would like to thank to his advisor Associate Professor Kunihiko Hiraishi of Japan Advanced Institute of Science and Technology for his helpful discussions and suggestions.

Special thanks are to Associate Professor Mineo Kaneko of Japan Advanced Institute of Science and Technology for his constant guidance. Much of the final year of research was guided by him.

The author wishes to express his sincere gratitude to his prior principal advisor Professor Yoji Kajitani of Tokyo Institute of Technology for his helpful discussions, guidance, and all the activities, that inspired the author throughout the course of this research.

The author devotes his sincere thanks and appreciation to Research Associate Kunihiro Fujiyoshi of Japan Advanced Institute of Science and Technology, currently at Tokyo University of Agriculture and Technology. His eager discussions helped the author especially on building the proofs presented in this thesis.

Special thanks are to Research Associate Shigetoshi Nakatake of Tokyo Institute of Technology. He jointly started this research with the author, and has been an excellent partner throughout the research. He gave the first idea for our common target, and the discussions on his initial idea helped the author to develop the theory presented in this thesis.

The author is grateful to all who have affected or suggested his areas of research, especially to Visiting Professor Milan Vlach and Visiting Associate Professor Magnus Halldórsson.

Special thanks are to Mr. Eda, Mr. Funahara, Mr. Kaneko, Mr. Yamagishi and all the engineers at Murata Mfg., Co. Ltd. The motivation of this research is mainly from the author's experience in developing the CAD/FA system with them.

Finally, I would like to thank my wife Akiko and our sons Shun'ichi and Tatsurou for their love and support.

## Contents

| A                 | $oldsymbol{	ext{Abstract}}$ |                                                            |     |  |  |  |  |

|-------------------|-----------------------------|------------------------------------------------------------|-----|--|--|--|--|

| f Acknowledgments |                             |                                                            |     |  |  |  |  |

| 1                 | Intr                        | Introduction                                               |     |  |  |  |  |

|                   | 1.1                         | Rectangle Packing Problem                                  | 1   |  |  |  |  |

|                   | 1.2                         | Previous Researches                                        | 1   |  |  |  |  |

|                   | 1.3                         | Thesis Outline                                             | 2   |  |  |  |  |

|                   | 1.4                         | Remarks                                                    | 3   |  |  |  |  |

| 2                 | Rec                         | cangle Packing Solution Space Composed of Sequence-Pairs   | 4   |  |  |  |  |

|                   | 2.1                         | Introduction                                               | 4   |  |  |  |  |

|                   | 2.2                         | From Packing to Sequence-Pair                              | 6   |  |  |  |  |

|                   |                             | 2.2.1 Gridding                                             | 6   |  |  |  |  |

|                   |                             | 2.2.2 Geometrical Information of Sequence-Pair             | 9   |  |  |  |  |

|                   | 2.3                         | From Sequence-Pair to Packing                              | .0  |  |  |  |  |

|                   |                             | 2.3.1 Constraint of Sequence-Pair                          | .0  |  |  |  |  |

|                   |                             | 2.3.2 Best Packing Under the Constraint                    | .0  |  |  |  |  |

|                   |                             | 2.3.3 P-admissible Solution Space                          | . 1 |  |  |  |  |

|                   | 2.4                         | Use of Sequence-Pair                                       | .3  |  |  |  |  |

|                   |                             | 2.4.1 Rectangle Packing                                    | 3   |  |  |  |  |

|                   |                             | 2.4.2 Module Placement with Wires                          | .4  |  |  |  |  |

|                   | 2.5                         | Conclusion                                                 | .6  |  |  |  |  |

| 3                 | Maj                         | oping from Sequence-Pair to Rectangular-Dissection 1       | 8   |  |  |  |  |

|                   | 3.1                         | Introduction                                               | 8.  |  |  |  |  |

|                   | 3.2                         | Preliminary                                                | .9  |  |  |  |  |

|                   |                             |                                                            | 9   |  |  |  |  |

|                   |                             | 3.2.2 Sequence-Pair                                        | .9  |  |  |  |  |

|                   |                             | 3.2.3 Rectangular-Dissection                               | 1:  |  |  |  |  |

|                   |                             | 3.2.4 Sequence-Pair and Rectangular-Dissection             | :2  |  |  |  |  |

|                   | 3.3                         | Rectangular-Dissection without Empty Room                  | :4  |  |  |  |  |

|                   |                             | 3.3.1 HV-Cross and Adjacent-Cross                          | :4  |  |  |  |  |

|                   |                             | 3.3.2 Converting Sequence-Pair into Rectangular-Dissection | 25  |  |  |  |  |

|                   |                             | 3.3.3 Necessary and Sufficient Condition                   | 29  |  |  |  |  |

|                   | 3.4                         |                                                            | 80  |  |  |  |  |

|                   |                             | 3.4.1 Removing Adjacent-Crosses                            | 80  |  |  |  |  |

|                   |                             | 3.4.2 Maximum Number of Empty Rooms                        | 3   |  |  |  |  |

|              | 3.5    | Conclu  | ısion                                                                                                                                                                 | 33   |

|--------------|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4            | Rec    | tangle  | Packing with Obstacles                                                                                                                                                | 35   |

|              | 4.1    | Introd  | $ \stackrel{-}{\text{uction}} \stackrel{-}{\ldots} \dots \dots$ | 35   |

|              | 4.2    | Prelim  | inary                                                                                                                                                                 | 36   |

|              |        | 4.2.1   | Rectangle Packing with Pre-Placed Rectangles (RPP)                                                                                                                    | . 36 |

|              |        | 4.2.2   | Sequence-Pair                                                                                                                                                         | . 36 |

|              |        | 4.2.3   | Feasibility of Sequence-Pair                                                                                                                                          |      |

|              | 4.3    | Adapt   | ation                                                                                                                                                                 |      |

|              |        | 4.3.1   | Necessary Condition                                                                                                                                                   |      |

|              |        | 4.3.2   | Algorithm                                                                                                                                                             |      |

|              |        | 4.3.3   | Illustrative Example                                                                                                                                                  |      |

|              |        | 4.3.4   | Proof of Adaptation                                                                                                                                                   |      |

|              | 4.4    | Use of  | Adaptation                                                                                                                                                            |      |

|              |        | 4.4.1   | RPP Example                                                                                                                                                           |      |

|              |        | 4.4.2   | Place and Route Example                                                                                                                                               |      |

|              | 4.5    | Conclu  | ısion                                                                                                                                                                 |      |

| 5            | Cor    | clusion | n                                                                                                                                                                     | 49   |

| $\mathbf{R}$ | efere  | nces    |                                                                                                                                                                       | 50   |

| Ρı           | ublic. | ations  |                                                                                                                                                                       | 52   |

## Chapter 1

## Introduction

## 1.1 Rectangle Packing Problem

Layout in physical design of VLSI is, simply to say, to pack all the circuit elements in a chip without violating the design rules, so that the circuit performs well and the production yield is high. Among the variety of targets in different stages, the problem defined as follows is the base of all of them.

#### Rectangle Packing Problem: RP

Let  $\mathcal{M}$  be a set of n rectangular modules whose heights and widths are given in real numbers. (Orientations are fixed.) A packing of  $\mathcal{M}$  is a non-overlapping placement of all the modules. The minimum bounding rectangle of a packing is called the chip. Find a packing of  $\mathcal{M}$  in a chip of the minimum area.

Notice that  $\mathbf{RP}$  is not simply a combinatorial optimization problem since the heights and widths of modules are arbitrary real numbers. It will be shown in this thesis that the problem belongs to the  $\mathcal{NP}$ -hard class.

#### 1.2 Previous Researches

Similar problems have been studied from mathematical interests [1, 2, 3, 4, 5], but they are far from real applications in VLSI layout design. In VLSI design, deterministic algorithms have been used based on heuristic ideas [6, 7], but they easily fall in a non-global local-optimum. An alternative approach is to use stochastic searches, such as simulated annealing and genetic algorithm. A stochastic search is known to have a potential for finding one of the best solutions in the "solution space" in a controlled time [8, 9].

To apply a stochastic search, it is required to reduce the problem into a combinatorial level by introducing a discrete solution space. A solution space is a set of codes, each of which represents a construction of placement. A stochastic search is to explore the solution space randomly and heuristically to find a good solution, and to output the best found solution by the end of the given limit of time. However, if the solution space does not include any optimal solution, the found solution cannot be optimal. Unfortunately, an optimal solution is not guaranteed to be included in the most of known solution spaces [10, 11, 12]. The solution space proposed by Onodera, Taniguchi and Tamaru [13] includes an optimal solution but also includes infeasible solutions, thus it is not useful

for a stochastic search. (They uses an exhaustive algorithm, but the size of the tractable problem is limited up to six modules.)

The discussion above concludes that the key issue is to invent a solution space which includes an optimal solution but excludes all the infeasible solutions. Such a solution space is said to be P-admissible in this research, though there is no known example for the rectangle packing problem.

#### 1.3 Thesis Outline

The main contribution of this thesis is finding a P-admissible solution space for the rectangle packing problem. The solution space is defined as follows. A pair of module name sequences (for example, (abcd, bdac) for modules a, b, c and d) is called a sequence-pair. It is defined that sequence-pair implies a horizontal/vertical (right of, left of, below, above) relation for every pair of modules m and m', depending on whether m is {before, after} m' in the {first, second} sequence. A compaction procedure is given so that it makes a sequence-pair corresponds to a best packing of all the packings that satisfy the implied horizontal/vertical relations. The set of all the sequence-pairs, thus of the cardinality  $(n!)^2$ , is our solution space. The P-admissibility of this solution space is proved in detail in this thesis. In experiments using the data abstracted from industrial examples, hundreds of modules are effectively packed. Furthermore, to see how the method is promising, an example of tens of modules is shown to be placed with a conventional wiring consideration method.

A sequence-pair represents a non-overlapping placement of modules, but by nature it does not represent any wiring channel. This could be a difficulty in applying the method to IC layout in which the placement is followed by a channel router. In previous researches, a rectangular dissection has been used to represent relative positions of channels as well as relative positions of modules. As a complementary contribution to the sequence-pair method, we give a mapping from a sequence-pair to a rectangular dissection, introducing the minimum number of channels to preserve the information on module positions. The tight upper bound of the number of introduced channels is given with detailed proofs.

As a practical contribution of this thesis, further consideration is devoted to cope with a specific requirement in PCB/VLSI design. In typical PCBs, there are obstacles such as holes and connectors. The obstacles are often found also in VLSI design, for example, pre-placed macro cells. To eliminate the modules being overlapped with such obstacles, these obstacles can be modeled as "pre-placed modules" and included in a sequence-pair. However, it is not guaranteed that such a sequence-pair can recover the assigned coordinates of the pre-placed modules. A procedure is presented to change an arbitrary sequence-pair to fit such environments.

This thesis is organized as follows. In Chapter 2, the sequence-pair is introduced and its P-admissibility is proved. In Chapter 3, a mapping from a sequence-pair to a rectangular-dissection is provided to generate channel information. Chapter 4 is devoted to present an adaptation procedure to tailor the solution space for the obstacles. Finally, Chapter 5 concludes this research with remarks.

#### 1.4 Remarks

The Sequence-Pair idea was born in a research discussion in Kajitani-lab, Japan Advanced Institute of Science and Technology, in 1994, inspired by another idea, called Bounded-Sliceline-Grid (BSG), which is a uniform grid structure but specially designed for VLSI module placement problems. Since then, they have been working together to develop the BSG method and the Sequence-Pair method in parallel, as is listed in the publications section. However, this thesis rarely describes about BSG method, since theory of the sequence-pair is discussed in a complete and closed form. The birth and growth of the BSG and the Sequence-Pair in the very early stage are described in [15] which was written by the then Advisor Professor Y. Kajitani.

## Chapter 2

# Rectangle Packing Solution Space Composed of Sequence-Pairs

#### 2.1 Introduction

Layout in physical design of VLSI is, in short, to pack all the circuit elements in a chip without violating design rules, so that the circuit performs well and the production yield is high. There are so much variety of targets in different stages but the following problem is the core of them.

#### Rectangle Packing Problem: RP

Let  $\mathcal{M}$  be a set of n rectangular modules of fixed orientations, whose heights and widths are given in real numbers. A packing of  $\mathcal{M}$  is a non-overlapping placement of the modules. The minimum bounding rectangle of a packing is called the chip. Find a packing of  $\mathcal{M}$  onto a chip of the minimum area.

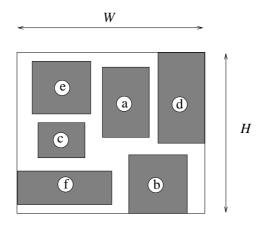

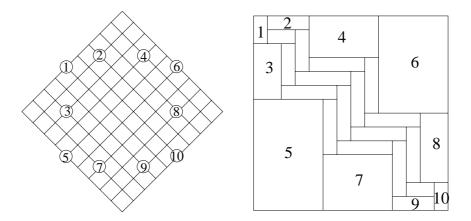

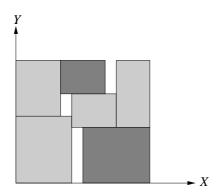

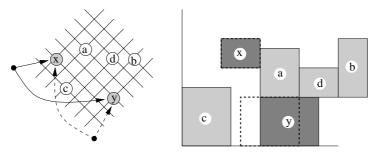

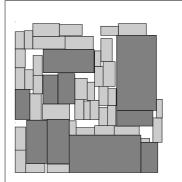

A packing of six modules is shown in Fig. 2.1.

The decision version of our problem  $\mathbf{RP}(\mathbf{A})$  is to decide whether  $\mathcal{M}$  can be packed onto a chip of area A. Baker, Coffman and Rivest [1] proved the  $\mathcal{NP}$ -completeness of a similar problem  $\mathbf{RP}(\mathbf{H}, \mathbf{W})$ : decide whether  $\mathcal{M}$  can be packed onto the chip of height H and width W. We can show  $\mathbf{RP}(\mathbf{A})$  to be  $\mathcal{NP}$ -complete using the fact that any instance of  $\mathbf{RP}(\mathbf{H}, \mathbf{W})$  can be polynomially reducible to an instance of  $\mathbf{RP}(\mathbf{A})$  by the following conversion.

$$\begin{array}{lll} r & \leftarrow & \frac{\text{the maximum width over modules}}{2H} \\ A & \leftarrow & (W+rH)(W+2rH) \\ \mathcal{M}' & \leftarrow & \{ \; (w\times rh) \; \mid \; \forall \; (w\times h) \in \mathcal{M} \} & \cup & \{ \; rH\times rH \; , \; (W+rH)\times (W+rH) \; \} \end{array}$$

Our problem  $\mathbf{RP}$  is harder than  $\mathbf{RP}(\mathbf{A})$ , so  $\mathcal{NP}$ -hard.

Since the heights and widths of modules are real numbers, **RP** is not simply a combinatorial optimization problem. In fact, there have been several numerical approaches [6, 7]. They first generate a possibly overlapping arrangement of modules, and then move modules to reduce the overlapping cost. But the overlap elimination is very hard for the numerical approaches without ad-hoc post-processing.

An alternative approach is "combinatorial search". In this approach, a set of codes is defined as a *solution space*. Each code represents a construction of placement. A code is

said to be feasible if the construction is consistent, i.e. there exists a packing corresponding to the code. The evaluation of a feasible code is the area of the chip, and the evaluation of an infeasible code is infinitely negative. The combinatorial search aims at finding a best code in the solution space. However, exhaustive search of the whole space will take too much time. Since the problem is **NP**-hard, the size of any such solution space is expected to be exponential. Several heuristics have been proposed to find a good solution in a moderate time, for example, simulated annealing and genetic algorithms. Given a time limit, such a heuristic stops the search half-way and outputs the best solution found so far. For this search to be effective, the minimum requirement of the solution space is the following four items.

- (1) The solution space is finite.

- (2) Every solution is feasible.

- (3) Realization of a code is possible in polynomial time.

- (4) There exists a code which corresponds to one of the optimal solutions.

The solution space that satisfies the above four requirements is called *P-admissible*.

The reasons for (1),(3) and (4) are obvious. That for (2) is: most heuristics pick up one solution after another along the neighboring structure defined on the space, consulting with the difference of evaluations (gain) to the previous solution. Therefore, if infeasible solutions are included, the continuity will be destroyed and convergence to a feasible solution is not guaranteed.

A known practical solution space is one derived from the *slicing floorplan* proposed by Otten [10] and others. It satisfies (1), (2) and (3). Several optimization heuristics are applied for the space, and one of the most successful approaches uses simulated annealing [8]. However, since the optimal solution can be non-slicing, (4) is not satisfied. This fact discourages us to start searching for the best in the space. Efforts have been paid to let the space include non-slicing structures [12, 11], but they have not been successful to satisfy (4). (Still, a merit of the slicing structure is in the channel routing stage [16].)

Another approach is proposed by Onodera, Taniguchi and Tamaru [13]. They construct a solution space by assigning one out of the four relations, "left of", "right of", "above", and "below", to every pair of modules. This space satisfies (4) since any packing satisfies a combination of the relations. But there are many infeasible codes such as; module a is left of module b, b is left of c and c is left of a. Thus their space is not P-admissible either. As a consequence, the space does not admit heuristics such as simulated annealing. In their paper, exhaustive search with a branch-and-bound technique is applied to find an exactly optimal solution, but the size of tractable problems is limited up to six modules.

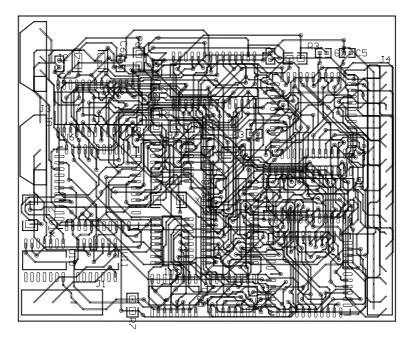

This chapter provides a P-admissible solution space, in which each code is a pair of module name sequences. By searching this space, it has become possible to pack hundreds of modules efficiently, as demonstrated in Fig. 2.9 and Fig. 2.10.

To utilize this solution space of **RP** for VLSI layout design, the evaluation of a packing has to be modified to consider wires. Some evaluating functions are available for estimating the final chip area [8, 13]. Among them, we use the formula proposed in [13]. The largest MCNC building-block benchmark was successfully placed by simulated annealing in about 30 minutes (Fig. 2.11).

Figure 2.1: A packing on a chip of area  $H \times W$

This chapter is organized as follows. In Section 2.2, a mapping from a given packing to a pair of module name sequences is given. It is proved that at least one of the optimal solutions is included in the space. Section 2.3 provides a procedure for an inverse mapping from a sequence pair to a packing. Section 2.4 demonstrates how the space can be utilized in VLSI placement problems. Section 2.5 then concludes with final remarks.

#### 2.2 From Packing to Sequence-Pair

Let  $\Pi$  be a packing on chip C. See Fig. 2.1 for an example. We describe a procedure called **Gridding**, which encodes  $\Pi$  to a sequence-pair, an ordered pair of module name sequences.

#### 2.2.1 Gridding

A rectangular dissection is a partition of C into rectangles, called rooms, such that a room contains at most one module. A room which contains no module is said to be empty.

The line segments forming the room boundaries (including four sides of C) are called the *cutting-segs*. We assume that a cutting-seg, except for four sides of C, stops at an inside point of an orthogonal cutting-seg (forming a T-intersection). It is trivial that such a rectangular dissection always exists.

In the following, we describe a procedure to get a pair of module name sequences from a packing.

#### procedure: Gridding( $\Pi$ )

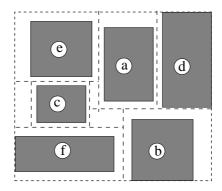

Obtain one arbitrary rectangular dissection and fix it. (See Fig.2.2 which is an example rectangular dissection corresponding to  $\Pi$  in Fig.2.1.) Take a

Figure 2.2: A rectangular dissection of a packing

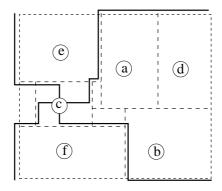

Figure 2.3: Loci of module c

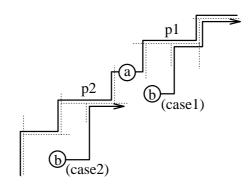

non-empty room. Put a pebble p at the center of the room. Move it right up to hit the cutting-seg which is the side of the room. Then, move p upward until to hit an orthogonal cutting-seg. Then, move it right to hit an orthogonal cutting-seg, and continue turning its direction as right, up, right, up, ..., until to reach the upper right corner of the chip. The locus of pebble p is called the right-up locus of the module. Similarly, up-left locus, left-down locus, and down-right locus are defined. (Fig.2.3 shows these four loci of one module.)

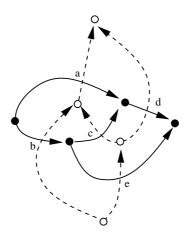

The union of right-up locus of x and left-down locus of x is called the *positive* locus (since it tends to go inside the 1st and 3rd quadrants). Analogously, the union of the up-left locus of x and down-right locus of x is called the negative locus. For every module, one positive locus and one negative locus are uniquely defined. They are referred to by the corresponding module names. (An example with all loci is shown in Fig.2.4.)

#### Theorem 1:

No pair of positive loci crosses each other. No pair of negative loci crosses each other. (They may run along the same cutting-segs, but not cross each other.)

Figure 2.4: Positive loci (left) and negative loci (right), resulted in  $(\Gamma_+, \Gamma_-) = (ecadfb, fcbead)$

Figure 2.5: Loci used in the proof of Theorem 1

**Proof:** Let two modules be a and b. Since positive loci of a and b cannot be inside the other room, a crossing, if any, would occur outside their rooms. Denote the right-up locus of module a be RU(a). Similar notation is applied for the other three types loci.

Suppose that RU(b) comes from below and hits RU(a) at a point  $p_1$ . See Fig.2.5 case 1. Since RU(a) and RU(b) are along cutting-segs, RU(b) cannot cross RU(a) at  $p_1$  by definition of the cutting-seg. After  $p_1$ , the two must run for a while. Since they are following the same rule of right-up locus, they run together and never cross each other. Hence, right-up loci of a and b do not cross. By the same reason, left-down loci of a and b do not cross.

Suppose that RU(b) comes from below and hits LD(a) at a point  $p_2$ . See Fig.2.5 case 2. After  $p_2$ , RU(b) goes right upstream along LD(a) for a while. Then RU(b) reaches to the point where LD(a) comes from above. After that point, RU(b) continues to go right and thus goes below of LD(a) again. Since RU(b) can not go inside the room of a, it goes below of the room of a. Hence, left-down locus of a and right-up locus of b do not cross. By the same reason, right-up locus of a and left-down locus of b do not cross.

Then, the positive loci of a and b do not cross. Similarly, negative loci of a and b do not cross.

The implication of the theorem is significant: n positive loci are linearly ordered, and

so are negative loci. Here we order the positive loci from upper left, and order the negative loci from lower left. Since each locus is uniquely referred to by the module name, we have obtained an ordered pair of module name sequences  $(\Gamma_+, \Gamma_-)$ , which we call sequence-pair, where  $\Gamma_+$  (resp.  $\Gamma_-$ ) is a module name sequence which represents the order of positive (resp. negative) loci.

In Fig.2.4, positive loci are in order "ecadfb" and negative loci are in order "fcbead", then  $(\Gamma_+, \Gamma_-) = (ecadfb, fcbead)$  is obtained.

Given packing  $\Pi$ , the resultant  $(\Gamma_+, \Gamma_-)$  obtained by **Gridding** is denoted **Gridding** $(\Pi)$ .

#### 2.2.2 Geometrical Information of Sequence-Pair

Let  $(\Gamma_+, \Gamma_-)$  be the sequence-pair produced by **Gridding** for a packing  $\Pi$ . Modules x and x' are related in exactly one of four ways: x' is after/before x in  $\Gamma_+/\Gamma_-$ . Let us define four disjoint subsets of  $\mathcal{M}$ , accordingly.

$$\mathcal{M}^{\mathrm{aa}}(x) = \{x' \mid x' \text{ is after } x \text{ in both } \Gamma_+ \text{ and } \Gamma_-\},$$

$$\mathcal{M}^{\mathrm{bb}}(x) = \{x' \mid x' \text{ is before } x \text{ in both } \Gamma_+ \text{ and } \Gamma_-\},$$

$$\mathcal{M}^{\mathrm{ba}}(x) = \{x' \mid x' \text{ is before } x \text{ in } \Gamma_+ \text{ and after } x \text{ in } \Gamma_-\},$$

$$\mathcal{M}^{\mathrm{ab}}(x) = \{x' \mid x' \text{ is after } x \text{ in } \Gamma_+ \text{ and before } x \text{ in } \Gamma_-\}.$$

For example, with respect to the sequence-pair  $(\Gamma_+, \Gamma_-) = (ecadfb, fcbead)$ , four subsets for module c are:  $\mathcal{M}^{aa}(c) = \{a, b, d\}$ ,  $\mathcal{M}^{bb}(c) = \emptyset$ ,  $\mathcal{M}^{ba}(c) = \{e\}$ , and  $\mathcal{M}^{ab}(c) = \{f\}$ .

Any module other than x belongs to a unique subset, and it is trivial that two modules are in a dual relation through  $x \leftrightarrow x'$ , and  $a \leftrightarrow b$  as:

$$x' \in \mathcal{M}^{aa}(x) \Leftrightarrow x \in \mathcal{M}^{bb}(x')$$

$x' \in \mathcal{M}^{ba}(x) \Leftrightarrow x \in \mathcal{M}^{ab}(x')$

In a packing, if the right side of module x is left of the left side of module x', x is said to be *left of* x'. Similarly, *right of*, *above*, *below* relations between two modules are defined.

#### Theorem 2:

Let  $(\Gamma_+, \Gamma_-)$  be the sequence-pair produced by **Gridding** for a packing  $\Pi$ . If  $x \in \mathcal{M}^{bb}(x')$ , then x is left of x' in  $\Pi$ . The claim also holds when the pair of words (" $\mathcal{M}^{bb}$ " and "left of") is replaced by any of (" $\mathcal{M}^{aa}$ " and "right of"), (" $\mathcal{M}^{ba}$ " and "above"), and (" $\mathcal{M}^{ab}$ " and "below").

In the previous example, module b is in  $\mathcal{M}^{aa}(c)$ . One can examine b is actually right of c in the packing shown in Fig. 2.1.

**Proof:** Let x and x' be arbitrary two modules. The loci of x divide the chip into four regions. Among them, the region surrounded by the up-right locus of x and right-down locus of x together with the right side of the chip is called the right-cone of x. Analogously, the left-, above-, and below-cone denote the other three regions.

Suppose x' is in  $\mathcal{M}^{\mathrm{aa}}(x)$ . This implies that the positive locus of x' is in the union of the right-cone and the below-cone of x. Also it is implied that the negative locus of x' is in the union of the right-cone and the above-cone of x. The cross point of the positive locus and the negative locus of x' is in their intersection, that is, the right-cone of x. Then, module x' is in the right-cone of x. Every modules in the right-cone of x is right of module x by definition of the up-right locus and the right-down locus of x.

It is clear that the claim holds for the other cases.

## 2.3 From Sequence-Pair to Packing

In the previous section, we analyzed the packing and fixed the procedure **Gridding** to obtain one sequence-pair from a given packing. Now we provide a procedure to synthesize one packing from an arbitrary sequence-pair.

#### 2.3.1 Constraint of Sequence-Pair

Given a sequence-pair  $(\Gamma_+, \Gamma_-)$ , we read a constraint from it as follows.

#### The Constraint Implied by a Sequence-Pair $(\Gamma_+, \Gamma_-)$

If  $x \in \mathcal{M}^{bb}(x')$ , module x must be left of module x'. This is also the constraint with replacing the pair of words (" $\mathcal{M}^{bb}$ " and "left of") with any of (" $\mathcal{M}^{aa}$ " and "right of"), (" $\mathcal{M}^{ba}$ " and "above"), and (" $\mathcal{M}^{ab}$ " and "below").

It is easily seen that the constraint imposed on the packing by a sequence-pair is unique. Furthermore, the following theorem holds.

**Theorem 3**: The constraint is always satisfiable.

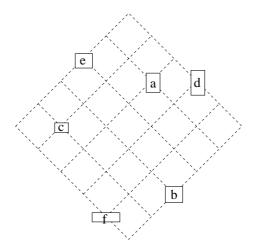

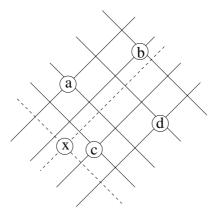

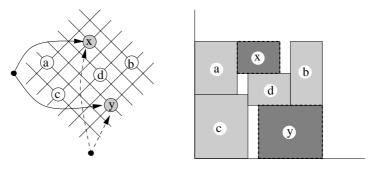

**Proof:** Consider an  $n \times n$  grid. Label the horizontal grid lines and vertical grid lines with module names along  $\Gamma_+$  and  $\Gamma_-$  from top and from left, respectively. A cross point of the horizontal grid line of label x and the vertical grid line of label x' is referred to by (x, x'). Then, rotate the resultant grid by 45 degrees counter clockwise to get an oblique grid. (See Fig. 2.6.) Put each module x with its center being on (x, x). Expand the separation of grid lines  $\sqrt{2}$  times larger than the longest width/height over modules, which is sufficient to eliminate overlapping of modules. The resultant packing trivially satisfies the constraint implied by the given sequence-pair.

An example is shown in Fig. 2.6.

#### 2.3.2 Best Packing Under the Constraint

Given  $(\Gamma_+, \Gamma_-)$ , one of the optimal packings under the constraint can be obtained in  $O(n^2)$  time by applying the well-known longest path algorithm for vertex weighted directed acyclic graphs. The process is given below.

Based on "left of" constraint of  $(\Gamma_+, \Gamma_-)$ , a directed and vertex-weighted graph  $G_H(V, E)$  (V: vertex set, E: edge set), called the *horizontal-constraint graph*, is constructed as follows.

Figure 2.6: A packing on an oblique grid for  $(\Gamma_+, \Gamma_-) = (ecadfb, fcbead)$

V: source s, sink t, and n vertices labeled with module names

$E:(s,x) \text{ and } (x,t) \text{ for each module } x, \text{ and } (x,x') \text{ if and only if } x \in \mathcal{M}^{\text{bb}}(x') \text{ ("left of" constraint)}$

Vertex-weight: zero for s and t, width of the corresponding module for the other vertices

Similarly the vertical-constraint graph  $G_V(V, E)$  is constructed using "below" constraint and the height of each module.

Neither of these graphs contains any directed cycle. We set the X-coordinate of x to be the longest path length from s to x in  $G_H$ . The Y-coordinate of x is set independently using  $G_V$ . If two modules x and x' are in horizontal relation, then there is an edge between x and x' in  $G_H$ , hence they do not overlap horizontally in the resultant placement. Similarly, if x and x' are in vertical relation, they do not overlap vertically. Thus no two modules overlap each other in the resultant placement because any pair of modules is either in horizontal or vertical relation.

The width and the height of the chip is determined by the longest path length between the source and the sink in  $G_H$  and  $G_V$ , respectively. Since the width and the height of the chip is independently minimum, the resultant packing is the best of all the packings under the constraint. The longest path length calculation on each graph can be done in  $O(n^2)$  time, proportional to the number of edges in the graph.

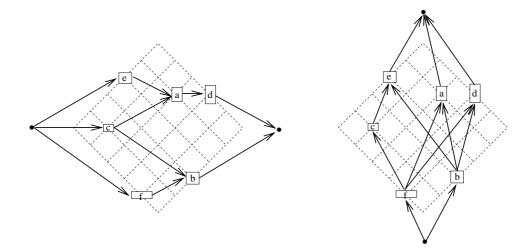

As an example,  $G_H$  and  $G_V$  are shown in Fig. 2.7 for  $(\Gamma_+, \Gamma_-) = (ecadfb, fcbead)$ . The resultant placement after the longest path length calculation is shown in Fig. 2.8.

#### 2.3.3 P-admissible Solution Space

Previous discussions conclude:

Figure 2.7: Constraint graphs  $G_H(\text{left})$  and  $G_V(\text{right})$  (transitive edges are not drawn for simplicity)

Figure 2.8: A best packing under the constraint implied by  $(\Gamma_+, \Gamma_-) = (ecadfb, fcbead)$

**Theorem 4**: The set of all sequence-pairs is a P-admissible solution space of **RP**. More precisely, it consists of  $(n!)^2$  sequence-pairs, each of which can be mapped to a packing in  $O(n^2)$  time, and at least one of which corresponds to one of the optimal solutions of **RP**.

Our discussion started for minimizing the area of the chip. However, all the discussions hold as long as the evaluating function is independently non-decreasing with respect to the width and the height of the chip. Therefore we may assume instead, for example, perimeter of the chip, area of the chip of pre-specified aspect ratio, and the height of the chip when its width is fixed. This fact will extend the usefulness of our solution space.

It has also been assumed that the orientation of each module (vertically laid or horizontally laid) is fixed. When the orientation is also requested to be optimized, we hold a  $\{0,1\}$  sequence of length n, expressing the orientation of each module being horizontal or vertical. The size of solution space increases to  $(n!)^2 2^m$ . (The orientation optimization for a fixed rectangular dissection is known to be NP-hard [17].) This technique can be easily extended to so-called "soft" modules, by preparing three or more candidates of (width, height) per module [18].

There is a sequence-pair for which another sequence-pair provides no worse packing, independent of the sizes of the modules. For example, if (abcd, cdab) corresponds to an optimal packing, then (abcd, cadb) or (acbd, cdab) also corresponds to an optimal packing, regardless of the widths and the heights of modules a, b, c and d. Then, the former sequence-pair, (abcd, cdab), is redundant for our current objective to find a packing with smaller area. We extend our evaluating function to consider wires in the next section.

## 2.4 Use of Sequence-Pair

#### 2.4.1 Rectangle Packing

We use a standard simulated annealing method to pack rectangles. It uses two kinds of pair-interchanges: (i) two module names in  $\Gamma_+$ , (ii) two module names in  $\Gamma_+$  and also in  $\Gamma_-$ . The initial sequence-pair was made at random. The temperature was decreased exponentially.

The first interest would be to know the experimental performance ratio (obtained area / optimal area) of the above described simulated annealing. For this purpose, two problem instances are constructed such that their optimal solutions are known.

**REGGRID**: a collection of 100 unit squares. It is easily understood that an optimal solution with area 100 is possible when the squares are packed in the  $10 \times 10$  regular grid.

**LOGGRID**: a collection of 100 rectangles, generated by an exponential grid formed by eleven vertical lines x = 0, 1, 2, 3, 5, 7, 10, 14, 19, 26, 36 and eleven horizontal lines y = 0, 1, 2, 3, 5, 7, 10, 14, 19, 26, 36. Thus, the area of the optimal solution is  $36 \times 36 = 1296$ .

The result is shown in Table 2.1. The calculation speed was  $0.78 \sim 0.80$  milliseconds per iteration on a Sun SS-5 with 75 MHz clock. From Table 2.1, the proposed method attained the area 1.2 times larger than the minimum in a moderate time.

| Number of iterations | REGGRID | LOGGRID |

|----------------------|---------|---------|

| 10000                | 1.44    | 1.29    |

| 30000                | 1.32    | 1.33    |

| 100000               | 1.21    | 1.17    |

| 300000               | 1.3     | 1.17    |

| 1000000              | 1.08    | 1.20    |

| 3000000              | 1.20    | 1.14    |

| 10000000             | 1.1     | 1.11    |

| 30000000             | 1.1     | 1.14    |

Table 2.1: Performance ratio of 100 modules packing

To know the performance of the proposed method for "real" data, dimensions of 146 modules were extracted from a printed circuit board in a personal computer. The simulated annealing process is designed similarly, but we also include orientation optimization for this example: (i) two module names in  $\Gamma_+$ , (ii) two module names in  $\Gamma_+$  and also in  $\Gamma_-$ , (iii) the width and the height of a module, where the last one is for orientation optimization. The initial sequence-pair was made as  $\Gamma_+ = \Gamma_-$ , which corresponds to a linear horizontal arrangement of modules. From a heuristic point of view, operation (i) was selected with higher probability in higher temperature, and operation (iii) was selected with higher probability in lower temperature.

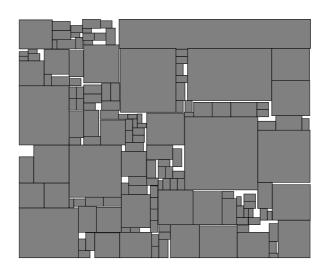

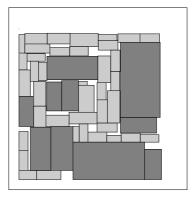

The result is shown in Fig. 2.9. Computation on Sun SS-2 stopped in 29.9 minutes reaching the terminating temperature. The algorithm searched at most 606,192 distinct sequence-pairs out of the solution space of size  $(146!)^2 2^{146} \sim 1.23 \times 10^{552}$ . Notice that, the search of only a fraction about  $4.92 \times 10^{-547}$  of the solution space was enough to obtain the placement shown in Fig. 2.9.

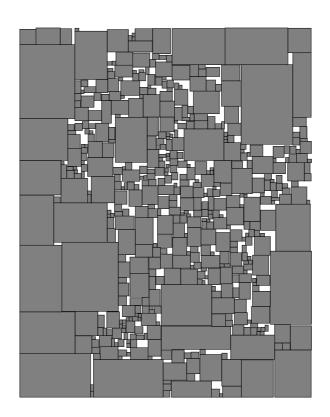

As another challenge, we tried 500 modules, using 18.83 hours on a Sun SS-2 to get the result shown in Fig. 2.10.

#### 2.4.2 Module Placement with Wires

For VLSI placement, we extend the evaluation to consider wires. Among various possible evaluations about wires, we focus on the final chip area after all wires are detailed-routed. However, it is difficult at this moment and hence we made use of an estimate of the final chip area without the actual routing phase.

Let  $(\Gamma_+, \Gamma_-)$  be a sequence-pair,  $\Pi$  be one of the optimal packings under the constraint implied by  $(\Gamma_+, \Gamma_-)$ , and W and H be the width and the height of  $\Pi$ . Terminals are given as fixed points on the boundary of each module. A *net* is a set of terminals (multi-terminal net), which must be connected by wires, later in detailed-routing phase. A set of nets is given as the netlist  $\mathcal{N}$ . Given terminals of a net i, which spread over  $\Pi$ , the width and the height of the smallest bounding box of these terminals are denoted by  $W_i$  and  $H_i$ , respectively. T is the sum of wiring width and wiring space (obtained from a design rule set). We use the following formula proposed in [13] to estimate the final chip width W' and height H'.

Figure 2.9: Packing of 146 modules

Figure 2.10: Packing of 500 modules

$$W' = W + T \frac{\sum_{i \in \mathcal{N}} H_i}{H}$$

$$H' = H + T \frac{\sum_{i \in \mathcal{N}} W_i}{W}$$

The second term of each formula estimates the increase in one direction owing to the wires, assuming all wires are uniformly distributed in the final chip. They experimentally showed that the result is acceptable for a commercial channel router [13].

There are choices per module, which is the combination of the four choices of 0, 90, 180, 270 degree rotations, and a decision yes, no on reflecting the module about the Y axis. This code for orientation and a sequence-pair are put together into a simulated annealing process in our system. The process runs in a similar fashion as the rectangle packing optimization, and explores the solution space of size  $(n!)^2 8^n$ .

A point not mentioned in [13] is how the location of each individual module is calculated. In our system, after the best evaluated code is obtained, coordinates of each module are determined as follows. Assume  $(X_j, Y_j)$  is the coordinates of the lower left corner of module j in  $\Pi$ . (This is the information we can use in this phase.) Let  $\mathcal{N}_{X_j}$  be a set of nets such that the X coordinate of the left side of bounding box of the net is less than or equal to  $X_j$ . Similarly,  $\mathcal{N}_{Y_j}$  is defined using  $Y_j$ . We determine the coordinates  $(X'_i, Y'_i)$  of the lower left corner of module j in the resultant chip by the following formula.

$$X'_{j} = X_{j} + T \frac{\sum_{i \in \mathcal{N}_{X_{j}}} H_{i}}{H}$$

$$Y'_{j} = Y_{j} + T \frac{\sum_{i \in \mathcal{N}_{Y_{j}}} W_{j}}{W}$$

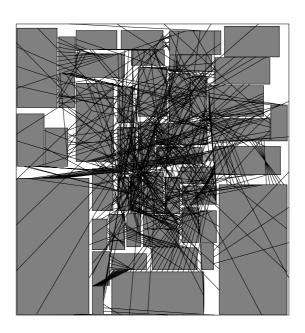

For an experiment, the biggest building block layout data, called "ami49", was taken from the MCNC benchmarks. The data is the biggest one in their benchmark suit, but our method was fast enough to handle the data without splitting the problem. (Some recent research [9] also handle the data without dividing the problem.) The result is shown in Fig. 2.11. We remark that it was done with an additional constraint: aspect ratio = 1, taking  $T=7~\mu m$ . The estimated chip size is 6482  $\mu m \times 6925~\mu m$ . Computation time was 31.36 minutes on SunIPX.

#### 2.5 Conclusion

This chapter introduced a data structure to represent a general packing in terms of a pair of module name sequences, called sequence-pair. Detailed proofs are presented to show that every sequence-pair feasibly corresponds to a packing, and at least one sequence-pair corresponds to an area-minimum packing.

In experiments, 500 rectangles were packed very efficiently in a reasonable time. It was attained by a standard simulated annealing in which a move is a change of the sequence-pair. The evaluating function was then extended to the VLSI placement problem using a conventional wiring area estimation method. The biggest MCNC benchmark, ami49, is placed very nicely.

Figure 2.11: Placement of MCNC "ami49"

## Chapter 3

# Mapping from Sequence-Pair to Rectangular-Dissection

#### 3.1 Introduction

In the first stage of VLSI physical design, it is required to determine a rough arrangement of circuit components, such as modules and channels. A stochastic algorithm, such as simulated annealing or genetic algorithm, would be a good choice as an optimization algorithm since the problem is hard. To make a stochastic algorithm work effectively, a fundamental issue is in how to represent candidate arrangements, with enough generality and efficiency to cope with various design requirements.

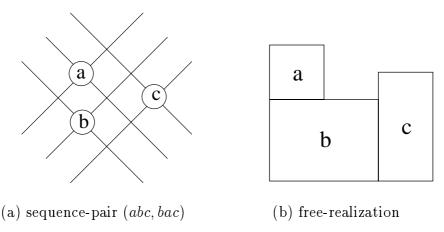

In Chapter 2, we proposed a representation called sequence-pair, which is a pair of module name sequences. For example, (abc, cab) is a sequence-pair for module set  $\{a, b, c\}$ . For a sequence-pair, they assigned an HV-relation-set (HVRS), which is a set of horizontal (right of/left of) or vertical (above/below) relations for every module pair. For example, sequence-pair (abc, cab) corresponds to HVRS  $\{a \text{ is left of } b, c \text{ is below } a, c \text{ is below } b\}$ . It is proved in the chapter that a sequence-pair always corresponds to a realizable HVRS, and there is a sequence-pair whose HVRS can lead an area minimum placement. However, HVRS alone is not sufficient as a representation of candidate arrangements of components. Channel positions are also desired to be represented together.

A traditional method exists to represent channel positions together with module positions. It is the rectangular-dissection. (sometimes called floorplan in the literature [17].) However, known efficient representation techniques are limited for specific classes of rectangular-dissections, such as slicing structure [8].

To combine the merits of sequence-pair and rectangular-dissection, it is desired to map a sequence-pair to a rectangular-dissection. Observe from Fig. 3.2-(a) that a room with no module assignment, called the *empty room*, is necessary in the rectangular-dissection to keep the relative positions of modules. It is worth allowing this empty room since it is essentially needed to achieve the area minimum placement. However, introducing arbitrary many empty rooms results in arbitrary many line segments, which represent channels.

This chapter gives a mapping from a sequence-pair to a rectangular-dissection whose number of rooms is minimum among all the rectangular-dissections whose HVRSs are equivalent to the HVRS of the given sequence-pair. Consequently, candidate arrangements of modules and channels are successfully represented with the generality and the efficiency

inherited from the sequence-pair.

The organization of this chapter is as follows. Section 3.2 defines preliminary terms. Section 3.3 shows a necessary and sufficient condition that a sequence-pair is mapped to a rectangular-dissection with no empty room. Section 3.4 presents a procedure to output a rectangular-dissection with fewest empty rooms. Section 3.5 is for conclusion.

## 3.2 Preliminary

#### 3.2.1 HV-Relation-Set

An HV-relation-set for a set of modules is a set of horizontal (right of / left of) or vertical (above/below) relations for all module pairs. For example,

$$\{a \text{ is left of } b, c \text{ is below } a, c \text{ is below } b\}$$

is an HVRS for module set  $\{a, b, c\}$ . The cardinality of an HVRS is  $\binom{n}{2}$ , where n is the number of modules. The variety of HVRS is  $4^{\binom{n}{2}}$ .

An HVRS may or may not be realizable. The above example is realizable. A non-realizable example is:  $\{a \text{ is left of } b, b \text{ is left of } c, c \text{ is left of } a\}$ . A branch and bound approach [13] can be used to eliminate non-realizable HVRSs.

#### 3.2.2 Sequence-Pair

A sequence-pair is an ordered pair of  $\Gamma_+$  and  $\Gamma_-$ , where each of  $\Gamma_+$  and  $\Gamma_-$  is a sequence of names of given n modules. For example,  $(\Gamma_+, \Gamma_-) = (abcd, bdac)$  is a sequence-pair of module set  $\{a, b, c, d\}$ . If module x is the i'th module in  $\Gamma_+$ , we denote  $\Gamma_+(i) = x$ , as well as  $\Gamma_+^{-1}(x) = i$ . A similar notation is used also for  $\Gamma_-$ . To help intuitive understanding, we use a notation such as

$$(\Gamma_+, \Gamma_-) = (\cdots a \cdots b \cdots, \cdots a \cdots b \cdots)$$

by which we mean

$$\Gamma_+^{-1}(a) < \Gamma_+^{-1}(b) \quad \text{and} \quad \Gamma_-^{-1}(a) < \Gamma_-^{-1}(b).$$

A sequence-pair corresponds to an HVRS as follows. For every module pair  $\{a, b\}$ , a is left of b (equivalently, b is right of a) if

$$(\Gamma_{\perp}, \Gamma_{\perp}) = (\cdots a \cdots b \cdots \cdots a \cdots b \cdots).$$

Similarly, a is below b (equivalently, b is above a) if

$$(\Gamma_+, \Gamma_-) = (\cdots b \cdots a \cdots, \cdots a \cdots b \cdots).$$

For example, sequence-pair (abcd, bdac) implies HVRS:  $\{b \text{ is below } a, b \text{ is left of } d, d \text{ is below } c, a \text{ is left of } c, d \text{ is below } a, b \text{ is left of } c\}$ .

The variety of HVRS represented by the sequence-pair equals to the variety of the sequence-pair,  $(n!)^2$ , thus drastically reduced from the original variety  $4^{\binom{n}{2}}$ , where n is the number of modules. Furthermore, the sequence-pair has the following property.

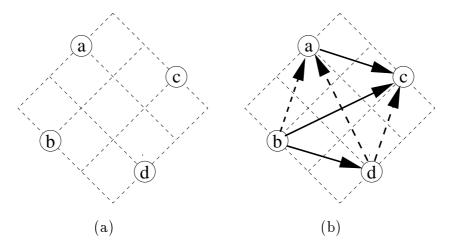

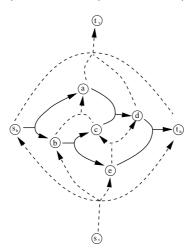

Figure 3.1: (a) Sequence-Pair (abcd, bdac), (b) Horizontal-Seq-Pair-Graph (H-SPG) and Vertical-Seq-Pair-Graph (V-SPG). The edges of H-SPG are drawn in solid lines and the edges of V-SPG are drawn in dotted lines.

**Property 1**: The HVRS of every sequence-pair is realizable. For any non-overlapping placement, there is a sequence-pair whose HVRS is satisfied by the placement. □

A proof is given in Chapter 2.

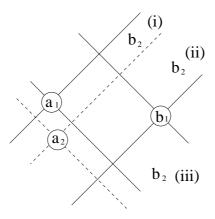

The HVRS of a sequence-pair of n modules can be graphically understood by means of oblique-grid, defined as follows. Let  $L_+(1), L_+(2), \cdots, L_+(n)$  be n parallel lines of slope +1 drawn on a plane, ordered from left. Let  $L_-(1), L_-(2), \cdots, L_-(n)$  be n parallel lines of slope -1 drawn on the plane, also ordered from left. These 2n lines form a 45 degree oblique  $n \times n$  grid, called the oblique-grid. The oblique-grid-embedding of a sequence-pair  $(\Gamma_+, \Gamma_-)$  is the oblique-grid with each module name x written at the cross point of  $L_+(\Gamma_+^{-1}(x))$  and  $L_-(\Gamma_-^{-1}(x))$ . Fig. 3.1-(a) shows the oblique-grid-embedding of sequence-pair (abcd, bdac). Using the oblique-grid-embedding, the HVRS of a sequence-pair can be re-defined as: for each module x, the modules which are seen from x in the angle between -45 degree and 45 degree are right of x, the modules in the angle between 45 degree and 135 degree are above x, and so on.

The HVRS of a sequence-pair is represented by a pair of directed acyclic graphs, called horizontal-sequence-pair-graph (H-SPG) and vertical-sequence-pair-graph (V-SPG), defined as follows. For either graph, vertices uniquely correspond to modules and have the corresponding module names. The edge set of the H-SPG is constructed faithfully to the horizontal relations, from left to right, but eliminating the transitive edges. The edge set of the V-SPG is defined similarly from bottom to top. We sometime abbreviate the pair of H-SPG and V-SPG of a sequence-pair to "SPGs".

Oblique-grid-embedding of a sequence-pair with arrows additionally drawn corresponding to the edges of the SPGs is called the oblique-grid-embedding of the SPGs. Fig. 3.1-(b) shows an example, where the edges of the H-SPG are drawn using solid lines, and the edges of the V-SPG are drawn using dotted lines.

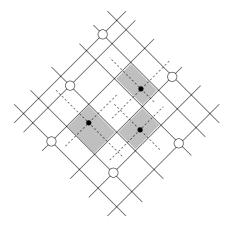

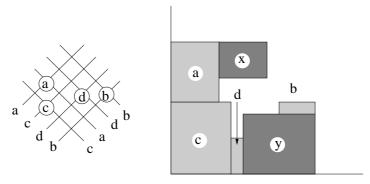

#### 3.2.3 Rectangular-Dissection

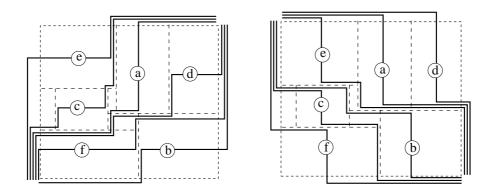

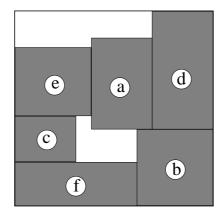

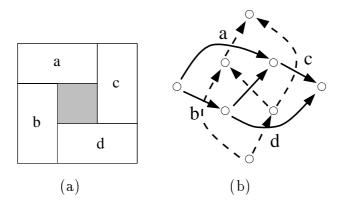

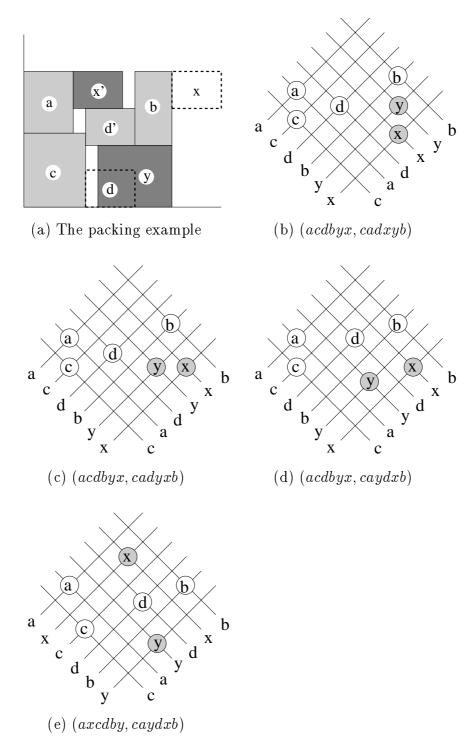

A rectangular-dissection is a dissection of a rectangle into a set of rectangles, called rooms, with an injective assignment of modules to rooms (no two modules share a room.) An example is shown in Fig. 3.2-(a). Only T-intersections are used to form the dissection except for the four corners of the bounding rectangle. (Two T-intersections may form a cross shape as a degenerate case.) The bounding rectangle represents the chip, each room represents an area which is assignable to a module, and each line segment represents a channel. A room is said to be occupied if a module is assigned to the room, otherwise said to be empty. In Fig. 3.2-(a), the dark room at the center is empty and the other rooms are occupied. Empty rooms have been used to modify a rectangular-dissection incrementally [19].

A rectangular-dissection specifies relative positions of modules and channels as follows: If the right side of a room  $r_a$  and the left side of a room  $r_b$  are both on an identical vertical line segment  $l_c$ , the module a assigned to the room  $r_a$  should be placed left of the channel c corresponding to the line segment  $l_c$ , and the module b assigned to the room  $r_b$  should be placed right of the channel c (horizontal relation). Notice that a horizontal relation between module pair a, b is transitively specified as: module a should be placed left of module b. Vertical relations are specified similarly using horizontal line segments.

The information of a rectangular-dissection is commonly represented by means of a pair of directed acyclic graphs [20, 21, 17], a horizontal-rectangular-dissection-graph (H-RDG) and a vertical-rectangular-dissection-graph (V-RDG). Each vertical (horizontal) line segment corresponds to a vertex in the H-RDG (V-RDG) and each room corresponds to an edge (u,v) where u is the vertex corresponding to the left (bottom) side of the room and v is the vertex corresponding to the right (top) side of the room. We sometime use the word "RDGs" to denote the pair of H-RDG and V-RDG of a rectangular-dissection. Two rectangular-dissections are said to be equivalent if their RDGs (the two H-RDGs, as well as the two V-RDGs) are the same. Fig. 3.2-(b) illustrates the RDGs of the rectangular-dissection shown in Fig. 3.2-(a). In the figure, the edges of H-RDG are drawn using solid lines, and the edges of V-RDG are drawn using dotted lines. An empty room corresponds to the anonymous edge in the figure.

H-RDG as well as V-RDG is a directed acyclic planar graph with possibly duplicated edges. Each RDG is polar, i.e. a directed acyclic graph with a single source and a single sink. Two polar graphs  $G_1$  and  $G_2$  are said to be in *polar-dual* relation if  $G_1$  and  $G_2$  become dual when an undirected edge from the source to the sink is added in each graph. From the construction, the RDGs are in polar-dual relation. The reverse is also true since polar-dual graphs are known to be mapped to a rectangular-dissection [21].

**Property 2**: Given two polar graphs  $G_1$  and  $G_2$ , there exists a rectangular-dissection whose RDGs are  $G_1$  and  $G_2$ , if and only if  $G_1$  and  $G_2$  are in polar-dual relation.

When we construct a rectangular-dissection from H-RDG  $G_h$  and V-RDG  $G_v$ , we use the following procedure.

#### **Procedure** ConstRD $(G_h, G_v)$

For a vertex  $u \in V(G_h)$ , x(u) denotes the ordinal number of the vertex u in a topological order of the vertices in  $G_h$ . (x(u)) has a unique integer such that x(u) < x(u') if there exists a path from u to u'). Similarly, y(v) denotes the ordinal number of the vertex v

Figure 3.2: (a) Rectangular-Dissection, (b) Horizontal-Rectangular-Dissection-Graph (H-RDG) and Vertical-Rectangular-Dissection-Graph (V-RDG). H-RDG is drawn in solid lines and V-RDG is drawn in dotted lines.

in a topological order of the vertices in  $G_v$ . A pair of edges  $(e_h, e_v)$  is called a "cross" if  $e_h (\in E(G_h))$  and  $e_v (\in E(G_v))$  are in a dual relation. For each cross  $((u_1, u_2), (v_1, v_2))$ , draw a rectangle whose lower left corner is at  $(x(u_1), y(v_1))$  and whose upper right corner is at  $(x(u_2), y(v_2))$ .

(Procedure ConstRD End)

It is easily seen that ConstRD runs in O(n) time, where  $n = |E(G_h)| = |E(G_v)|$  which also equals to the number of rooms in the resultant rectangular-dissection.

#### 3.2.4 Sequence-Pair and Rectangular-Dissection

The major merit of the sequence-pair and that of the rectangular-dissection are summarized as follows.

- The merit of the sequence-pair is in its efficiency in enumerating various HVRSs.

- The merit of the rectangular-dissection is in its ability of representing the channels.

To keep the two merits at the same time, the target of this chapter is:

**Target:** To map a sequence-pair to a rectangular-dissection.

The following three properties show a similarity of the sequence-pair and the rectangulardissection.

**Property 3**: Given a sequence-pair, for any two modules a and b, there is a path which connects a and b in H-SPG or in V-SPG, but not in both.

**Property 4**: In the H-RDG (V-RDG) of a rectangular-dissection, if there is a path from edge a to edge b, then the room a is left of (below) room b in the rectangular-dissection.

Property 3 and 4 are easily understood.

**Property 5**: Given a rectangular-dissection, for any two rooms a, b, there is a path which connects a and b in H-RDG or in V-RDG, and not in both.

**Proof:** Let G and G' be the H-RDG and V-RDG of the rectangular-dissection. Then G and G' are in polar-dual relation. Let source and sink of G(G') be s(s') and t(t'), respectively. A full-path of G(G') is a path from s(s') to t(t') in G(G'). Then the claim can be re-written as: for any two edges a and b, a full-path which includes both a and b exists either in G or G', and not exists in both G and G'.

It is clear that G and G' are in polar-dual relation. Hence, the edge set of a full-path of G(G') has one to one correspondence with a cut set of G'(G).

If G has a full-path which includes both a and b, there is a cut set in G' which includes both a and b, hence G' does not have a full-path which includes both a and b.

In the following, we consider the case G does not have a full-path which includes both a and b. Let  $V_R$  be the subset of vertices in G consists of the vertices which is reachable from the outgoing vertex of a or the outgoing vertex of b. Let  $V_R$  be the rest. Since G is a directed acyclic graph, the incoming vertex of G and the incoming vertex of G' are both in  $V_R$ . There is no edge from a vertex in  $V_R$  to a vertex in  $V_R$ , hence the set of edges from a vertex in  $V_R$  to a vertex

Property 4 and 5 imply that a rectangular-dissection, as well as a sequence-pair, uniquely corresponds to an HVRS. Then, the correspondence between the sequence-pair and the rectangular-dissection is in question. Next property can be easily derived from the result of Chapter 2.

**Property 6**: For the HVRS T of any rectangular-dissection, there is unique sequence-pair S whose HVRS is T.

The reverse direction is essential to achieve our target. We have the following observations.

**Observation 1**: There is a sequence-pair whose HVRS can only be represented by a rectangular-dissection with an empty room. □

(abcd, bdac) is an example of such sequence-pair whose HVRS can only be represented using an empty room. Fig. 3.1-(a) and Fig. 3.2-(a) illustrate the sequence-pair and the corresponding rectangular-dissection.

**Observation 2**: There is a set of modules whose area minimum placement can only be represented by a rectangular-dissection with an empty room.  $\Box$

For instance, area minimum placement of four modules of sizes  $3 \times 2$ ,  $2 \times 3$ ,  $3 \times 3$  and  $2 \times 4$ , can be represented essentially only by the rectangular-dissection shown in Fig. 3.2-(a). From Observation 1 and 2, it is our constraint that:

Constraint: The HVRS of a sequence-pair should be preserved by the targeted mapping.

**Observation 3**: For an HVRS, rectangular-dissection is not unique if arbitrary many empty rooms are allow to be introduced. □

**Property 7**: For any rectangular-dissection, the number of line segments is equal to the number of rooms plus three.  $\Box$

Property 7 can be proved by counting the number of room corners contributed by a line segment.

Recall that the line segments represent channels. Although the goodness about the number of channels might differ in several routing schemes, fewer number of channels is most likely preferred to avoid too many wire bends. Thus, it is our criterion that:

Criterion: Minimize the number of rooms in the targeted mapping.

#### 3.3 Rectangular-Dissection without Empty Room

This section gives a procedure which maps a sequence-pair to a rectangular-dissection without any empty room if the given sequence-pair satisfies a certain condition. Then, the condition is revealed to be necessary and sufficient for eliminating the introduction of empty room. To describe the condition, we need to define two terms, HV-cross and adjacent-cross.

#### 3.3.1 HV-Cross and Adjacent-Cross

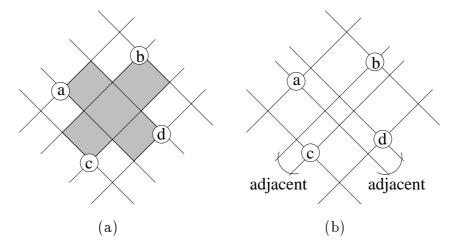

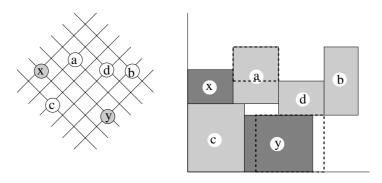

Four modules a, b, c, d are said to form an HV-cross in a sequence-pair  $S = (\Gamma_+, \Gamma_-)$  if they satisfy the following three conditions in  $(\Gamma_+, \Gamma_-)$  or in  $(\Gamma_+, \Gamma'_-)$ , where  $\Gamma'_-$  is the reverse of  $\Gamma_-$ .

- $(\cdots a \cdots b \cdots c \cdots d \cdots, \cdots c \cdots a \cdots d \cdots b \cdots)$

- There is no module x which satisfies

$$(\cdots a \cdots x \cdots d \cdots, \cdots a \cdots x \cdots d \cdots).$$

• There is no module x which satisfies

$$(\cdots b \cdots x \cdots c \cdots, \cdots c \cdots x \cdots b \cdots).$$

Fig. 3.3-(a) illustrates an HV-cross using oblique-grid. There is no module in the dark region because of the last two conditions in the definition. HV-cross is so called because it corresponds to a crossing between an edge in the H-SPG and an edge in the V-SPG in the oblique-grid-embedding of the SPGs.

If four modules a, b, c, d form an HV-cross and b and c are adjacent in  $\Gamma_+$ , and a and d are adjacent in  $\Gamma_-(\Gamma'_-)$ , the HV-cross is also called the *adjacent-cross*. The condition is illustrated in Fig. 3.3-(b).

**Lemma 1**: If there is an HV-cross in a sequence-pair S, then an adjacent-cross also exists in S.

**Proof:** The proof is by contradiction. Without loss of generality, let an HV-cross formed by four modules a, b, c and d be  $S = (\Gamma_+, \Gamma_-) = (\cdots a \cdots b \cdots c \cdots d \cdots c \cdots a \cdots d \cdots b \cdots)$ . (See

Figure 3.3: (a) HV-cross (no module is in the dark region). (b) adjacent-cross (special case of HV-cross).

Fig. 3.4.) We can assume further that: (i) the distance between b and c in  $\Gamma_+$  is minimal over all the HV-crosses in S; and (ii) among such HV-crosses, the distance between a and d in  $\Gamma_-$  is minimal.

If b and c are not adjacent in  $\Gamma_+$ , there is a module in between. Such modules are not between b and c in  $\Gamma_-$ , from the definition of HV-cross. In such modules, there is module x which satisfies one of the two cases:

- $S = (\cdots a \cdots b \cdots x \cdots c \cdots d \cdots, \cdots x \cdots c \cdots a \cdots d \cdots b \cdots)$  and a, b, x, d form an HV-cross, or

- $S = (\cdots a \cdots b \cdots x \cdots c \cdots d \cdots, \cdots c \cdots a \cdots d \cdots b \cdots x \cdots)$  and a, x, c, d form an HV-cross.

(Fig. 3.4 illustrates an example for the former case.) Either case contradicts to the assumption (i). Similarly, if a and d are not adjacent in  $\Gamma_{-}$ , a contradiction to the assumption (ii) is derived. Hence, a, b, c, d form an adjacent-cross.

#### 3.3.2 Converting Sequence-Pair into Rectangular-Dissection

A procedure called SeqPair-RDG is presented to map a sequence-pair to a pair of RDGs. From the resultant RDGs, a rectangular-dissection is obtained by the procedure ConstRD given in Section 3.2. Fig. 3.5 illustrates the result of each step for input sequence-pair S = (abcde, becad). A hyper directed edge is denoted  $(V_i, V_o)$ , where  $V_i$  is the input vertex set, and  $V_o$  is the output vertex set.

#### Procedure SeqPair-RDG

Input: Sequence-pair  $S = (\Gamma_+, \Gamma_-)$  which has no adjacent-cross.

Output: H-RDG  $G_{HP}$  and V-RDG  $G_{VP}$ .

(Step 1) Add four new modules  $s_h, t_h, s_v, t_v$ , called *phantom* modules, to the input sequence-pair  $S = (\Gamma_+, \Gamma_-)$  and obtain new sequence-pair  $S^* = (t_v s_h \Gamma_+ t_h s_v, s_v s_h \Gamma_- t_h t_v)$ . Construct H-SPG  $G_{HSP}$  and V-SPG  $G_{VSP}$  from  $S^*$ .

Figure 3.4: Figure used in the proof of Lemma 1

(Step 2) Construct a horizontal hyper graph  $G_H$  and a vertical hyper graph  $G_V$  from  $G_{HSP}$  and  $G_{VSP}$  as follows. The vertex set of  $G_H$  and  $G_V$  are both equivalent to the vertex set of SPGs. A hyper edge  $(V_L, V_R)$  is in the edge set  $E(G_H)$  if and only if the subgraph of  $G_{HSP}$  induced by  $V_L \cup V_R$  is a maximal bipartite. The edge set  $E(G_V)$  is similarly defined using  $G_{VSP}$ .

(Step 3) For  $G_H$  (also for  $G_V$ ), construct a hyper graph  $G_{HP}$  (resp.  $G_{VP}$ ) by converting all the hyper edges to the vertices and by converting all the vertices, except for the vertices corresponding to the phantom modules, to the edges. (**Procedure SeqPair-RDG End**)

**Theorem 5**: Let S be a sequence-pair of n modules. If S does not include adjacent-cross, procedure SeqPair-RDG maps S to a pair of RDGs which correspond to a rectangular-dissection with no empty room such that the HVRS of the rectangular-dissection equals to the HVRS of S, in  $O(n^2)$  time.

From the resultant RDGs, a rectangular-dissection is obtained by ConstRD in O(n) time. In the following, we prove this theorem.

**Lemma 2**: In (Step 1), each edge of  $G_{HSP}$  ( $G_{VSP}$ ) belongs to a unique maximal complete bipartite subgraph of  $G_{HSP}$  ( $G_{VSP}$ ).

**Proof**: The proof is by contradiction. Assume an edge  $(a_1, b_1)$  belongs to two maximal complete bipartite subgraphs  $G^1(V_i^1 \cup V_o^1, E^1)$  and  $G^2(V_i^2 \cup V_o^2, E^2)$ . Since  $G^1$  and  $G^2$  are both maximal complete bipartite graphs, there are two vertices  $a_2 \in (V_i^1 \cup V_i^2)$  and  $b_2 \in (V_o^1 \cup V_o^2)$  such that there is no edge  $(a_2, b_2)$  in  $E(G_{HSP})$ . The edges  $(a_1, b_1)$ ,  $(a_1, b_2)$  and  $(a_2, b_1)$  all exist in  $E(G_{HSP})$ . If  $a_1$  and  $a_2$  are in horizontal relation, then  $(a_1, b_1)$  or  $(a_2, b_1)$  becomes transitive. Hence  $a_1$  and  $a_2$  are in vertical relation. Without loss of generality, we assume  $a_1$  is above  $a_2$ , i.e.  $S = (\cdots a_1 \cdots a_2 \cdots , \cdots a_2 \cdots a_1 \cdots)$ . Since there are edges  $(a_1, b_1)$  and  $(a_2, b_1)$ ,  $S = (\cdots a_1 \cdots a_2 \cdots b_1 \cdots , \cdots a_2 \cdots a_1 \cdots b_1 \cdots)$ . Considering the fact that there is edge  $(a_1, b_2)$ , the position of  $b_2$  are exhaustively examined in the following. (See Fig. 3.6).

(i)

$$S = (\cdots a_1 \cdots b_2 \cdots a_2 \cdots b_1 \cdots, \cdots a_2 \cdots a_1 \cdots b_1 \cdots b_2 \cdots)$$

(a)  $G_{HSP}$  (solid lines) and  $G_{VSP}$  (dotted lines) obtained in Step 1

(b)  $G_H$  (solid lines) and  $G_V$  (dotted lines) obtained in Step 2

(c)  $G_{HP}$  (solid lines) and  $G_{VP}$  (dotted lines) obtained in Step 3

Figure 3.5: Snapshot of the procedure SeqPair-RDG

Figure 3.6: Figure used in the proof of Lemma 2

In  $G_{VSP}$ , there is a path from  $a_2$  to  $b_2$ . An edge in the path crosses to the edge  $(a_1, b_1) \in E(G_{HSP})$ , thus there is an HV-cross in S. This contradicts to the fact that S has no adjacent-cross (thus no HV-cross by Lemma 1).

(ii)  $S = (\cdots a_1 \cdots a_2 \cdots b_2 \cdots b_1, \cdots a_2 \cdots a_1 \cdots b_1 \cdots b_2 \cdots)$

Since edge  $(a_2, b_2)$  does not exist in  $E(G_{HSP})$ , there is a vertex x which satisfies  $S = (\neg a_1 \neg a_2 \neg x \neg b_2 \neg b_1, \neg a_2 \neg x \neg a_1 \neg b_1 \neg b_2)$  or  $S = (\neg a_1 \neg a_2 \neg x \neg b_2 \neg b_1, \neg a_2 \neg a_1 \neg b_1 \neg x \neg b_2)$ . The former case results in  $(a_2, b_1)$  being transitive, and the latter results in  $(a_1, b_2)$  being transitive, either contradicts to the definition of  $G_{HSP}$ .

(iii)  $S = (\cdots a_1 \cdots a_2 \cdots b_1 \cdots b_2 \cdots, \cdots a_2 \cdots a_1 \cdots b_2 \cdots b_1 \cdots)$

Since there is no edge  $(a_2, b_2)$ , there is module x which satisfies  $S = (\cdots b_1 \cdots x \cdots b_2 \cdots a_2 \cdots x \cdots a_1)$ . Then, there is a path from x to  $a_1$  in  $G_{VSP}$ . An edge in the path crosses to the edge  $(a_2, b_1) \in E(G_{HSP})$ , which is a contradiction.

(iv) The other cases are trivially impossible.

Hence, an edge in  $G_{HSP}$  belongs to a unique maximal bipartite subgraph of  $G_{HSP}$ . Similarly, the claim also holds for  $G_{VSP}$ .

**Lemma 3**: The pair of graphs  $G_{HP}$  and  $G_{VP}$  obtained by SeqPair-RDG is the RDGs. **Proof**: In the following, we show the output is a pair of RDGs by converting the oblique-grid-embedding of  $S^*$ . The modules in S are called *real* modules in contrast to the phantom modules.

In the oblique-grid embedding of  $S^*$  which is obtained in (Step 1), any horizontal edge and vertical edge do not cross each other because  $S^*$  does not have HV-cross. (A cross between horizontal edges, or between vertical edges, is possible.)

In the HVRS of  $S^*$ , phantom module  $s_h$  ( $t_h$ ,  $s_v$ ,  $t_v$ ) is left of (right of, below, above, respectively) every real module. Hence all the vertices corresponding to real modules have at least one input edge and one output edge, both in  $G_{HSP}$  and in  $G_{VSP}$ .

In the hyper directed graphs  $G_H$  and  $G_V$  obtained in (Step 2), the input degree and the output degree of each vertex are 0 or 1. From Lemma 2, the input degree and the output degree of the vertices which correspond to real modules are both 1, in either hyper graph. Further, any two edges do not cross each other if they are taken from distinct maximal complete bipartite subgraphs. Hence,  $G_H$  and  $G_V$  can be drawn without any crossing, as shown in Fig. 3.5-(b).

In (Step 3), the conversion between hyper edges and vertices preserves the planarity, thus  $G_{HP}$  and  $G_{VP}$  are planar. The input degree and the output degree of  $G_{HP}$  and  $G_{VP}$  are 1. Hence, the two hyper graphs  $G_{HP}$  and  $G_{VP}$  are both ordinary graphs. Consequently,  $G_{HP}$  and  $G_{VP}$  are in polar-dual relation. From Property 2, they are RDGs.

**Lemma 4**: The HVRS of the RDGs obtained by SeqPair-RDG is equivalent to the HVRS of the input sequence-pair.

**Proof:** In (Step 1), a horizontal (vertical) relation is represented as a path between two vertices in  $G_{HSP}$  ( $G_{VSP}$ ). For each path in  $G_{HSP}$  ( $G_{VSP}$ ), the corresponding path exists in the hyper graph  $G_H$  ( $G_V$ ) in (Step 2), and also in the in  $G_{HP}$  ( $G_{VP}$ ) in (Step 3). No new relation is introduced in the resultant RDGs since the RDGs can not represent both horizontal and vertical relation for a module pair (Property 5).

#### (Proof of Theorem 5)

Only the speed is proved in the following since the other claims are already proved by Lemma 3 and 4.

In (Step 1), SPGs are constructed faithfully to the HVRS, but eliminating the transitive edges, by its definition. For a module a, the set of all the modules  $\{x_1, x_2, \ldots, x_m\}$  that are non-transitively right of module a can be computed in O(n) time using the fact that they are in the form:

$$(\cdots x_m \cdots x_2 \cdots x_1 \cdots, \cdots a \cdots x_1 \cdots x_2 \cdots x_m).$$

Hence, SPGs can be constructed in  $O(n^2)$  time.

(Step 2) can be done also in  $O(n^2)$  time, proportional to the number of edges in SPGs, because each edge in SPGs belongs to a unique maximal bipartite in SPGs (Lemma 2).

It is obvious that the sum of the cardinality of the input vertex set and that of the output vertex set of all the hyper edges in  $G_H$  ( $G_V$ ) is O(n). Hence, (Step 3) can be done in O(n) time.

Consequently, SeqPair-RDG can be done in  $O(n^2)$  time.

#### 3.3.3 Necessary and Sufficient Condition

Theorem 5 shows that the absence of the adjacent-cross is sufficient for a sequence-pair to be mapped to a rectangular-dissection without empty room. It is also necessary as follows.

**Theorem 6**: A sequence-pair can be mapped to a rectangular-dissection without introducing any empty room if and only if the sequence-pair does not have an adjacent-cross.

**Proof:** The condition is sufficient by Theorem 5. Let S be a sequence-pair of n modules and S includes one or more adjacent-crosses. In the following, we show the HVRS of S is not equivalent to the HVRS of any rectangular-dissection with n rooms.

Let four modules a, b, c, d form an adjacent-cross in S. Without loss of generality, Let  $S = (\cdots a \cdots bc \cdots d \cdots, \cdots b \cdots da \cdots c \cdots)$ . The proof is by contradiction. Assume the relative module position of S is represented by a rectangular-dissection F without any empty room.

In the H-RDG of F, there are three paths;

- (i) the path from the edge a to the edge c,

- (ii) the path from the edge b to the edge c, and

- (iii) the path from the edge b to the edge d.

For the path (ii), from the two facts "b and c are adjacent in  $\Gamma_+$ , and there is no anonymous edge in the H-RDG of F.", it is understood that edge b and edge c are directly connected by a vertex v. It implies that the vertex v is in the path (i) and also in the path (iii). Hence, there is a path from a to d (via v) in the H-RDG. This contradicts to the fact: a and d are in the vertical relation in the HVRS of S, thus not in the horizontal relation.

## 3.4 Rectangular-Dissection with Fewest Empty Rooms

In this section, we give a procedure which maps a sequence-pair to a rectangular-dissection with fewest empty rooms. The maximum possible number of empty rooms is also presented.

#### 3.4.1 Removing Adjacent-Crosses

Let  $S = (\Gamma_+, \Gamma_-)$  be a sequence-pair of n modules, which possibly includes adjacent-crosses. Inserting dummy module x into S is to add a new module x into  $\Gamma_+$  and into  $\Gamma_-$ . "Adjacent-cross ab/cd" denotes an adjacent-cross such that a and b are adjacent in  $\Gamma_+$  and c and d are adjacent in  $\Gamma_-$ . For example,  $(\cdots d \cdots ab \cdots c \cdots, \cdots a \cdots cd \cdots b \cdots)$  and  $(\cdots c \cdots ab \cdots d \cdots, \cdots b \cdots cd \cdots a \cdots)$  are such cases.