## **JAIST Repository**

https://dspace.jaist.ac.jp/

| Title        | Hierarchical Interconnection Networks for<br>Massively Parallel Computers |  |  |

|--------------|---------------------------------------------------------------------------|--|--|

| Author(s)    | M., M., Hafizur Rahman                                                    |  |  |

| Citation     |                                                                           |  |  |

| Issue Date   | 2006-03                                                                   |  |  |

| Туре         | Thesis or Dissertation                                                    |  |  |

| Text version | author                                                                    |  |  |

| URL          | http://hdl.handle.net/10119/981                                           |  |  |

| Rights       |                                                                           |  |  |

| Description  | Supervisor:日比野 靖,情報科学研究科,博士                                               |  |  |

# Hierarchical Interconnection Networks for Massively Parallel Computers

by

### M.M. Hafizur Rahman

submitted to

Japan Advanced Institute of Science and Technology

in partial fulfillment of the requirements

for the degree of

Doctor of Philosophy

Supervisor: Professor Susumu Horiguchi

School of Information Science Japan Advanced Institute of Science and Technology ©Copyright 2006 by M.M. Hafizur Rahman All Rights Reserved

## Abstract

The most critical component in determining the ultimate performance potential of a multicomputer is its interconnection network. In this dissertation, we propose a new hierarchical interconnection network, called the Hierarchical Torus Network (HTN) for large scale 3D multicomputers. It consists of multiple basic modules (BMs) which are 3D-tori  $(m \times m \times m)$  and are hierarchically interconnected by 2D-tori  $(n \times n)$ . Both the BMs and the interconnection at higher levels are toroidally connected, hence the name Hierarchical Torus Network (HTN). To reduce the vertical links between silicon planes, we consider higher-level networks as 2D-torus instead of 3D-torus network. We have explored various aspects such as network diameter, cost, average distance, bisection width, peak number of vertical links, and VLSI layout area of the HTN and compared them with those for other networks. It is shown that the HTN possesses several attractive features including constant node degree, small diameter, small average distance, high arcconnectivity, better bisection width, small number of wires, a particularly small number of vertical links, and an economic layout area.

We have used wormhole routing for switching because it has low buffering requirements, and more importantly, it makes latency independent of the message distance. Deadlock-free routing is the most critical issue in wormhole-routed networks and is achieved by using virtual channels (VCs). Since the hardware cost increases as the number of VCs increases, the unconstrained use of VCs is cost-prohibitive. In this dissertation, we present a deadlock-free routing algorithm for the HTN with a minimum number of VCs. By using the dimension-order routing and various traffic patterns, we have evaluated the dynamic communication performance of the HTN as well as other networks. HTN yields low latency and high throughput, which are indispensable for high performance massively parallel computers. It is also shown that the impact of non-uniform traffic patterns on the HTN is less than on the other networks. We have also described a suite of low-cost adaptive routers, LS, CS, and LS+CS with dimension order routing, analyzed their cost, and evaluated the dynamic communication performance for the HTN. The hardware cost for the LS, CS, and LS+CS algorithms is exactly equal to dimension order routing. The only overhead imposed is router delay for header selection. The dynamic communication performance using LS+CS algorithm is better than when the other algorithms are used. Therefore, an HTN with the LS+CS algorithm is a good choice for future massively parallel computers.

A fault tolerant network is very essential for the reliability of massively parallel computer systems. We have presented a hierarchical redundancy approach to reconfigure a faulty node by redundant node for the HTN. With a 25% redundancy, the system yield at the BM and second level are satisfactory. To show the suitability of the HTN, we have discussed mapping of some commonly used advanced applications. It is shown that the number of communication steps for applications mapping on the HTN is lower than for conventional and other hierarchical interconnection networks.

Pruning technique reduces the wiring complexity. We have explored the 3D-WSI implementation aspect of pruned-HTN. It is shown that the peak number of vertical links and layout area of pruned HTN in 3D-WSI is less than that of non-pruned HTN. To show the versatility of torus-torus combination for hierarchical networks, we have modified two other hierarchical networks (H3D-torus and TESH) using torus-torus networks.

To Taha never dull never boring always beloved

## Acknowledgments

First of all, I would like to thank the almighty Allah (SWT) who has again blessed me to pass another important passage in my life.

I wish to express my sincere and profound gratitude and profuse thanks to my supervisor Prof. Susumu Horiguchi of GSIS at Tohoku university for his constant encouragement and kind guidance during this research work. I am deeply grateful to him for his enthusiasm and insight, which have made research a most enjoyable and fulfilling experience. His phenomenal depth of knowledge and ability to discern the key points of the research problem inspire me a lot. I am deeply indebted to him for his patient supervision and warm support. I am both incredibly proud and immensely lucky to become one of his students.

I wish to continue my gratitude to Prof. Y. Hibino, Prof. M. Kaneko, Prof. T. Matsuzawa, and Prof. Y. Inoguchi for gladly agreeing to serve as members of my dissertation committee and for providing helpful advice.

I am highly obliged to Prof. Yasushi Inoguchi of School of Information Science at JAIST for his kindness, and valuable suggestion and discussion during the research of sub-theme. I would like to take this opportunity to thank all the teaching staff at the school of Information Science at JAIST, who has benefited me with a worth of knowledge. I would also like to thank Asso. Prof. X. Jiang and Research Associate Masaru Fukushi of Tohoku university and Ryoko Hayashi of Kanazawa Institute of Technology for their helpful discussion, comments, and suggestions during this research work. In particular, Mr. Fukushi has given me a lot of helpful advice to reach the valuable insights in wafer stacked-implementation of massively parallel computers. I would like to continue my sincere thanks to Dr. Yasuyuki Miura of Communication Research Laboratory, Tokyo for his kind help.

I am indebted to the to the Ministry of Education, Science, Sports, and Culture, Japan for the financial support I have been provided with for staying and studying here at JAIST. I would like to continue thanks the japanese language teachers, especially Etsuko Horiguchi sensei who teach me Japanese language. Without them, I would certainly have run into much trouble. It is my great pleasure to do research work with the members of firmware laboratory. I devote my sincere thanks and appreciation to my lab-mates. I can not express how much I have appreciated and their support and friendship through the years. I will keep them in my mind for their help and assistance.

Although far away from Bangladesh, I would also like to say thanks to my parents, who encouraged me to succeed by teaching me not to fear failure. Last, but not least, I can never hope to thank, my dear Ruba and our sweet son Taha, enough for their continuous support and encouragement. They were putting up with many dreary evenings and weekends when I was doing this research work. Their tolerance an understanding made it possible for me to complete this endeavor.

# Contents

| $\mathbf{A}$ | Abstract |         | ii                                                      |    |

|--------------|----------|---------|---------------------------------------------------------|----|

| $\mathbf{A}$ | ckno     | wledgn  | nents                                                   | iv |

| 1            | Intr     | oducti  | ion                                                     | 1  |

|              | 1.1      | Introd  | luction                                                 | 1  |

|              | 1.2      |         | onnection Networks                                      | 2  |

|              | 1.3      |         | ations and Goal                                         | 6  |

|              | 1.4      |         | ibution of the Dissertation                             | 8  |

|              | 1.5      |         | sis of the Dissertation                                 | 10 |

| 2            | Inte     | erconne | ection Networks for Massively Parallel Computers        | 12 |

|              | 2.1      | Introd  | luction                                                 | 12 |

|              | 2.2      | Defini  | tions                                                   | 14 |

|              |          | 2.2.1   | Fundamental Definitions                                 | 14 |

|              |          | 2.2.2   | Topological Characteristics of Interconnection Networks | 14 |

|              |          | 2.2.3   | Layout Characteristics of Interconnection Networks      | 15 |

|              |          | 2.2.4   | Dynamic Communication Performance Metrices              | 15 |

|              | 2.3      | Interce | onnection Network Topologies                            | 16 |

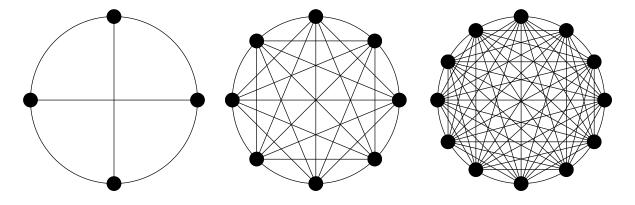

|              |          | 2.3.1   | Completely-Connected Networks                           | 16 |

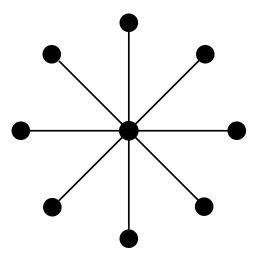

|              |          | 2.3.2   | Star Networks                                           | 16 |

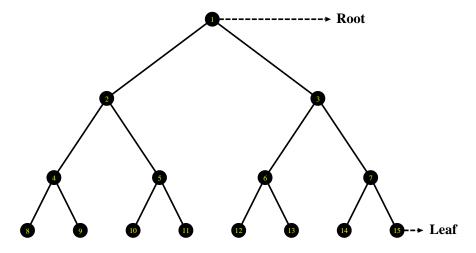

|              |          | 2.3.3   | Tree Networks                                           | 17 |

|              |          | 2.3.4   | Hypercubic Networks                                     | 19 |

|              |          | 2.3.5   | Array Networks                                          | 22 |

|              | 2.4      | Hierar  | chical Interconnection Network (HIN)                    | 26 |

|              |          | 2.4.1   | Completely-Connected Network based HIN                  | 27 |

|              |          | 2.4.2   | Tree Network based HIN                                  | 29 |

|              |          | 2.4.3   | Hypercube Network based HIN                             | 31 |

|              |          | 2.4.4   | Array Network based HIN                                 | 33 |

|              | 2.5      | Conclu  | usions                                                  | 38 |

| 3            | Hie      | rarchic | cal Torus Network (HTN)                                 | 39 |

|              | 3.1      |         | luction                                                 | 39 |

|              | 3.2      | Archit  | secture of the HTN                                      | 40 |

|              |          | 3.2.1   | Basic Module                                            | 40 |

|              |          | 322     | Higher Level Interconnection                            | 41 |

|   |     | 3.2.3 Addressing and Routing                                 |

|---|-----|--------------------------------------------------------------|

|   | 3.3 | Static Network Performance                                   |

|   |     | 3.3.1 Node Degree                                            |

|   |     | 3.3.2 Diameter                                               |

|   |     | 3.3.3 Average Distance                                       |

|   |     | 3.3.4 Cost                                                   |

|   |     | 3.3.5 Connectivity                                           |

|   |     | 3.3.6 Bisection Width                                        |

|   | 3.4 | Wafer Stacked Implementation                                 |

|   |     | 3.4.1 3D Stacked Implementation                              |

|   |     | 3.4.2 Peak Number of Vertical Links                          |

|   |     | 3.4.3 Layout Area                                            |

|   |     | 3.4.4 Maximum Wire Length                                    |

|   | 3.5 | Conclusions                                                  |

|   |     |                                                              |

| 4 | -   | namic Communication Performance of the HTN 67                |

|   | 4.1 | Introduction                                                 |

|   | 4.2 | Routing Algorithm                                            |

|   |     | 4.2.1 Resources and Allocation Units                         |

|   |     | 4.2.2 Taxonomy of Routing Algorithm                          |

|   |     | 4.2.3 Primitive Considerations                               |

|   |     | 4.2.4 Channel Dependency Graph                               |

|   | 4.3 | Dimension-Order Routing (DOR) for HTN                        |

|   |     | 4.3.1 Routing Algorithm for HTN                              |

|   |     | 4.3.2 Deadlock-free Routing                                  |

|   |     | 4.3.3 Minimum Number of Virtual Channels                     |

|   | 4.4 | Dynamic Communication Performance using DOR                  |

|   |     | 4.4.1 Performance of Interconnection Networks                |

|   |     | 4.4.2 Simulation Environment                                 |

|   |     | 4.4.3 Traffic Patterns                                       |

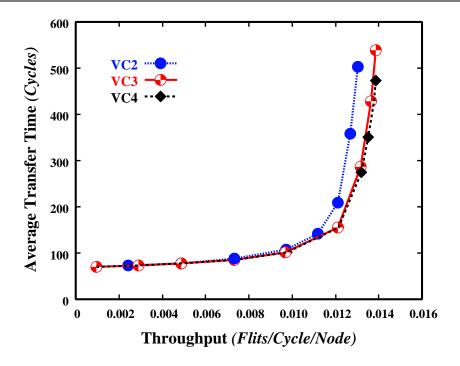

|   |     | 4.4.4 Dynamic Communication Performance Evaluation           |

|   |     | 4.4.5 Effect of Message Length                               |

|   |     | 4.4.6 Effect of the Number of Virtual Channels               |

|   | 4.5 | Adaptive Routing                                             |

|   |     | 4.5.1 Link-Selection (LS) Algorithm                          |

|   |     | 4.5.2 Channel-Selection (CS) Algorithm                       |

|   |     | 4.5.3 Combination of LS and CS (LS+CS) Algorithm             |

|   |     | 4.5.4 Deadlock-Free Routing                                  |

|   | 4.6 | Router Cost and Speed                                        |

|   |     | 4.6.1 Router Gate Counts                                     |

|   |     | 4.6.2 Router Speed                                           |

|   | 4.7 | Dynamic Communication Performance using Adaptive Routing 125 |

|   | 4.8 | Conclusions                                                  |

| 5 | Rec          | configuration Artchitecture and Application Mappings               | 132 |

|---|--------------|--------------------------------------------------------------------|-----|

|   | 5.1          | Introduction                                                       | 132 |

|   | 5.2          | Reconfiguration Architecture of the HTN                            | 133 |

|   |              | 5.2.1 Reconfiguration Scheme                                       | 133 |

|   |              | 5.2.2 System Yield of the HTN                                      |     |

|   | 5.3          | Application Mappings on HTN                                        | 139 |

|   |              | 5.3.1 Converge and Diverge                                         |     |

|   |              | 5.3.2 Bitonic Merge                                                |     |

|   |              | 5.3.3 Fast Fourier Transform (FFT)                                 |     |

|   |              | 5.3.4 Finding the Maximum                                          |     |

|   |              | 5.3.5 Processing Time                                              |     |

|   | 5.4          | Conclusions                                                        |     |

| 0 | ъ            | litt. l. lab Ni / l                                                | 150 |

| 6 | Pru<br>6.1   | ned Hierarchical Torus Network Introduction                        | 150 |

|   | 6.2          | Pruned Network                                                     |     |

|   | 0.2          | 6.2.1 Pruned Torus Network                                         |     |

|   |              |                                                                    |     |

|   | c o          | 6.2.2 Pruned HTN                                                   |     |

|   | 6.3          | 3D-WSI Implementation of the Pruned HTN                            |     |

|   |              | 6.3.1 Peak Number of Vertical Links                                |     |

|   | 0.4          | 6.3.2 Layout Area                                                  |     |

|   | 6.4          | Conclusion                                                         | 159 |

| 7 | Mo           | dification of other Hierarchical Networks based on Torus-Torus In- | -   |

|   | tero         |                                                                    | 160 |

|   | 7.1          | Introduction                                                       |     |

|   | 7.2          | Modified Hierarchical 3D-Torus Network                             | 160 |

|   |              | 7.2.1 Interconnection of the MH3DT Network                         | 161 |

|   |              | 7.2.2 Routing Algorithm                                            | 163 |

|   |              | 7.2.3 Deadlock-Free Routing                                        | 165 |

|   |              | 7.2.4 Static Network Performance                                   | 166 |

|   |              | 7.2.5 Dynamic Communication Performance                            | 168 |

|   |              | 7.2.6 Summary                                                      | 172 |

|   | 7.3          | Modified TESH Network                                              |     |

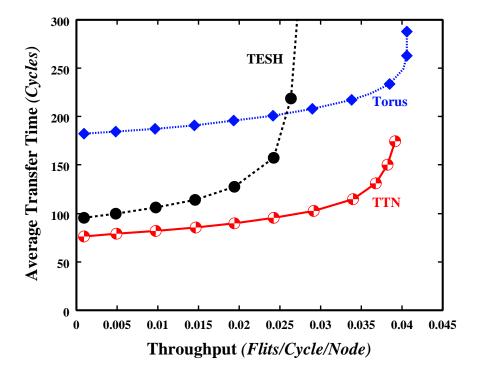

|   |              | 7.3.1 Interconnection of the TTN                                   |     |

|   |              | 7.3.2 Routing Algorithm                                            |     |

|   |              | 7.3.3 Deadlock-Free Routing                                        |     |

|   |              | 7.3.4 Static Network Performance                                   |     |

|   |              | 7.3.5 Dynamic Communication Performance                            |     |

|   |              | 7.3.6 Summary                                                      |     |

|   | 7.4          | Conclusion                                                         |     |

| 0 | $\mathbf{C}$ | -1                                                                 | 104 |

| 8 |              | nclusions                                                          | 184 |

|   | 8.1          | Introduction                                                       |     |

|   | 8.2          | Conclusions                                                        | 184 |

|   | 0.0          | Future Directions                                                  | 188 |

| References   | 190 |

|--------------|-----|

| Publications | 202 |

| Index        | 204 |

# List of Figures

| 2.1  | Completely-connected networks for $N = 4$ , $N = 8$ , and $N = 12$         | 16 |

|------|----------------------------------------------------------------------------|----|

| 2.2  | A star-connected network of nine nodes                                     | 17 |

| 2.3  | Star graph network                                                         | 18 |

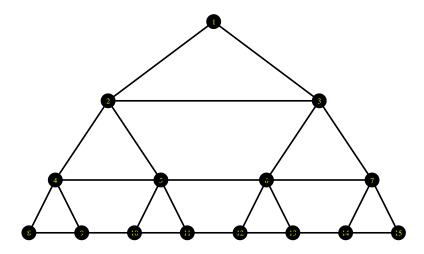

| 2.4  | A 15 node binary tree network                                              | 19 |

| 2.5  | A 15 node X-tree network                                                   | 19 |

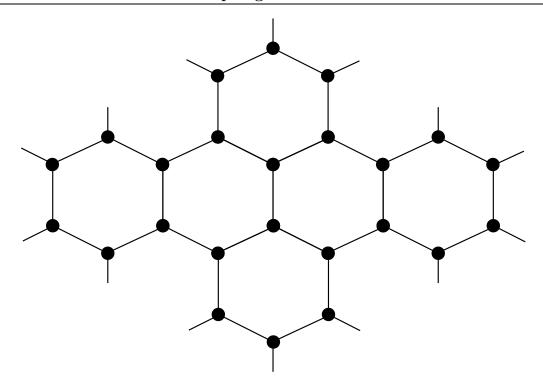

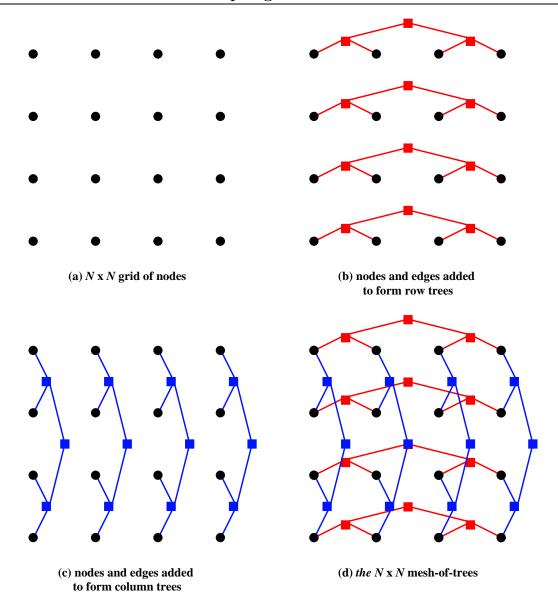

| 2.6  | The 2D mesh-of-trees. Leaf nodes from the original grid are denoted with   |    |

|      | black circles. Nodes added to form row trees are denoted with red squares, |    |

|      | and nodes added to form column trees are denoted with blue squares         | 20 |

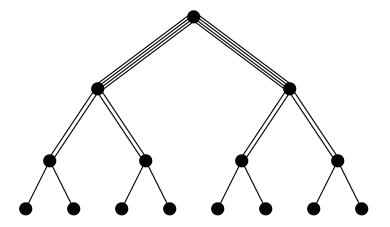

| 2.7  | A fat-tree network                                                         | 20 |

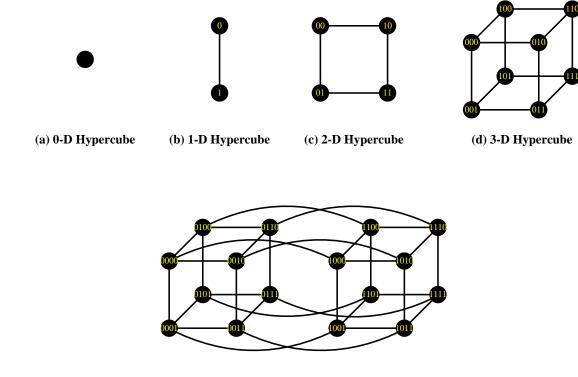

| 2.8  | The Binary cube networks of zero, one, two, three, and four dimensions,    |    |

|      | the nodes are labeled using $n$ -bit binary numbers                        | 22 |

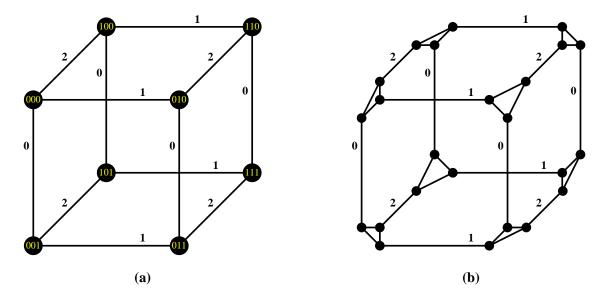

| 2.9  | (a) The 3-dimensional binary cube network (b) The 3-dimensional CCC.       |    |

|      | Labels for individual nodes in the CCC are binary cube node label and the  |    |

|      | adjacent link label                                                        | 23 |

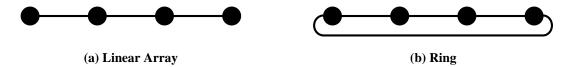

| 2.10 | A four-node linear array and ring network                                  | 24 |

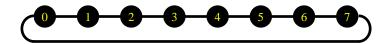

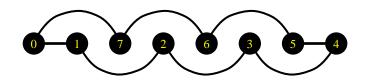

| 2.11 | A layout for a ring network which minimizes link lengths $(N = 8)$         | 24 |

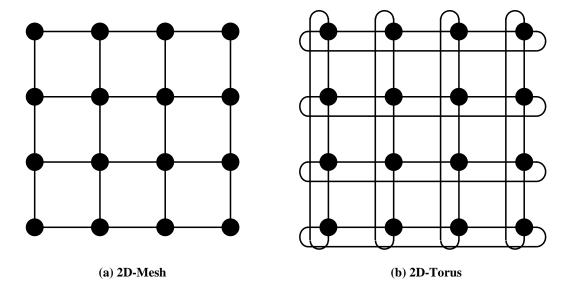

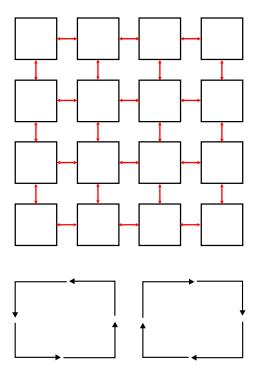

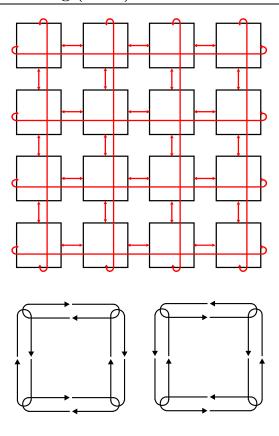

|      | 2D mesh and torus networks with 4 nodes in each dimension (a) 2D-mesh      |    |

|      | (b) 2D-torus networks                                                      | 25 |

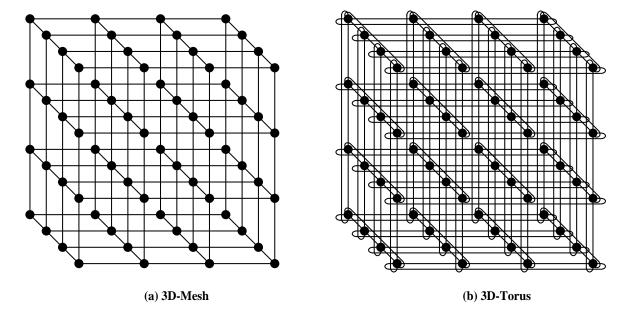

| 2.13 | 3D mesh and torus networks with 4 nodes in each dimension (a) 3D-mesh      |    |

|      | and (b) 3D-torus networks                                                  | 26 |

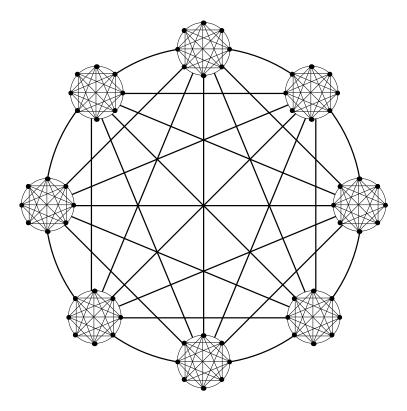

| 2.14 | A level-2 MFC network with 8 clusters and the cluster size is 8            | 28 |

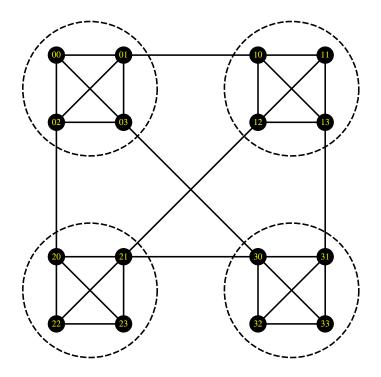

| 2.15 | An example of 16-node swapped network with the 4-node complete graph       |    |

|      | as its basis.                                                              | 28 |

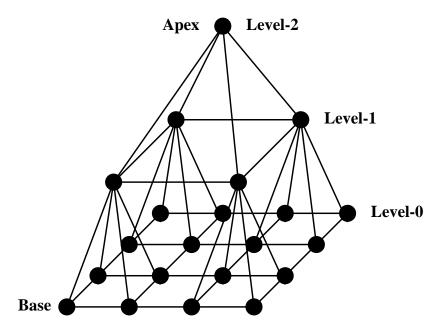

| 2.16 | A pyramid network of 16 node                                               | 29 |

| 2.17 | A hierarchical clique network                                              | 30 |

| 2.18 | Fibonacci cubes                                                            | 31 |

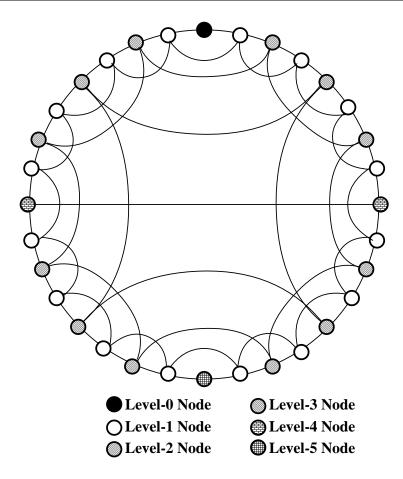

| 2.19 | A HCN(2,2) network                                                         | 32 |

| 2.20 | Recursive diagonal torus network                                           | 33 |

| 2.21 | Standard 1D-SRT consisting of 32 nodes                                     | 34 |

| 2.22 | Level-2 interconnection of TESH network                                    | 35 |

| 2.23 | Interconnection of a Level-2 H3D-torus network                             | 36 |

| 2.24 | Interconnection of a Level-2 H3D-mesh network                              | 37 |

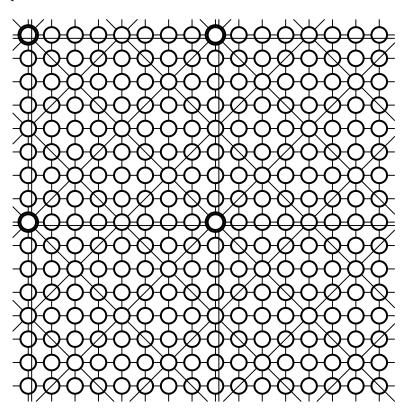

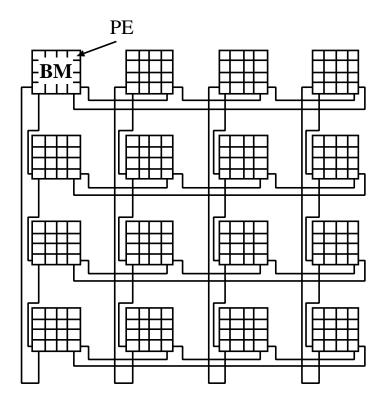

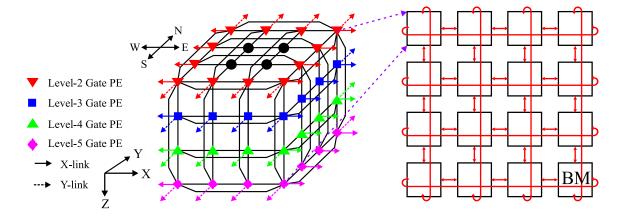

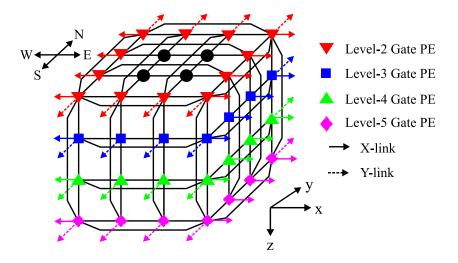

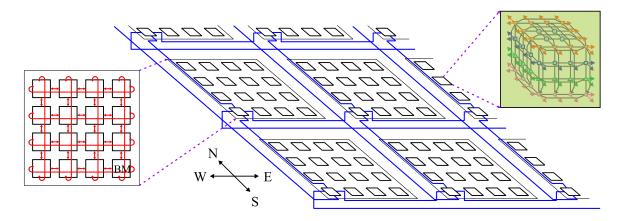

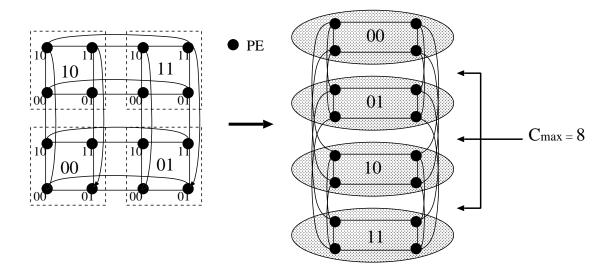

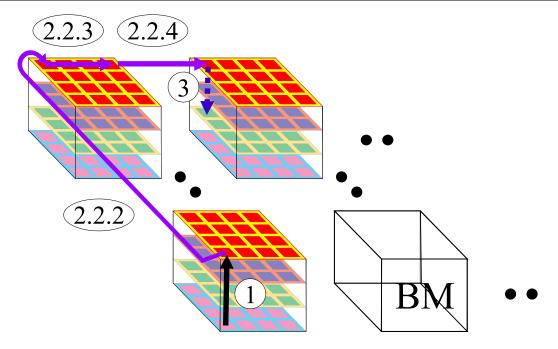

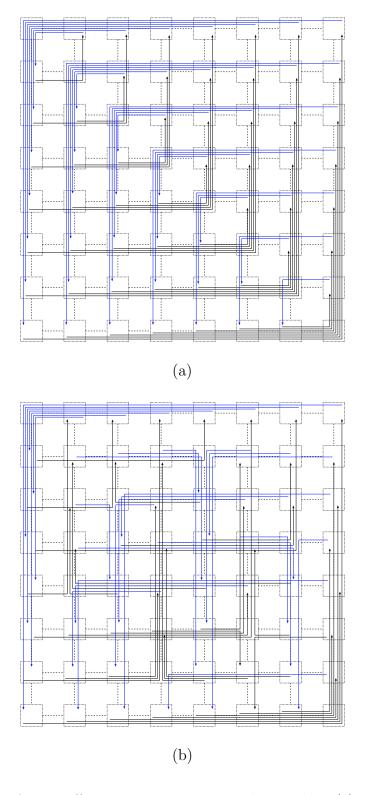

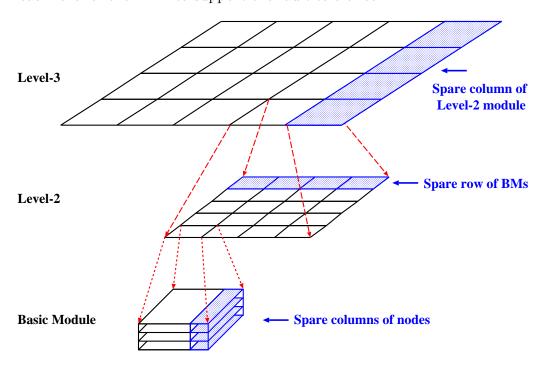

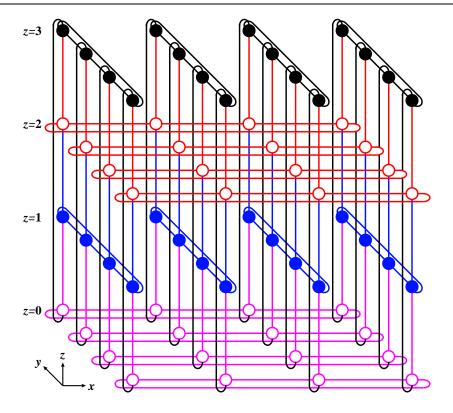

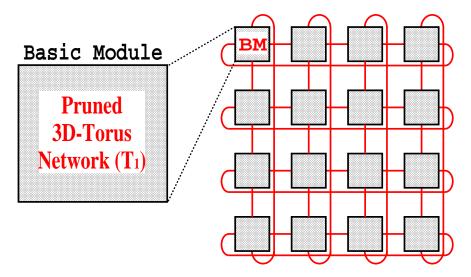

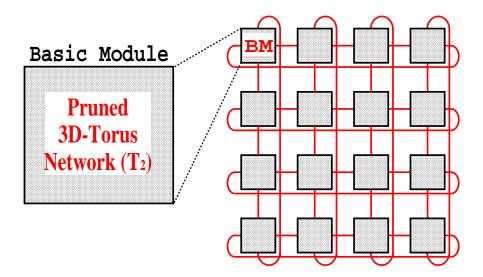

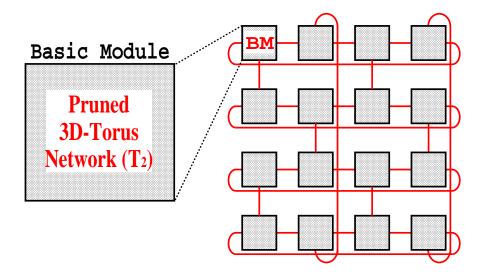

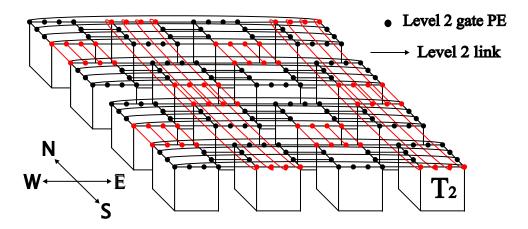

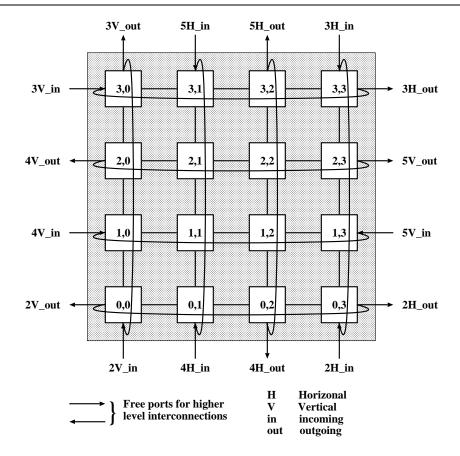

| 3.1  | Interconnection of HTN                                                     | 40 |

| 3.2  | Basic module of the HTN                                                    | 41 |

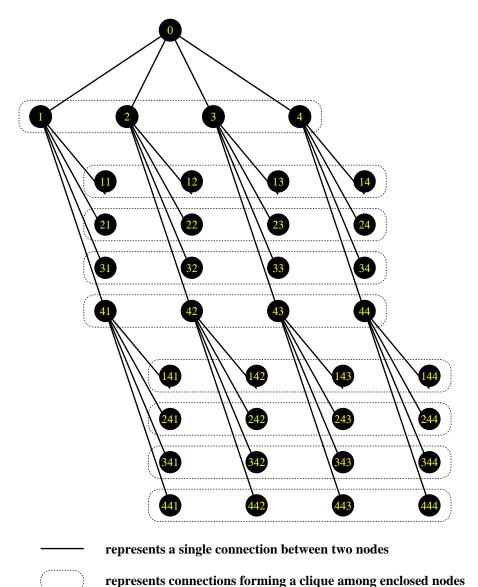

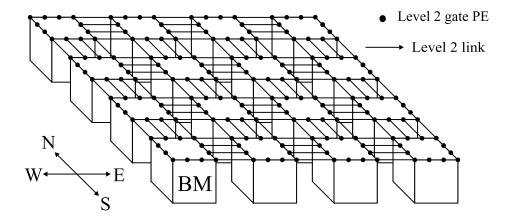

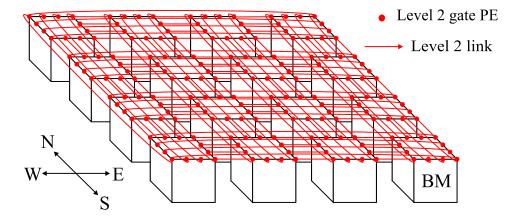

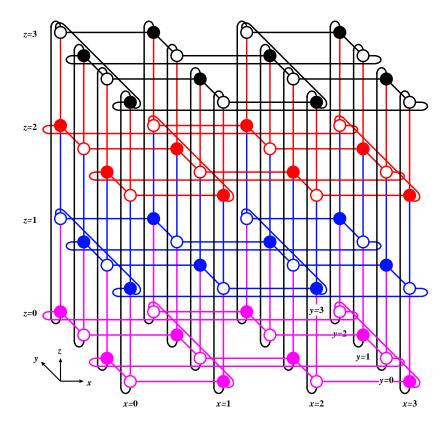

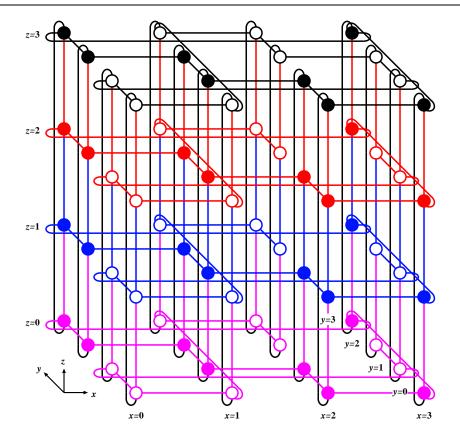

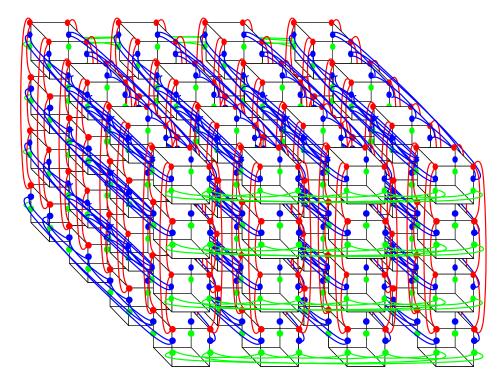

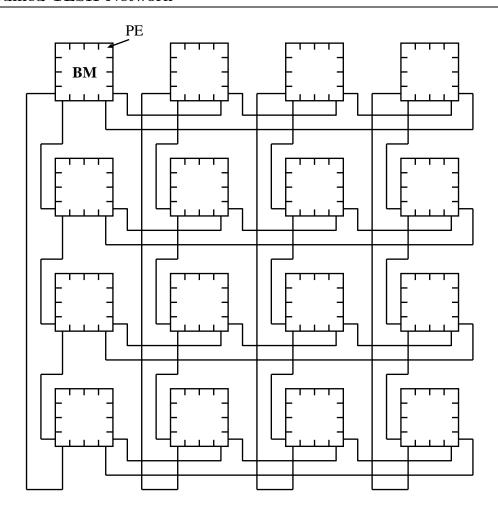

| 3.3  | Interconnection of a Level-2 HTN                                           | 42 |

| 3.4  | Interconnection of a Level-3 HTN                                           | 42 |

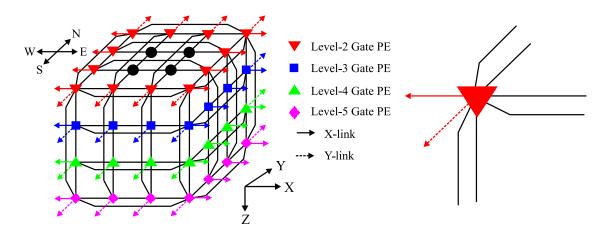

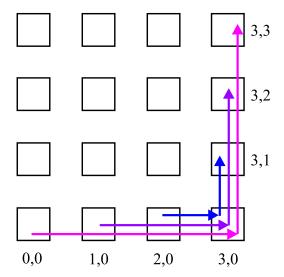

| 3.5  | Routing algorithm of the HTN                                               | 45 |

| 3.6    | Illustration of degree of HTN                                                 | 46  |

|--------|-------------------------------------------------------------------------------|-----|

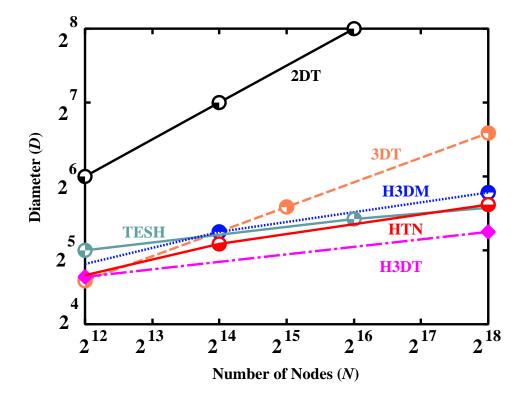

| 3.7    | Diameter of networks as a function of number of nodes $(N)$                   | 48  |

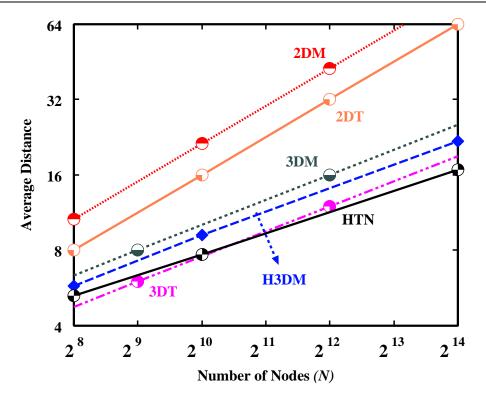

| 3.8    | Average distance of networks as a function of number of nodes (N)             | 50  |

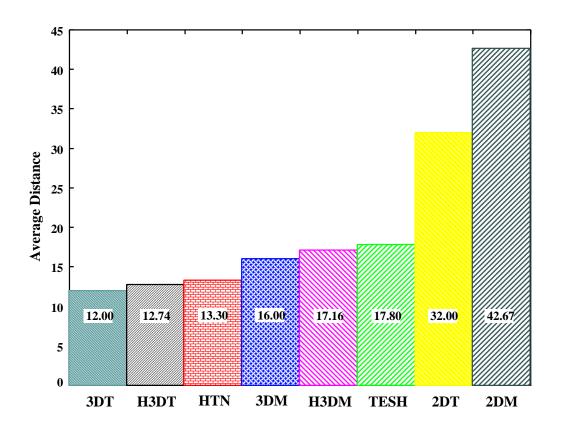

| 3.9    | Average distance of various networks with 4096 nodes                          | 50  |

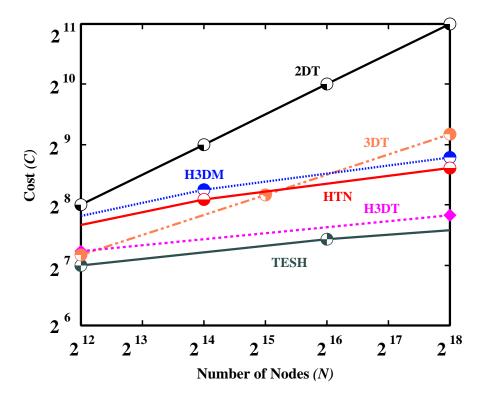

| 3.10   | Cost of different networks as a function of number of nodes $(N)$             | 51  |

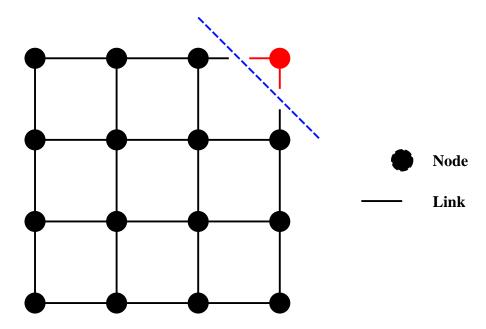

| 3.11   | Illustration of connectivity for 2D-mesh network                              | 52  |

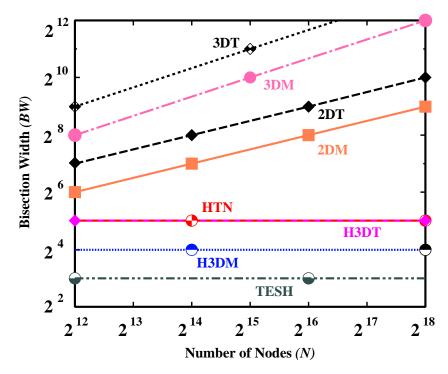

|        | Bisection width of networks as a function of number of nodes $(N)$            | 53  |

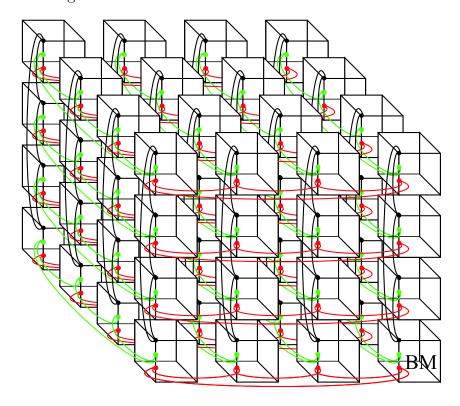

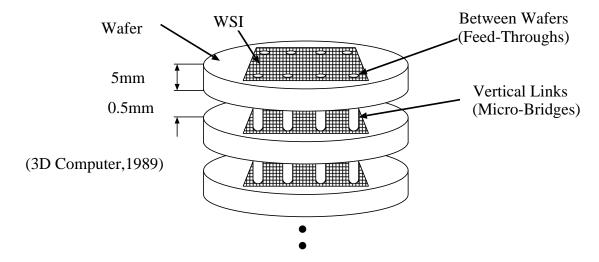

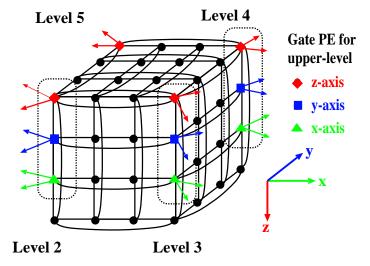

| 3.13   | Structure of 3D stacked implementation                                        | 55  |

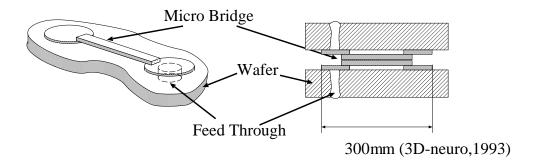

| 3.14   | Structure of microbridge and feedthrough                                      | 55  |

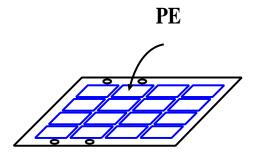

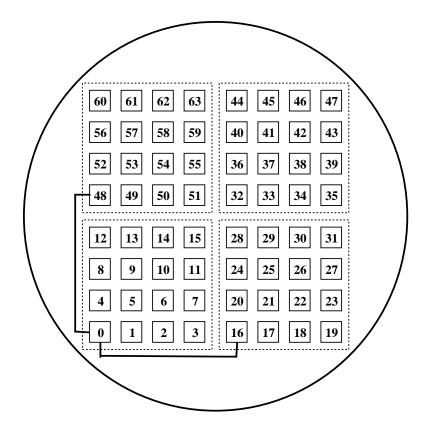

|        | PE array in a silicon plane for wafer stacked-implementation                  | 56  |

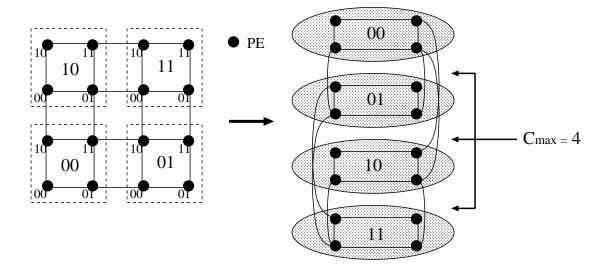

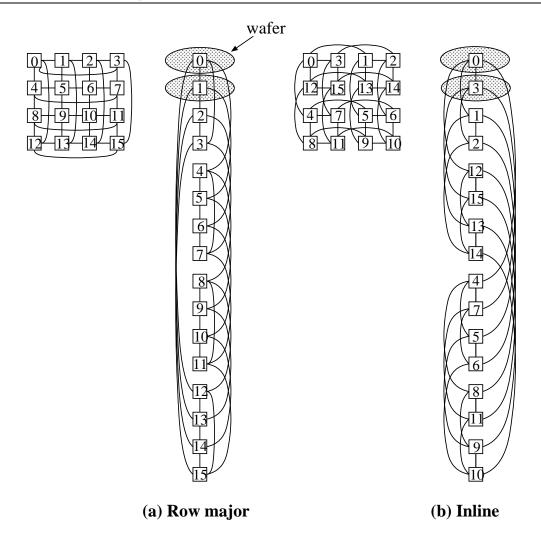

| 3.16   | Vertical links of 2D-mesh network in 3D wafer stacked-implementation          | 56  |

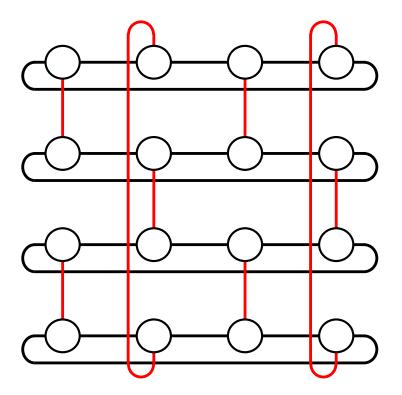

| 3.17   | Vertical links of 2D-torus network in 3D wafer stacked-implementation         | 56  |

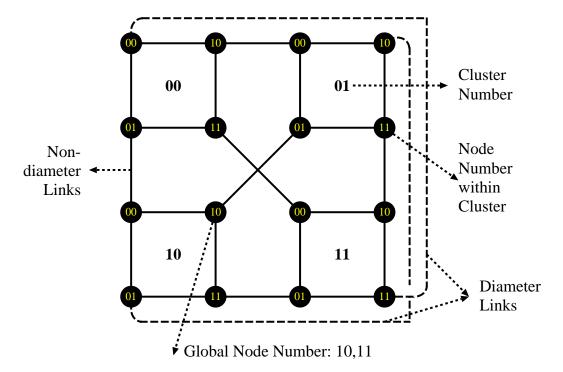

| 3.18   | Interconnection scheme of 2D-torus in 3D stacked implementation               | 57  |

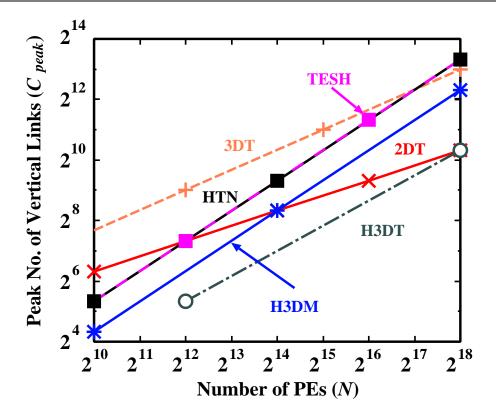

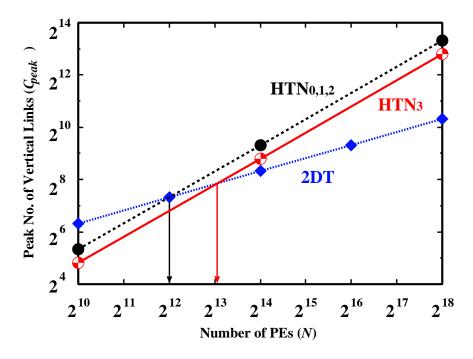

| 3.19   | A comparison of peak number of vertical links of HTN with other networks      | 59  |

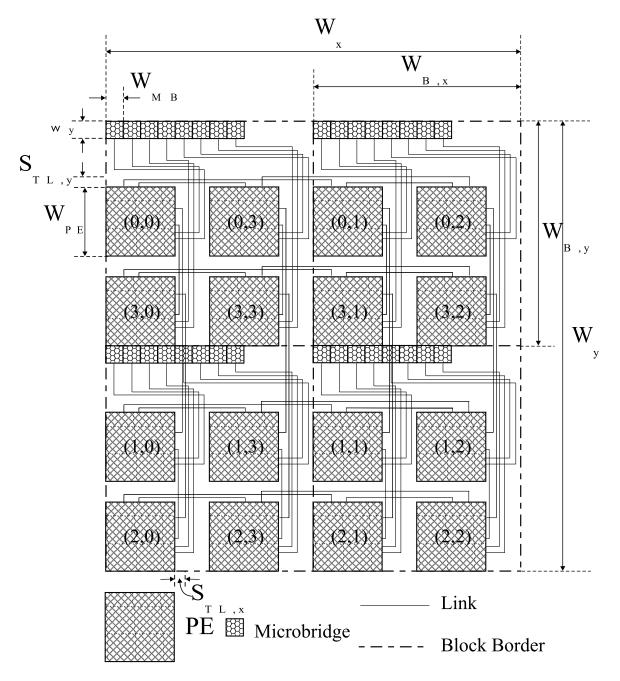

| 3.20   | Layout area of 2D-torus for $N = 16$ , $L = 4$ and $p = 1$                    | 61  |

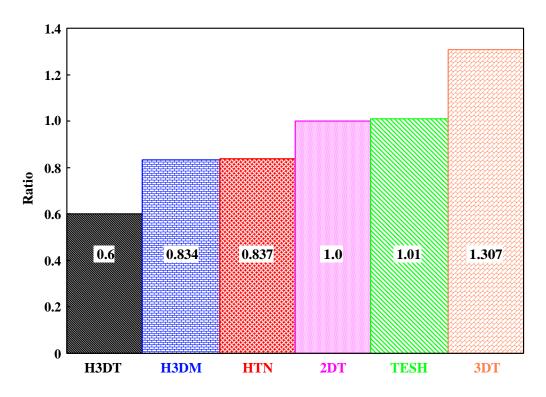

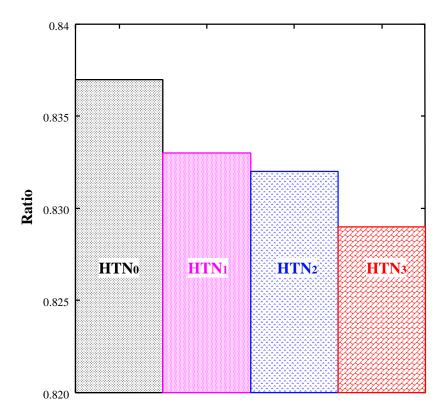

| 3.21   | Normalized layout area                                                        | 63  |

| 3.22   | 2D-planner realization of 3D-torus network                                    | 65  |

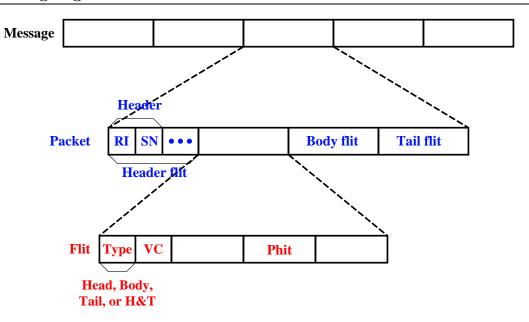

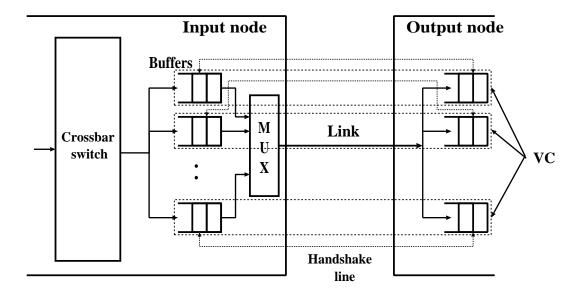

| 4.1    | Units of resource allocation                                                  | 70  |

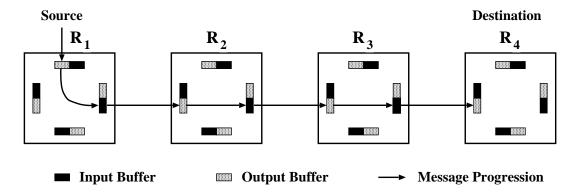

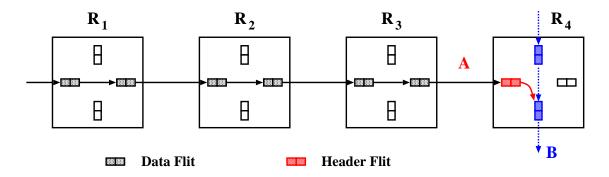

| 4.2    | Wormhole routing                                                              | 72  |

| 4.3    | An example of the blocked wormhole-routed message                             | 72  |

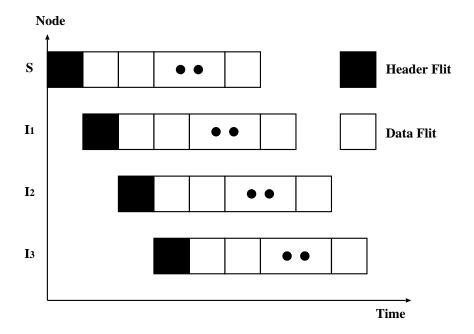

| 4.4    | Time-space diagram of a wormhole-routed message                               | 72  |

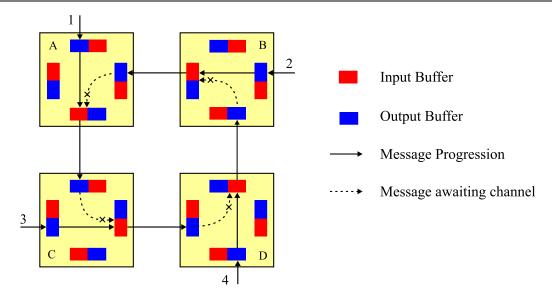

| 4.5    | An example of deadlock involving four packets                                 | 74  |

| 4.6    | Virtual channel                                                               | 76  |

| 4.7    | Message blocking while physical channels remain idle                          | 76  |

| 4.8    | Virtual channel allows to pass blocked message                                | 76  |

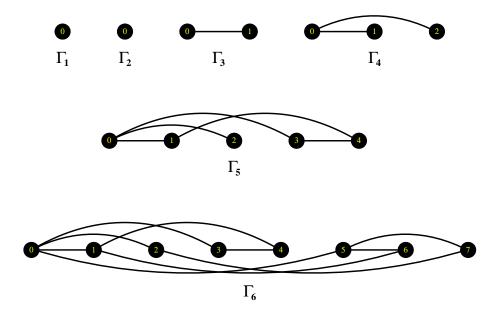

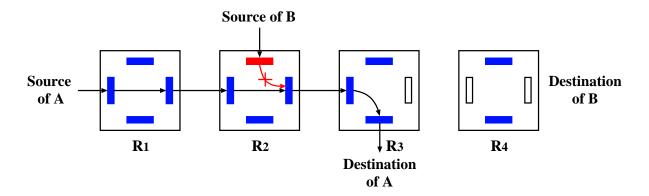

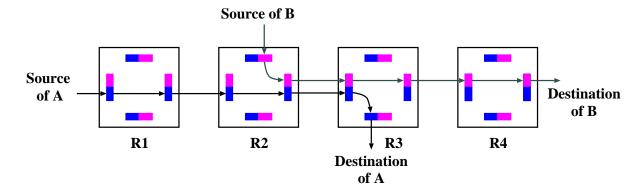

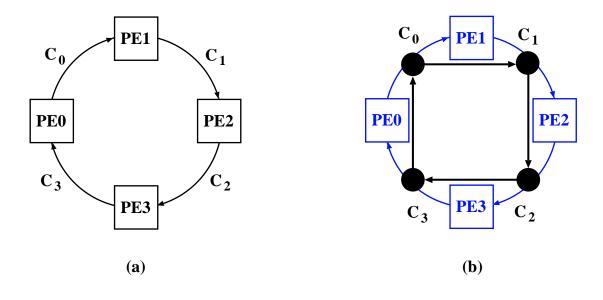

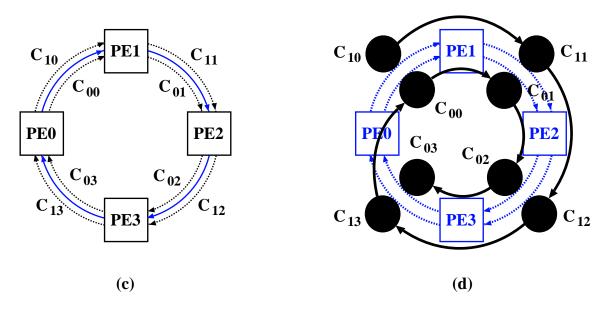

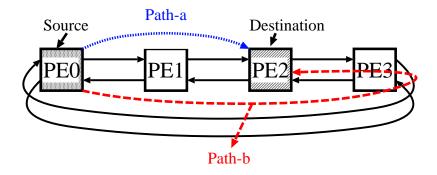

| 4.9    | (a) A ring network with unidirectional channels. (b) The associated channel   |     |

|        | dependency graph contains a cycle. (c) Each physical channel is logically     |     |

|        | split into two virtual channels. (d) A modified channel dependency graph      |     |

|        | without cycles.                                                               | 79  |

|        | Deadlock configuration in mesh network                                        | 80  |

|        | Deadlock configuration in torus network                                       | 81  |

| 4.12   | A set of routing paths created by the dimension order routing in a 2D-mesh    |     |

|        | network                                                                       | 82  |

|        | Dimension-order routing algorithm for HTN                                     | 85  |

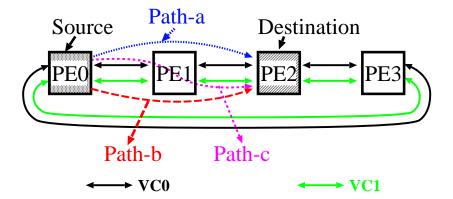

|        | An example of message routing in HTN                                          | 86  |

| 4.15   | Nonuniform traffic patterns on a $8 \times 8$ mesh networks: (a) dimension-   | 0.0 |

| 4 1 0  | reversal traffic and (b) bit-reversal traffic                                 | 92  |

| 4.16   | Dynamic communication performance of dimension-order routing with uni-        |     |

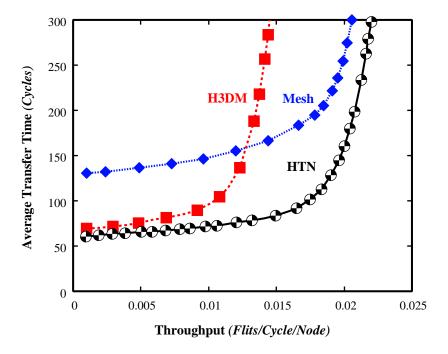

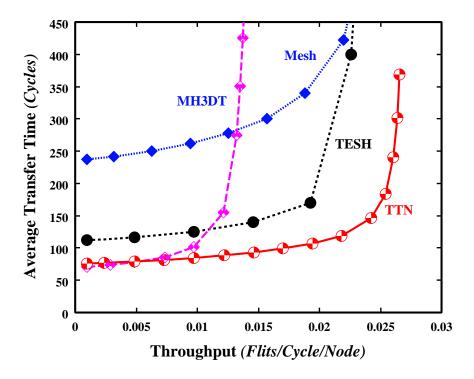

|        | form traffic pattern on various networks: 1024 nodes, different virtual chan- | 05  |

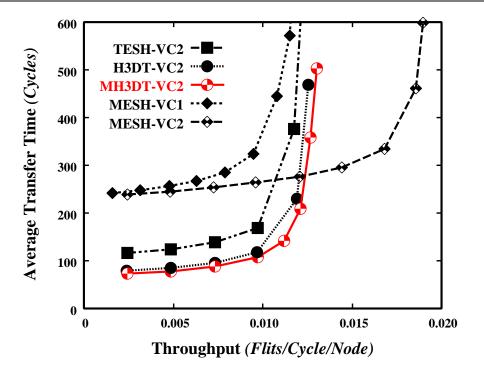

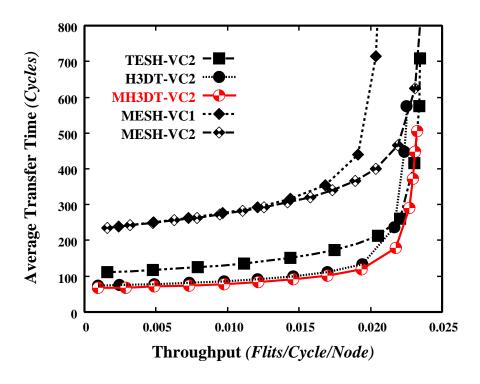

| 1 1 17 | nels, short message, and $q = 0$                                              | 95  |

| 4.17   | Dynamic communication performance of dimension-order routing with uni-        |     |

|        | form traffic pattern on various networks: 1024 nodes, 3 virtual channels,     | 05  |

|        | short message, and $q = 0$                                                    | 95  |

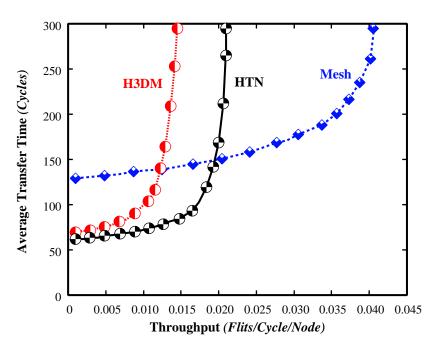

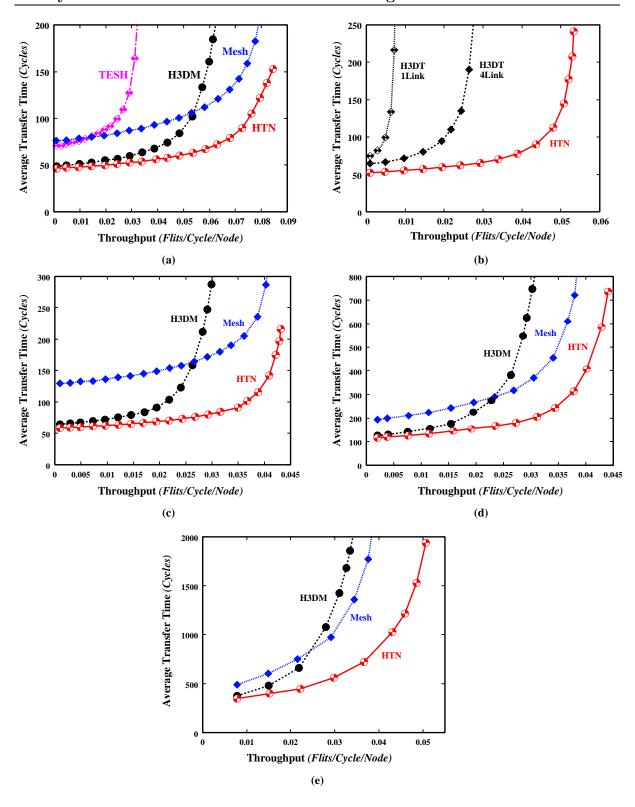

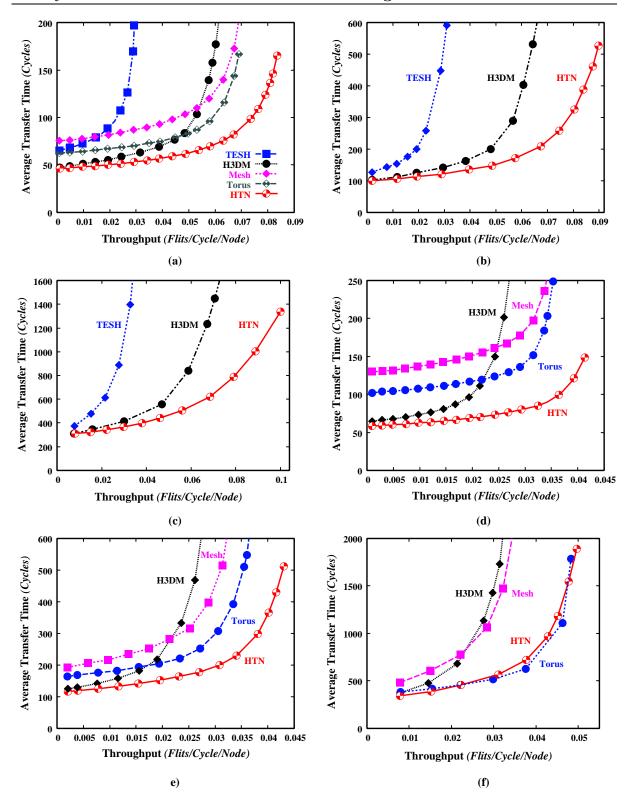

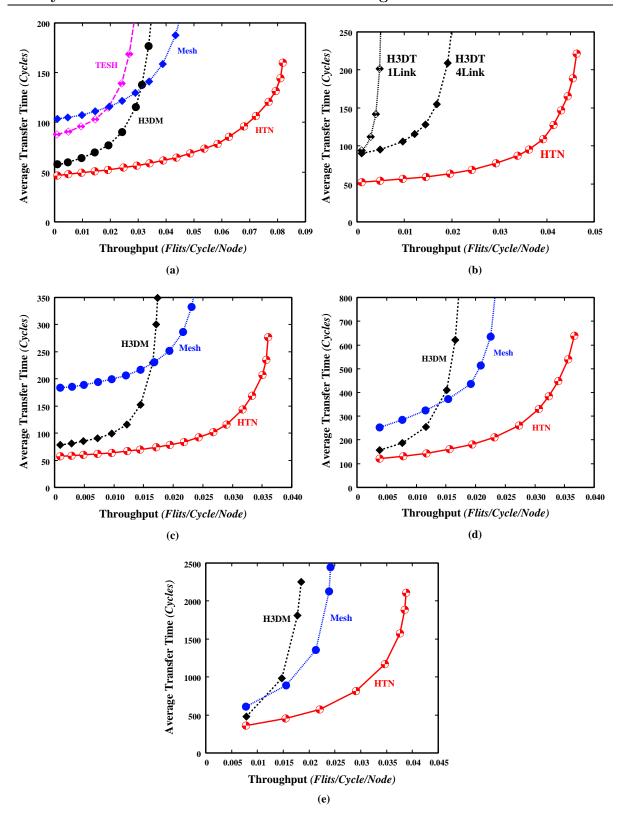

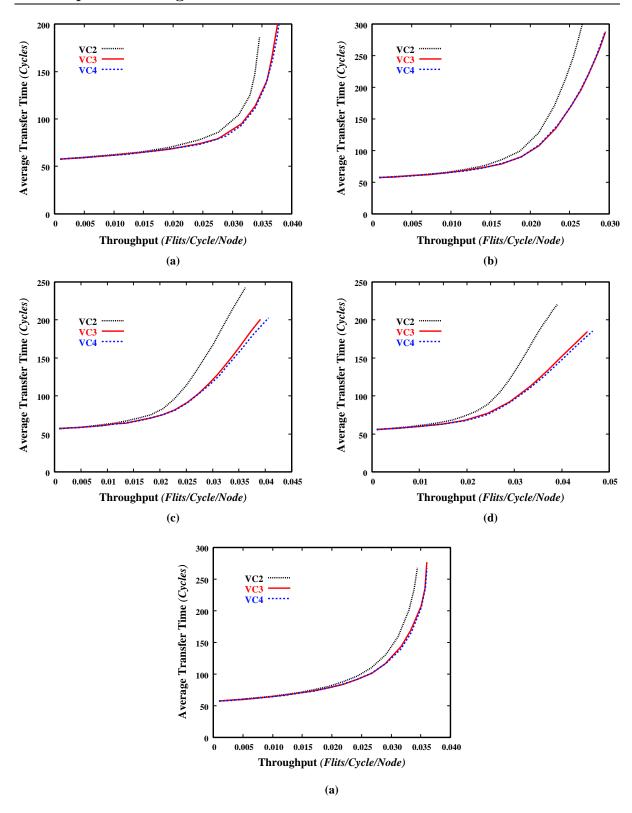

| 4.18 | Dynamic communication performance of dimension-order routing with uniform traffic pattern on various networks: (a) 256 nodes, 3 virtual channels,               |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | short message, and $q=1$ (b) 512 nodes, 3 virtual channels, short message,                                                                                      |     |

|      | and $q = 1$ , (c) 1024 nodes, 3 virtual channels, short message, and $q = 1$ ,                                                                                  |     |

|      | (d) 1024 nodes, 3 virtual channels, medium-length message, and $q = 1$ , (e) 1024 nodes, 3 virtual channels, long message, and $q = 1, \dots, \dots$            | 97  |

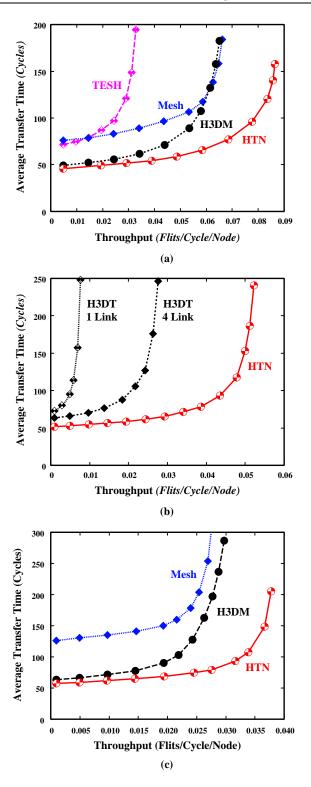

| 4.19 |                                                                                                                                                                 | 91  |

| 1.10 | form traffic pattern on various networks: (a) 256 nodes, 2 virtual channels,                                                                                    |     |

|      | short message, and $q = 1$ (b) 256 nodes, 2 virtual channels, medium-length                                                                                     |     |

|      | message, and $q = 1$ , (c) 256 nodes, 2 virtual channels, long message, and                                                                                     |     |

|      | q=1, (d) 1024 nodes, 2 virtual channels, short message, and $q=1$ , (e)                                                                                         |     |

|      | 1024 nodes, 2 virtual channels, medium-length message, and $q = 1$ , and (f)                                                                                    | 0.0 |

| 4.90 | 1024 nodes, 2 virtual channels, long message, and $q = 1, \dots, \dots$                                                                                         | 98  |

| 4.20 | Dynamic communication performance of dimension-order routing with hot-<br>spot traffic pattern on various networks: (a) 256 nodes, 3 virtual channels,          |     |

|      | 5% hot-spot traffic, short message, and $q = 1$ (b) 512 nodes, 3 virtual                                                                                        |     |

|      | channels, 5% hot-spot traffic, short message, and $q=1$ , and (c) 1024                                                                                          |     |

|      | nodes, 3 virtual channels, 5% hot-spot traffic, short message, and $q=1$ .                                                                                      | 100 |

| 4.21 | Dynamic communication performance of dimension-order routing with hot-                                                                                          |     |

|      | spot traffic pattern on various networks: (a) 256 nodes, 3 virtual channels,                                                                                    |     |

|      | 2% hot-spot traffic, short message, and $q=1$ (b) 256 nodes, 3 virtual channels, $10%$ hot-spot traffic, short message, and $q=1$ , (c) 1024 nodes,             |     |

|      | 3 virtual channels, 2% hot-spot traffic, short message, and $q=1$ , (c) 1024 hodes,                                                                             |     |

|      | 1024 nodes, 3 virtual channels, 10% hot-spot traffic, short message, and                                                                                        |     |

|      |                                                                                                                                                                 | 101 |

| 4.22 | Dynamic communication performance of dimension-order routing with di-                                                                                           |     |

|      | mension reversal traffic pattern on various networks: (a) 256 nodes, 3 vir-                                                                                     |     |

|      | tual channels, 2-dimensional reversal traffic, short message, and $q = 1$ (b)                                                                                   |     |

|      | 1024 node, 3 virtual channels, 2-dimensional reversal traffic, short message, ands $q = 1$ , (c) 256 nodes, 3 virtual channels, 3-dimensional reversal traffic, |     |

|      | short message, and $q = 1$ , (d) 1024 nodes, 3 virtual channels, 3-dimensional                                                                                  |     |

|      | reversal traffic, short message, and $q = 1, \ldots, \ldots$                                                                                                    | 103 |

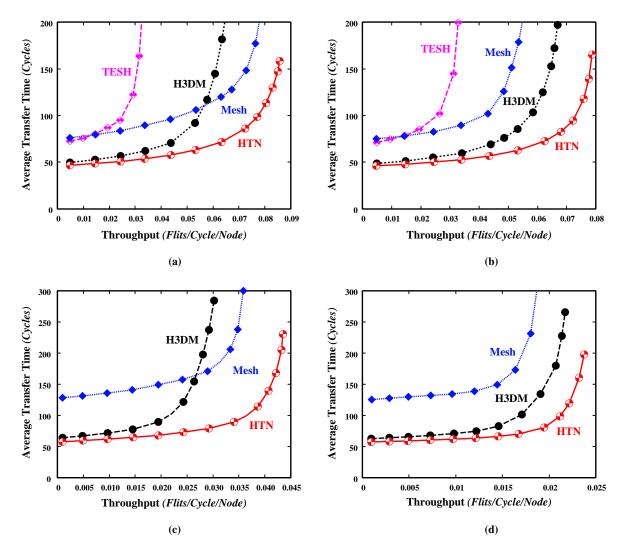

| 4.23 | Dynamic communication performance of dimension-order routing with bit-                                                                                          |     |

|      | reversal traffic pattern on various networks: (a) 256 nodes, 3 virtual chan-                                                                                    |     |

|      | nels, short message, and $q=1$ (b) 512 nodes, 3 virtual channels, short message, and $q=1$ , (c) 1024 nodes, 3 virtual channels, short message, and             |     |

|      | message, and $q = 1$ , (c) 1024 nodes, 3 virtual channels, short message, and $q = 1$ , (d) 1024 nodes, 3 virtual channels, medium-length message, and          |     |

|      | q = 1, and (e) 1024 nodes, 3 virtual channels, long message, and $q = 1$ .                                                                                      | 105 |

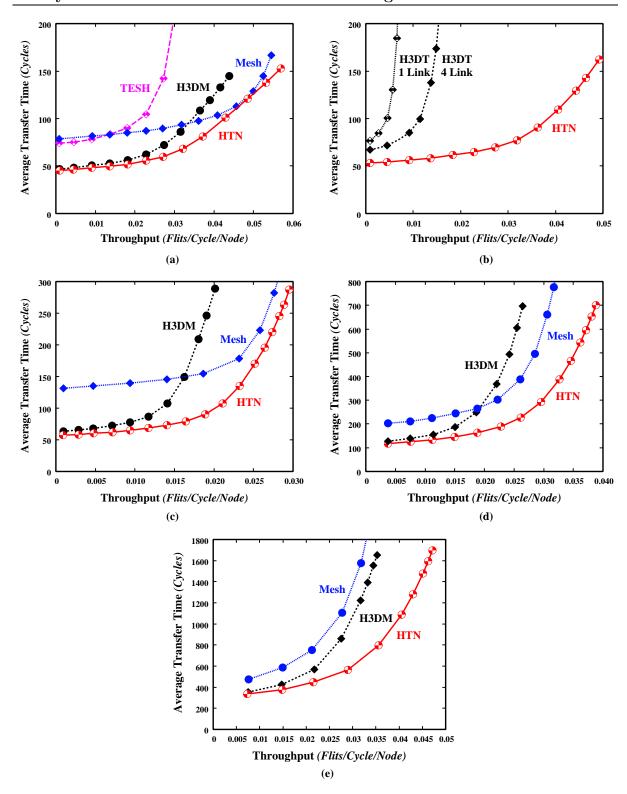

| 4.24 | Dynamic communication performance of dimension-order routing with com-                                                                                          |     |

|      | plement traffic pattern on various networks: (a) 256 nodes, 3 virtual chan-                                                                                     |     |

|      | nels, short message, and $q = 1$ , (b) 512 nodes, 3 virtual channels, short                                                                                     |     |

|      | message, and $q = 1$ , (c) 1024 nodes, 3 virtual channels, short message,                                                                                       |     |

|      | and $q = 1$ (d) 1024 nodes, 3 virtual channels, medium-length message, and $q = 1$ , and (e) 1024 nodes, 3 virtual channels, long message, and $q = 1$ .        | 106 |

|      | $q-1$ , and $(c)$ 1024 nodes, $\sigma$ virtual chamnels, long message, and $q-1$ .                                                                              | 100 |

| 4.25 | Dynamic communication performance of dimension-order routing with bit-<br>flip traffic pattern on various networks: (a) 256 nodes, 2 virtual channels, |      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | short message, and $q = 1$ and (b) 1024 nodes, 2 virtual channels, short                                                                               |      |

|      | message, and $q = 1, \ldots, \ldots$                                                                                                                   | 108  |

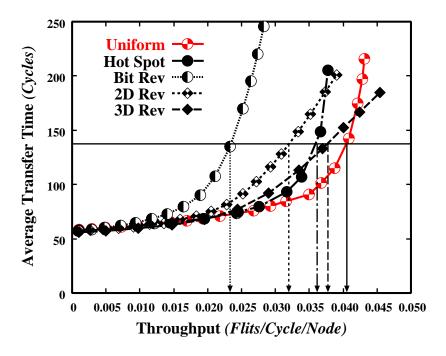

| 4.26 | Dynamic communication performance of large-size HTN by dimension-                                                                                      |      |

|      | order routing under various traffic patterns: 3 virtual channels, short message                                                                        | .109 |

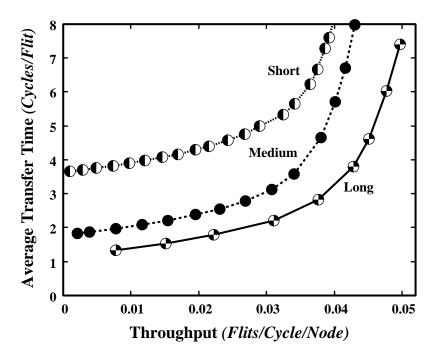

| 4.27 |                                                                                                                                                        | 0 0  |

|      | put of HTN: 1024 nodes, 2 VCs, and $q = 1$                                                                                                             | 110  |

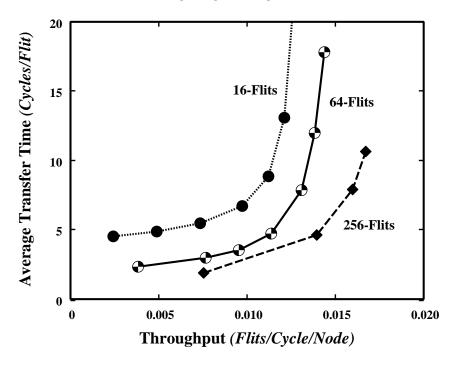

| 4.28 | Dynamic communication performance of dimension-order routing with dif-                                                                                 |      |

|      | ferent virtual channels and short message on the large-size HTN: (a) hot                                                                               |      |

|      | spot traffic, (b) bit reversal traffic, (c) 2-dimension reversal, (d) 3-dimension                                                                      |      |

|      | reversal, and (e) complement traffic patterns                                                                                                          | 112  |

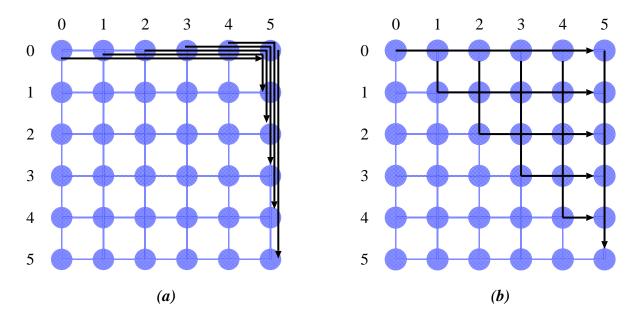

| 4.29 | Routing messages in an 6x6 mesh from node $(0, i)$ to node $(i, 5)$ (for $0 \le i$                                                                     |      |

|      | $i \leq 5$ ; (a) Using dimension order routing, five messages must traverse                                                                            |      |

|      | the channel from $(0,4)$ to $(0,5)$ , (b) Using adaptive routing, all messages                                                                         |      |

|      | proceed simultaneously                                                                                                                                 | 113  |

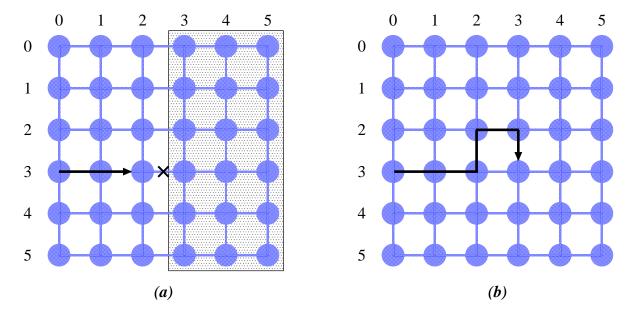

| 4.30 | A $6 \times 6$ mesh with a faulty link from node $(3,2)$ to node $(3,3)$ . (a) With                                                                    |      |

|      | dimension order routing messages from dark nodes to the shaded area can-                                                                               |      |

|      | not be delivered. (b) With adaptive routing, messages can be delivered                                                                                 |      |

|      | between all pairs of nodes                                                                                                                             | 113  |

|      | Selection of physical link by link-selection algorithm                                                                                                 |      |

|      | Link-selection algorithm for HTN                                                                                                                       |      |

|      | Selection of virtual channels by channel-selection algorithm                                                                                           |      |

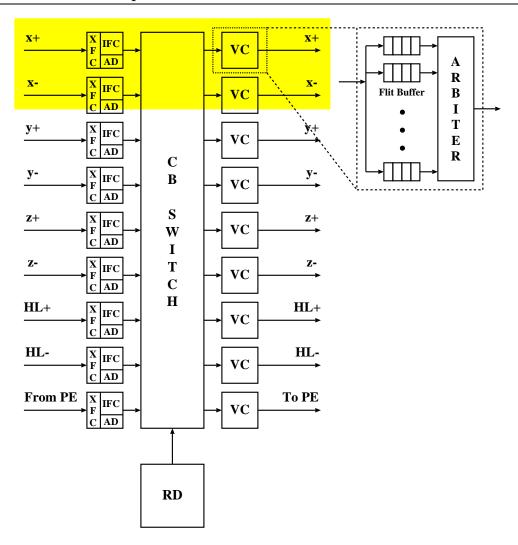

|      | A block diagram of router architecture                                                                                                                 | 121  |

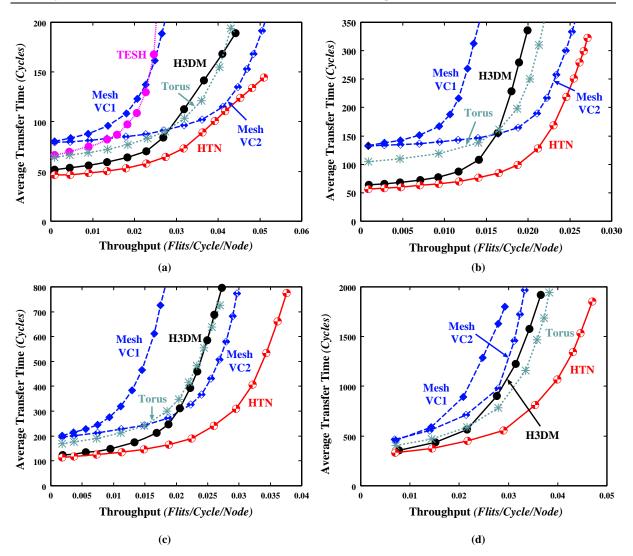

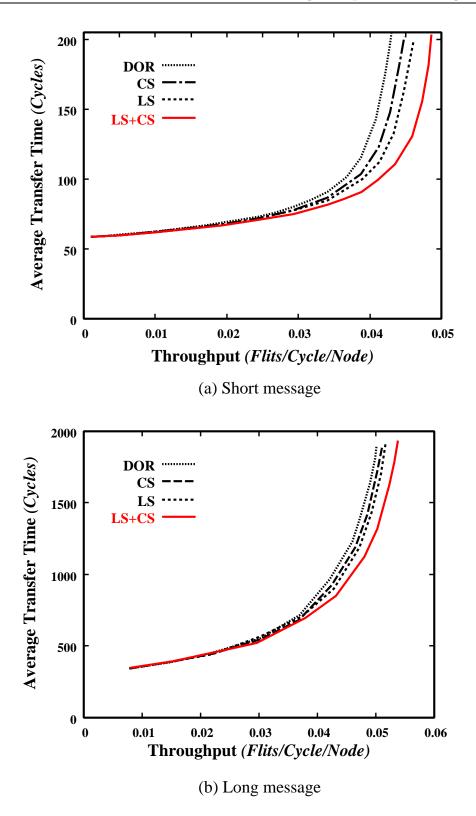

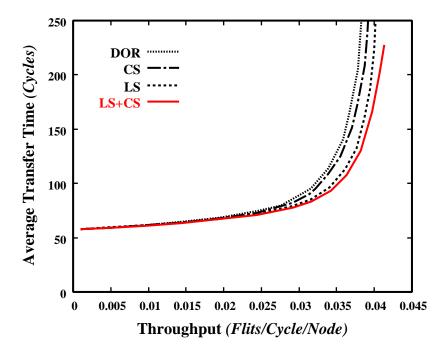

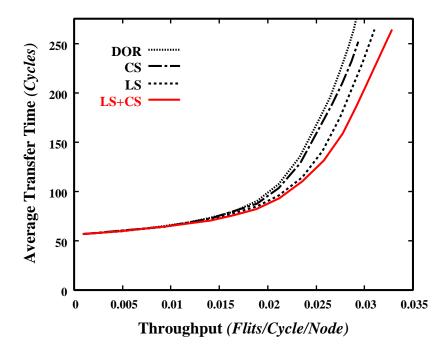

| 4.35 | Comparison of dynamic communication performance of the HTN between                                                                                     |      |

|      | DOR, LS, CS, and LS+CS algorithms with uniform traffic pattern: 1024                                                                                   | 105  |

| 1.00 | nodes, 3 virtual channels, and $q = 1, \dots, \dots, \dots$                                                                                            | 127  |

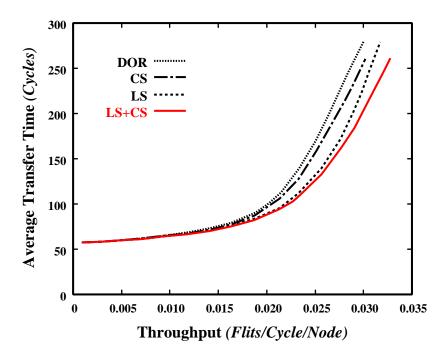

| 4.30 | Comparison of dynamic communication performance of the HTN between                                                                                     |      |

|      | DOR, LS, CS, and LS+CS algorithms with 5% hot-spot traffic pattern:                                                                                    | 100  |

| 4.27 | 1024 nodes, 3 virtual channels, short message, and $q = 1, \dots, \dots$                                                                               | 128  |

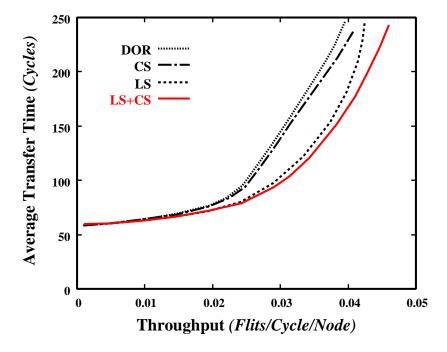

| 4.57 | Comparison of dynamic communication performance of the HTN between                                                                                     |      |

|      | DOR, LS, CS, and LS+CS algorithms with bit-reversal traffic pattern: 1024 nodes, 3 virtual channels, 16 flits, and $q = 1. \dots \dots \dots \dots$    | 198  |

| 1 38 | Comparison of dynamic communication performance of the HTN between                                                                                     | 120  |

| 4.00 | DOR, LS, CS, and LS+CS algorithms with bit-flip traffic pattern: 1024                                                                                  |      |

|      | nodes, 3 virtual channels, short message, and $q = 1, \ldots, n$                                                                                       | 120  |

| 4 39 | Comparison of dynamic communication performance of the HTN between                                                                                     | 120  |

| 1.00 | DOR, LS, CS, and LS+CS algorithms with perfect shuffle traffic pattern:                                                                                |      |

|      | 1024 nodes, 3 virtual channels, short message, and $q = 1$                                                                                             | 129  |

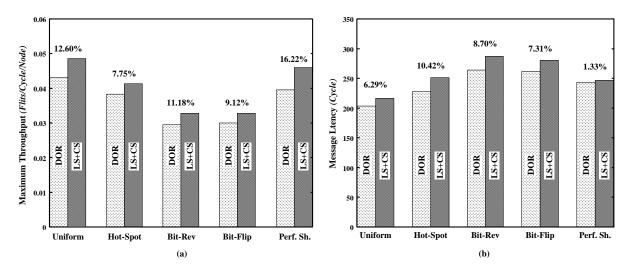

| 4.40 | Dynamic communication performance improvement by LS+CS algorithm                                                                                       | 1-0  |

| 1.10 | over DOR algorithm (a) Maximum throughput enhancement and (b) Mes-                                                                                     |      |

|      | sage latency reduction                                                                                                                                 | 130  |

| 5.1  | Hierarchical redundancy of the HTN                                                                                                                     |      |

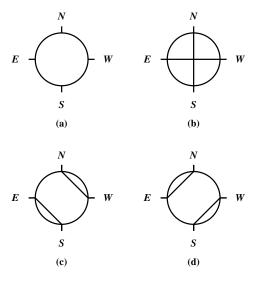

| 5.2  | Different switch states for reconfiguration: (a) no connect, (b) north-to-                                                                             |      |

|      | south and east-to-west, (c) north-to-west and south-to-east, and (d) north-                                                                            |      |

|      | to-east and south-to-west connects                                                                                                                     | 134  |

|      |                                                                                                                                                        |      |

| 5.5  | Diagonal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 134   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

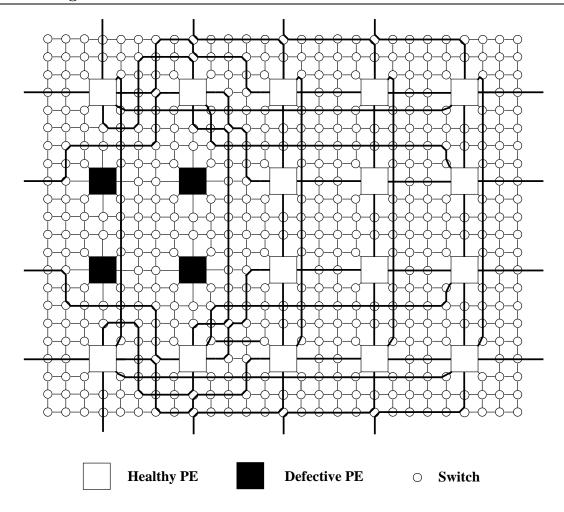

| 5.4  | Reconfiguration of a plane for the BM in the presence of 4 faulty PEs: Square                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

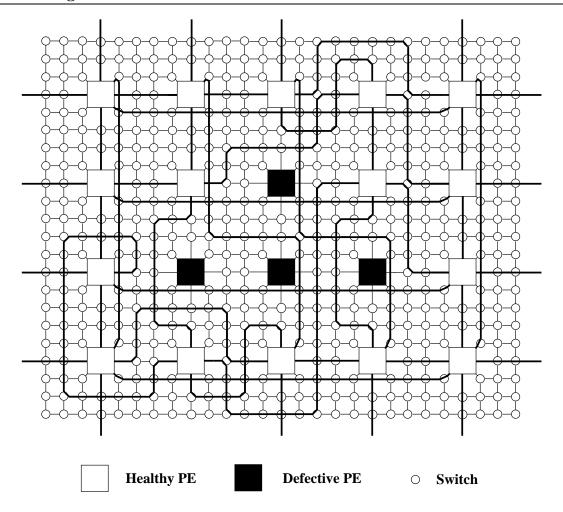

| 5.5  | Reconfiguration of a plane for the BM in the presence of 4 faulty PEs:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 100   |

| 0.0  | Concatenated L-shape and inverse L-shape                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 136   |

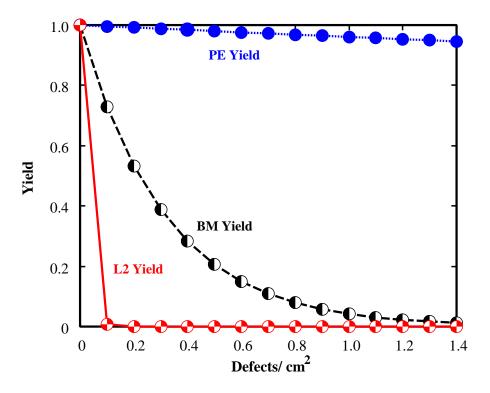

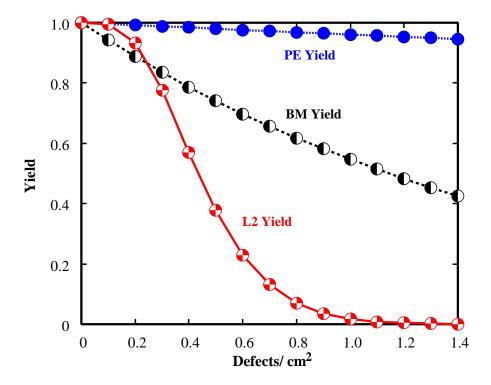

| 5.6  | Yield for BM and Level-2 network vs. fault density without spare node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| 5.7  | Yield for BM and Level-2 network vs. fault density without spare node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

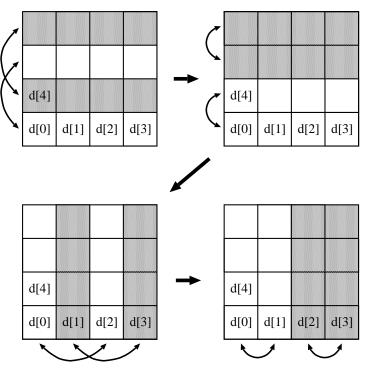

| 5.8  | CONVERGE on a 4 × 4 2D-mesh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

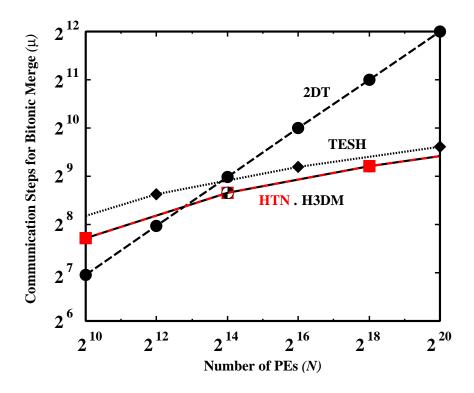

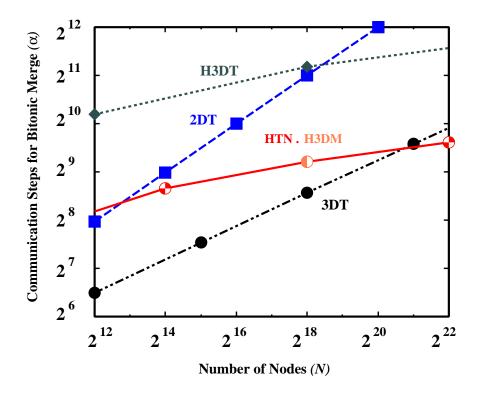

| 5.9  | The total number of communication steps of the bitonic merge in different networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| 5 10 | The total number of communication steps of the bitonic merge in different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 140   |

| 0.10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 146   |

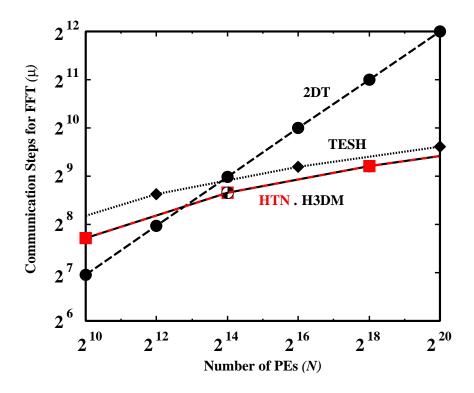

| 5.11 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

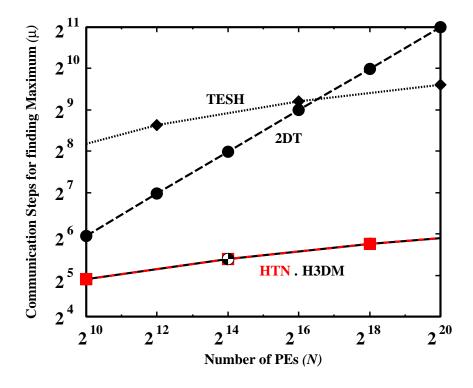

| -    | The total number of communication steps for finding the maximum in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

|      | different networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 147   |

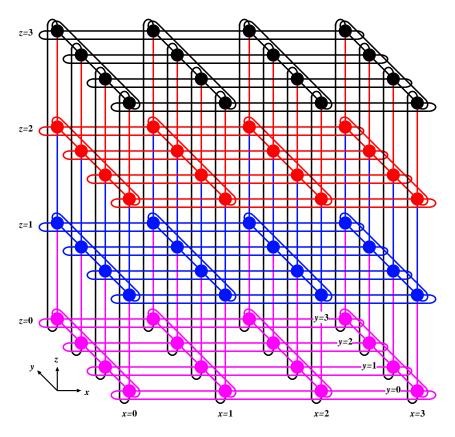

| 6.1  | A $(4 \times 4 \times 4)$ torus network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| 6.2  | A $(4 \times 4 \times 4)$ pruned torus obtained by pruning along the z direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| 6.3  | A $(4 \times 4 \times 4)$ pruned torus obtained by pruning along the $x + y + z$ direction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |